可以使用許多工具來優化PLL環路。 ADIsimCLK是用于ADI時鐘部件的好工具。優化相位噪聲和抖動不一定是一回事。

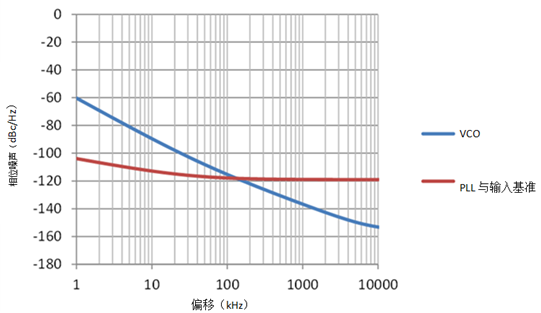

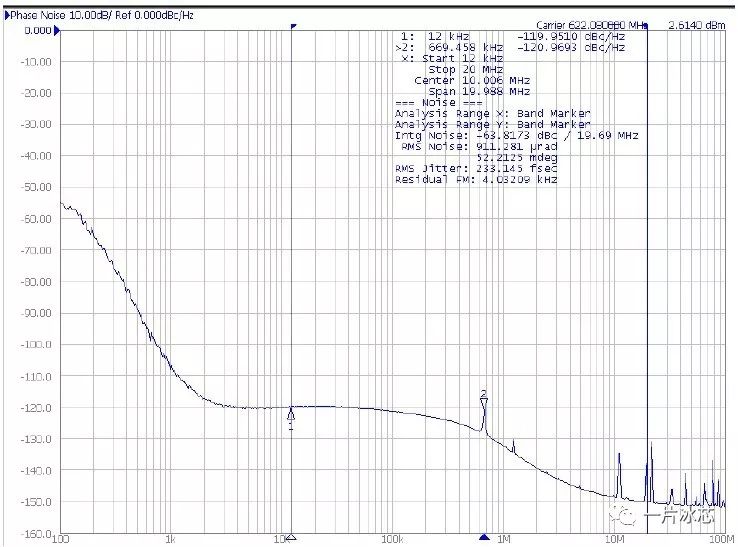

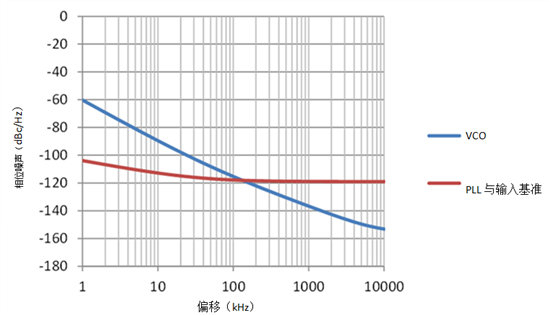

如果在給定的偏移頻率下有一個相位噪聲規范,那么應該將VCO和參考相位噪聲信息提供給工具,例如ADIsimCLK,并使用它來優化閉環帶寬實現預期目標。該過程實質上是調整閉環帶寬以折衷參考和VCO相位噪聲。

如果有一個具有抖動規格,則應調整閉環帶寬以實現最低抖動,這可能不一定對應于所有偏移頻率的最低相位噪聲。

例如,雖然可以通過擴展閉環帶寬來實現低近距相位噪聲,但由此產生的抖動可能大于可能的最小抖動,因為環路跟蹤參考的次數超過了是最佳抖動所必需的。可以通過降低閉環帶寬來實現更低的抖動,允許PLL在較低的偏移頻率下跟蹤VCO,即使得到的相位噪聲圖可能在閉環帶寬偏移頻率處顯示更多的峰值。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

pll

+關注

關注

6文章

776瀏覽量

135131 -

抖動

+關注

關注

1文章

69瀏覽量

18860 -

相位噪聲

+關注

關注

2文章

180瀏覽量

22860

發布評論請先 登錄

相關推薦

如何選擇環路帶寬平衡抖動、相位噪聲、鎖定時間或雜散

作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路

發表于 07-18 14:24

?1.1w次閱讀

選擇環路帶寬涉及抖動、相位噪聲、鎖定時間或雜散問題

做的仍是尋找最優環路帶寬。圖1中,鎖相環(PLL)與壓控振蕩器(VCO)噪聲交叉處的偏移,BWJIT(約為140kHz)通過減少曲線下方的面積來優化

發表于 08-29 16:02

雙環路時鐘發生器可清除抖動并提供多個高頻輸出

帶寬器件(用于清除抖動),其后是一個環 路帶寬較寬的高頻器件。有些現代雙環路模擬 PLL 集成于單個芯片之上,允許設計師 減少低頻參考抖動,同時還能提供高頻、低

發表于 10-31 08:00

發現抖動、相位噪聲、鎖定時間或雜散問題怎么解決

圖1中,鎖相環(PLL)與壓控振蕩器(VCO)噪聲交叉處的偏移,BWJIT(約為140kHz)通過減少曲線下方的面積來優化抖動。 圖1:最優

發表于 11-16 07:56

時鐘抖動(CLK)和相位噪聲之間的轉換

摘要:這是一篇關于時鐘(CLK)信號質量的應用筆記,介紹如何測量抖動和相位噪聲,包括周期抖動、逐周期抖動和累加

發表于 04-22 10:16

?4293次閱讀

鎖相環PLL的噪聲分析與優化 鎖相環PLL與相位噪聲的關系

鎖相環(PLL)是一種反饋控制系統,它通過比較輸入信號和輸出信號的相位差異,調整輸出信號以實現相位鎖定。在許多應用中,如無線通信、頻率合成和時鐘同步,PLL的性能直接關系到系統的整體性

怎樣優化PLL環路來達到理想的相位噪聲和抖動

怎樣優化PLL環路來達到理想的相位噪聲和抖動

評論