是的。當時鐘輸入信號穿過輸入級的開關區域時,輸入級中的隨機噪聲在信號傳遞到后續級時增加了信號的時間抖動。更快地穿過該開關區域(具有更高的壓擺率)的信號受隨機噪聲的影響較小,導致較少的附加時間抖動和較低的時鐘輸出抖動。對于相同幅度的信號,較高頻率信號具有較高(較快)的轉換速率,因此可以通過時鐘分配系統導致較低的時間抖動。

時鐘頻率的輸入中添加的任何抖動都不能通過隨后的時鐘頻率劃分來降低(相位噪聲會隨著分頻而降低,但不會降低抖動)。因此,應在輸入端盡可能減少抖動。

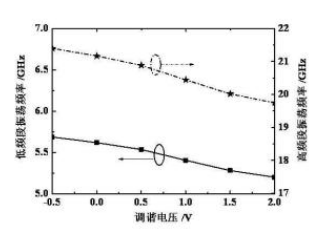

這意味著原則上運行VCO的頻率高于時鐘輸出所需的頻率。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

頻率

+關注

關注

4文章

1507瀏覽量

59263 -

VCO

+關注

關注

13文章

190瀏覽量

69221 -

輸入信號

+關注

關注

0文章

458瀏覽量

12579

發布評論請先 登錄

相關推薦

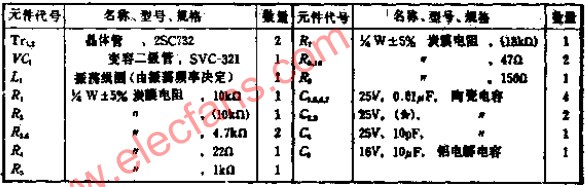

微型高穩定的鎖相頻率源電路設計

合成一般通過混頻、倍頻、分頻、濾波等方式進行頻率變換和組合,從而產生大量離散的穩定頻率信號。這不僅使頻率合成器具有龐大的體積和重量,其輸出信號中的諧波、噪聲及寄生

發表于 07-09 08:12

如何用交叉耦合電流饑餓型VCO設計實現降低時鐘頻率的相位噪聲?

本文設計了一個適用于以太網物理層芯片時鐘同步PLL的高寬帶低噪聲VCO,采用了具有良好抗噪能力的交叉耦合電流饑餓型差分環形振蕩器。仿真結果表明,在同樣輸入噪聲和環境噪聲的情況下,本文的VC

發表于 02-25 07:39

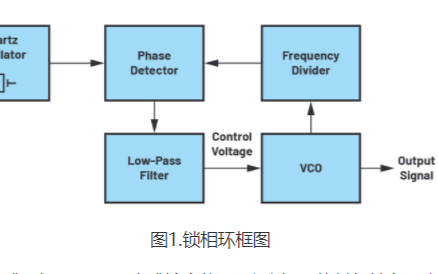

如何鎖住相位使VCO的頻率等于參考信號的頻率呢?

鑒頻鑒相器,當兩輸入信號頻率相同但相位不同的時候,有電壓差輸出,然后去控制VCO,改變反饋信號頻率。這不是導致兩輸入頻率不同了,這如何鎖住相位啊,使

發表于 04-24 10:23

變頻器的頻率為何調不上去?

對于一個變頻器來說都有頻率范圍的設定,如參數最大輸出頻率和運行頻率上限,最大輸出頻率根據變頻器的結構來確定可根據手冊進行查詢比如0~400.00Hz,

發表于 01-10 09:20

?2.8w次閱讀

驅動高壓鎖相環頻率合成器電路中的VCO詳細分析

鎖相環(PLL)電路是由壓控振蕩器(VCO)和鑒相器組成的反饋系統,振蕩器信號跟蹤施加的頻率或相位調制信號是否具有正確的頻率和相位。需要從固定低頻率

發表于 11-25 09:23

?18次下載

驅動高壓鎖相環頻率合成器電路的VCO

鎖相環(PLL)電路是由壓控振蕩器(VCO)和鑒相器組成的反饋系統,振蕩器信號跟蹤施加的頻率或相位調制信號是否具有正確的頻率和相位。需要從固定低頻率

VCO的頻率穩定性是什么

VCO(Voltage-Controlled Oscillator,壓控振蕩器)的頻率穩定性是一個關鍵的性能指標,它描述了VCO輸出頻率對輸入電壓變化的敏感程度及在長時間或不同環境條件

VCO頻率的運行頻率高,具有什么優勢?

VCO頻率的運行頻率高,具有什么優勢?

評論