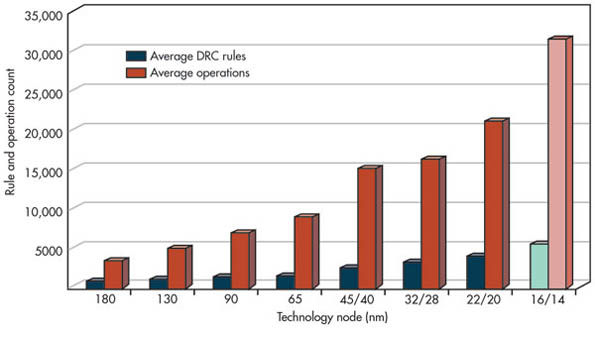

如果只是科普/大流程的話, 從199X年硅片的制作流程就沒怎么變過, 唯一對芯片設(shè)計(jì)造成比較大的影響的是隨著MOS管變小增加的Design Rule

我來簡單的說一下模擬電路和數(shù)字電路設(shè)計(jì)/制作方面的差別吧:首先明確一點(diǎn): 所有的ASIC(Application-Specific Integrated Circuit), 也即應(yīng)用芯片, 都是有一個(gè)Design的目的, 如果是在工廠里就是乙方提的要求; 在PhD生涯里就是老板布置的活...要成功通關(guān), 待我細(xì)細(xì)道來:

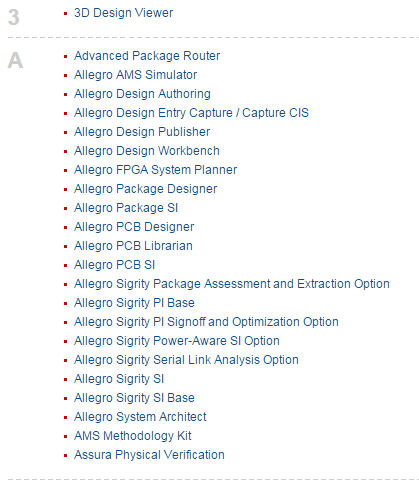

小怪. 數(shù)字電路電路圖推薦武器:

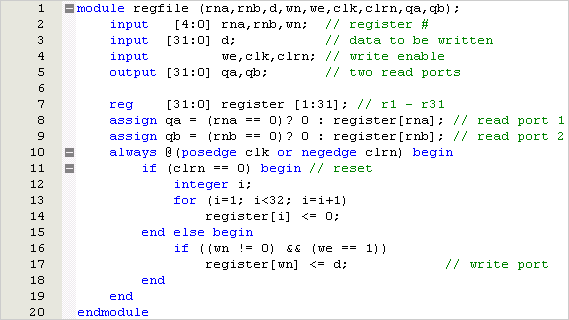

Verilog數(shù)字電路一般用Verilog寫, 主要是因?yàn)榉奖?我才不告訴你我手動(dòng)壘Standard Cell呢) . 比如說CPU級別的芯片, 動(dòng)輒上億的MOS管, 就算一秒畫一個(gè), 不計(jì)連線時(shí)間, 你得畫38個(gè)月.

小怪: 數(shù)字電路仿真推薦武器:

VCS, MMSIM寫完了Verilog, 就要跑數(shù)字仿真了. 一般會(huì)用到Synopsys 的VCS或者Mentor Graphics的MMSIM之類的.這個(gè)仿真非常快, 因?yàn)槊恳粋€(gè)MOS管都被看成是開關(guān), 然后加上一些非常粗糙的模擬出來的延遲時(shí)間. 目的是看你寫出來的玩意能不能正常工作.

小怪. 模擬電路電路圖推薦武器:

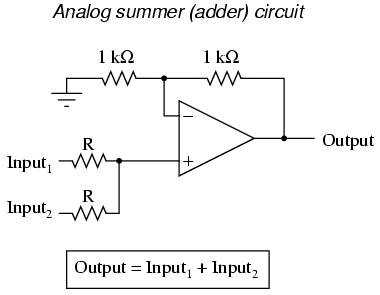

Cadence (允許準(zhǔn)確擊打), SPICE(自由度高, 可長可短)等這個(gè)就比較復(fù)雜了. 因?yàn)槟M電路的自由度非常高! 比方說, 一個(gè)MOS管在數(shù)字電路條件下就是一個(gè)開關(guān), 但是在模擬電路里面, 根據(jù)柵極電壓和電路結(jié)構(gòu)不一樣, 分分鐘完成 開路-大電阻-放大器-電流源-導(dǎo)通各種功能.所以呢, 模擬電路基本就得手畫了.

小怪.模擬電路仿真推薦武器:

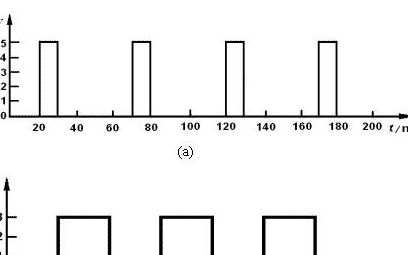

Spectre(精度最高), HSPICE, PSpice, HFSS等最好跟打小怪.模擬電路電路圖小怪用一樣的武器.模擬電路的仿真包括但不限于: 調(diào)節(jié)分壓, 仿真, 模擬工作點(diǎn)等... 而且千萬記住! 設(shè)計(jì)過程中, 精細(xì)(Swing <= 100 mV)的模擬電路要做噪聲分析! 不然各種地方的噪音分分鐘教你做人...好, 現(xiàn)在假設(shè)我們有電路圖啦~數(shù)字電路的電路圖長這樣:

模擬電路的電路圖長這樣:

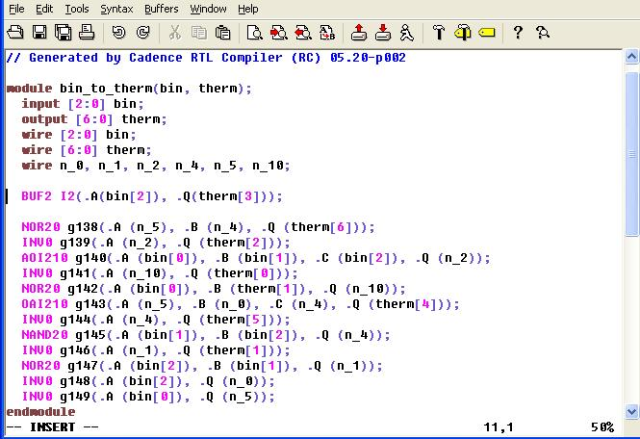

下一步, 就是要把這些東西變成實(shí)實(shí)在在的電路:小Boss.綜合電路:推薦武器: Design Compiler (DC)數(shù)字電路需要用到Design Compiler, Synopsys公司出的大殺器, 一招把Verilog轉(zhuǎn)成Verilog !這一步叫做Synthesis (綜合).綜合出來的電路也是Verilog格式, 但是長這樣:

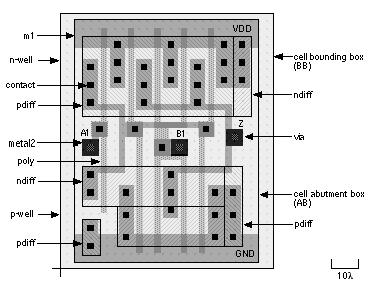

把一堆描述性質(zhì)的語言轉(zhuǎn)換成真正的Standard Cell (標(biāo)準(zhǔn)門電路)Standard Cell長這樣:

小Boss.模擬電路Layout

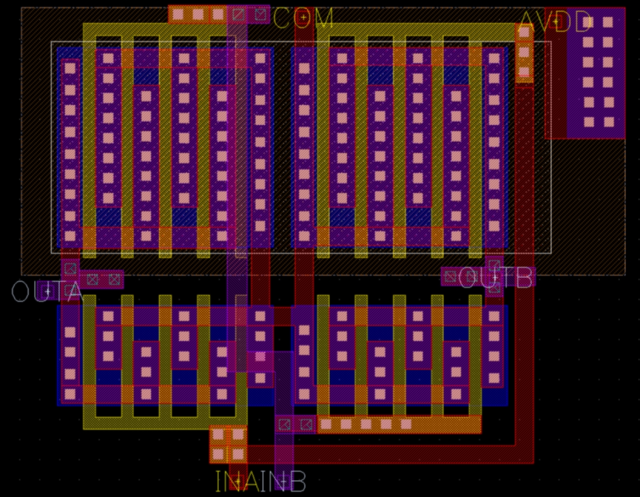

必殺: 無. 但是血厚.推薦武器: Cadence Layout Editor等.模擬電路就比較煩了, 一般會(huì)手畫, 大概長這樣:

。。這一個(gè)是比較規(guī)整的Design, 來個(gè)不規(guī)整的:

師兄有云: 畫模擬電路的Layout是體力活.

我表示師兄說的太對了!小Boss.數(shù)字電路Layout必殺: 向門神告狀(DRC/LVS Fail).推薦武器: IC-compiler, Encounter

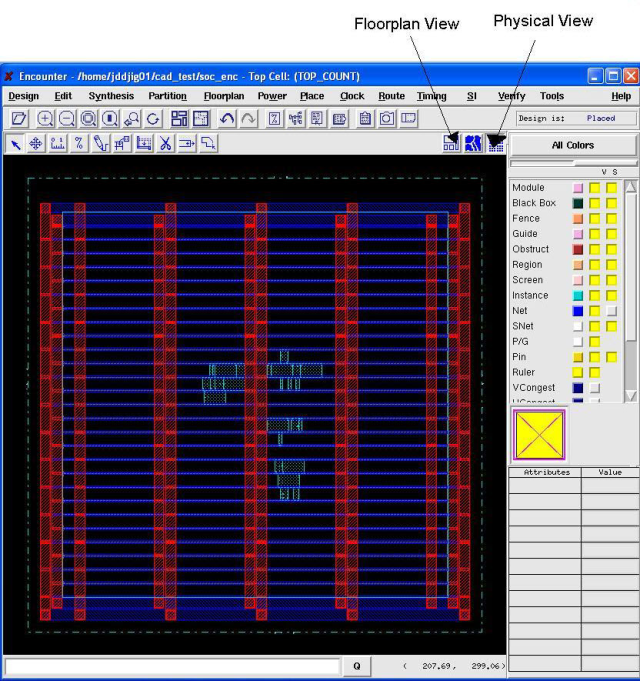

數(shù)字電路接下來就需要Place and Route (布線)了. 一般這個(gè)步驟由IC-Compiler / Encounter 等工具來完成. 具體就是, 把綜合過的Verilog 中的每個(gè)Standard Cell找到對應(yīng)的Standard Cell Layout, 布置在用戶指定的范圍內(nèi), 然后自動(dòng)連線.這個(gè)自動(dòng)連線就很講究:自動(dòng)布線要先連時(shí)鐘信號, 然后連電源網(wǎng)絡(luò), 最后連其他的數(shù)字信號等.時(shí)鐘信號默認(rèn)會(huì)使用雙倍線寬, 如有分支, 盡量使用對稱的結(jié)構(gòu);然后使用用戶的方式架設(shè)電源網(wǎng)絡(luò). 為什么叫電源網(wǎng)絡(luò)呢? 因?yàn)橐话闫系碾娫撮L這樣:

power net 這名字不是白起的...自動(dòng)布線就不展開講了... 學(xué)問太多了(主要是制作工藝...)之后, 還有一個(gè)很重要的步驟:Filler Cell什么意思呢?數(shù)字電路的Standard Cell放完了, 連好線了, 大致長這樣:

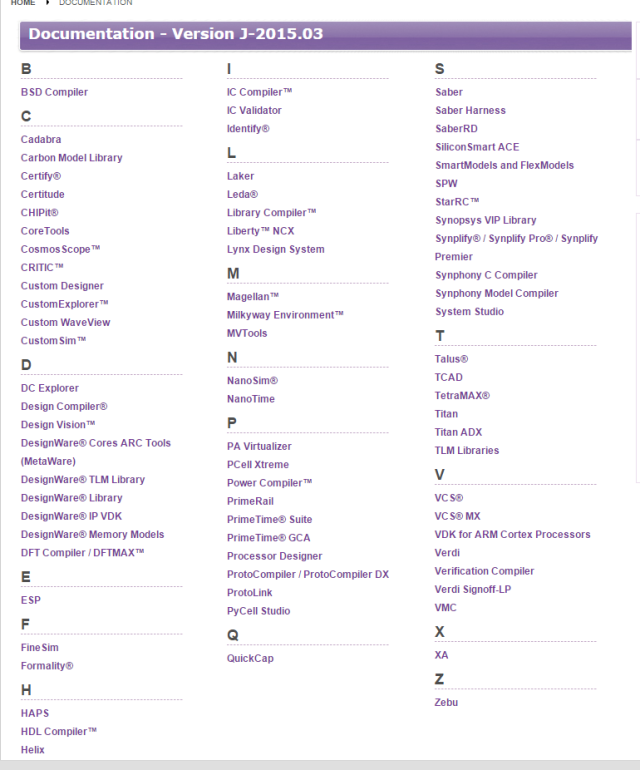

圖中的那幾個(gè)淡藍(lán)色的Cell就是Standard Cell, 連線未顯示.你要敢把這個(gè)Design交到Fab去做, 人家分分鐘咒你***.為什么呢? 打個(gè)比方: 我想讓你幫我剪一個(gè)窗花, 給你一張A4紙(大概58800mm2), 然后說, 我想要剪個(gè)窗花, 但是窗花的總面積不要超過1mm2, 最好還要有鏤空, 有個(gè)人.. blah blah blah...恩. 差不多一個(gè)意思..所以為了讓廠家和你不要那么難過, 需要在片上沒東西的地方加上Filler, 也就是長得像Standard Cell但是里面就是一坨沒有連線的金屬和輕摻雜層的東西.之后, 兩大門神決定了你能不能提交:門神1: Design Rule Check (DRC)必殺1: Area XX too small必殺2: XX to XX must be greater than or equal to 0.038必殺3: ...推薦武器: Calibre RVE, ASSURA, 仔細(xì)檢查+喊師兄幫忙每一招都對應(yīng)的是(由于技術(shù)原因或者安全原因)無法被制作出來的部分.反正招招必死. 想擊敗他必須一招都不能中(No Design Rule Violation).門神2: Layout Versus Schematic check (LVS)必殺: Layout does not match Schematic.推薦武器: Calibre RVE, ASSURE, 喊老板幫忙恩. 就是確定你畫的這個(gè)奇形怪狀的Layout跟一開始的電路圖是對的上號的.雖然此門神僅有一招, 但是這招千變?nèi)f化, 難以招架.兩大門神都開心了之后, 你就可以把你做出來的這個(gè)Graphic Database System II (GDSII) 文件交到廠商的手里了.附: Synopsys 武器一覽:

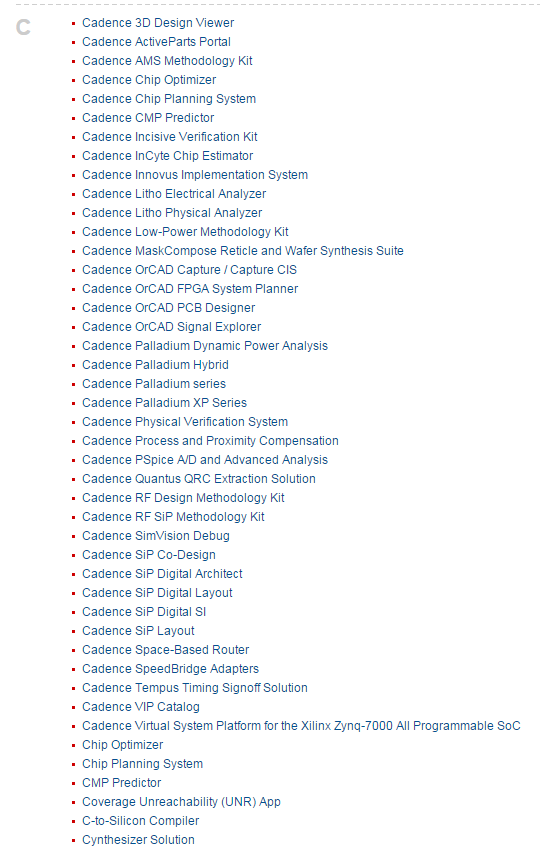

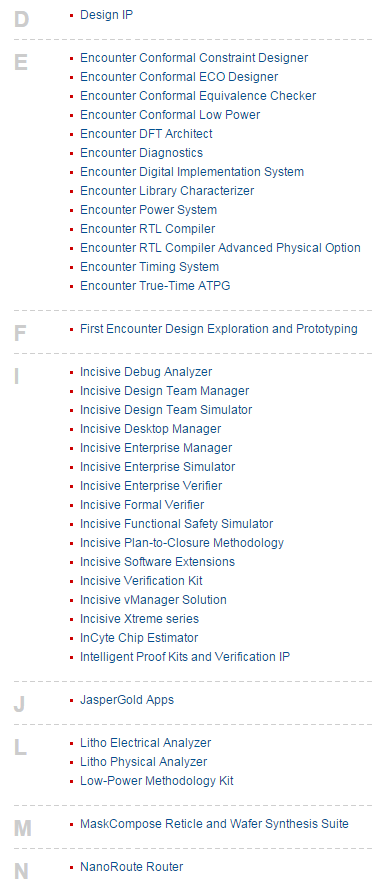

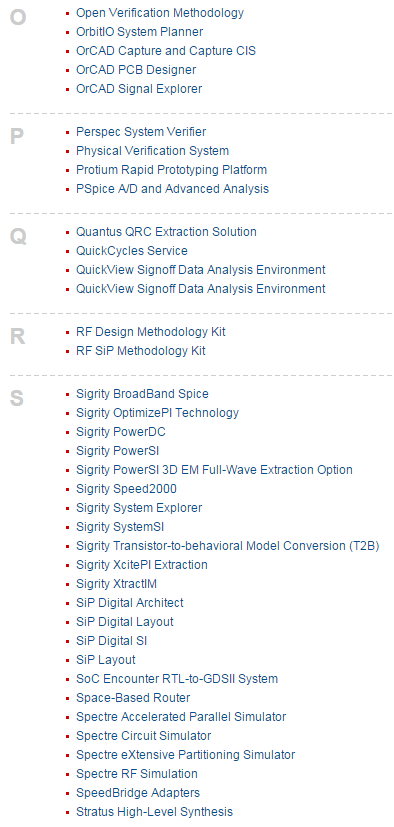

Cadence武器一覽:

從Fab回來以后, 戰(zhàn)斗還沒結(jié)束..Boss.Bonding & Packaging(封裝)必殺: 兩個(gè)pad黏一塊兒了!!!, pad金屬掉了!!!, 金屬絲斷了!!!.基礎(chǔ)武器: Bonding Machine

凡人即使有武器, 挑戰(zhàn)這個(gè)Boss也屬不易. 需要花重金升級武器才行, 比如說:

實(shí)在不行, 亦可祭出大殺器: 讓廠商Bond!這一步, 將芯片變成我們認(rèn)識的模樣:

從:

變成:

Boss.PCB Design必殺: 信號太多, 面積太小; 驅(qū)動(dòng)太弱, 電容太大; 燒Chip.推薦武器:Altium Design, Eagle等.

做出了Chip之后, 就需要畫一個(gè)配套的PCB, 將外圍電路在板上搭建好, 或者引至其他外設(shè)等.最終Boss.System Design必殺: 此Boss神通廣大, 一切外部設(shè)備都可以喚來作為必殺.推薦武器: The best weapon is the one between your ears. USE IT.

最終, 我們需要這個(gè)芯片在應(yīng)用中展現(xiàn)它的實(shí)力, 所以一個(gè)不滿足需求的芯片就是渣渣.

-

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423158 -

MOS管

+關(guān)注

關(guān)注

108文章

2410瀏覽量

66762 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1605瀏覽量

80580

原文標(biāo)題:一個(gè)芯片從構(gòu)想到完成電路設(shè)計(jì)的過程是怎樣的?

文章出處:【微信號:EngicoolArabic,微信公眾號:電子工程技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

模擬電路和數(shù)字電路PCB設(shè)計(jì)的區(qū)別詳解

模擬和數(shù)字電路基礎(chǔ)知識匯總

模擬和數(shù)字電路基礎(chǔ)知識匯總

模擬電路和數(shù)字電路PCB設(shè)計(jì)的區(qū)別詳解

模擬電路和數(shù)字電路PCB設(shè)計(jì)的區(qū)別

數(shù)字電路設(shè)計(jì)

模擬電路和數(shù)字電路學(xué)習(xí)筆記

模擬電路和數(shù)字電路的學(xué)習(xí)筆記

什么是模擬電路 什么是數(shù)字電路

模擬電路和數(shù)字電路的區(qū)別

模擬電路和數(shù)字電路設(shè)計(jì)/制作方面的差別

模擬電路和數(shù)字電路設(shè)計(jì)/制作方面的差別

評論