SRRC傳導輻射過不了,有人遇到過這種問題嗎,怎么解決的?

EDA365-WH:問一下,原理圖是誰提供的,芯片到B1之間為何射頻通道無匹配?你測試的是什么信號,現在的信號像是單音信號,而不是射頻調制信號?

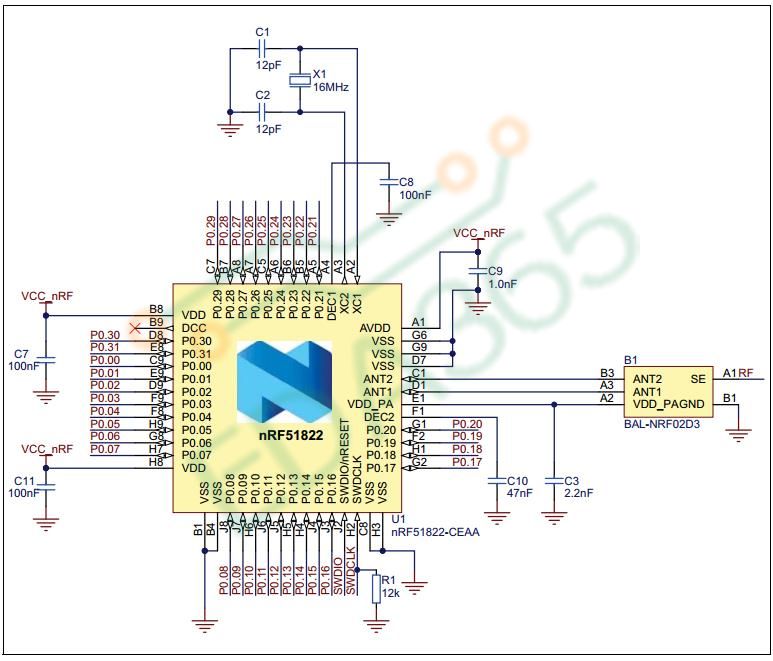

提問者:原理圖是巴倫的規格書中參考設計。

提問者:藍牙認證常用的三種調制,怎么會不是調制信號?11110000、10101010、還有個PRBS9,這里說的是發出來的數據包格式,調制方式是:GFSK。

網友1:是傳導雜散還是輻射雜散?傳導 ?不像是其它地方的干擾,傳導能掃到,輻射根本就沒有,感覺是芯片或者巴倫出來的。

EDA365-WH:藍牙設置變化頻點的話,這個干擾點是否變化?

提問者:有變化

網友2:檢查下電源,看是不是電源帶入的。

EDA365-WH:給個channel39,即輸出是中間頻點的,

目的是看這個信號和主信號之間的關系。從上面兩張圖的表現看和主信號間隔32MHz。但奇怪的是現在只能看到一邊,或者上邊,或者下邊很不合理。所以需要你主信號為chan39的測試結果,看看是否兩邊都有?

參考的PCB 走線,我個人認為這張圖上的AVdd和VDD 連在一起,不是好設計。調試時,你試試A1腳的電源單獨用外部電源供電。

提問者:之前都是在實驗室測試的,剛才弄了一個小時,在公司測,竟然測不到那個干擾。有自己測試過傳導雜散嗎,看看我是不是哪里沒有設置到?

EDA365-WH:測試雜散的過程:1、設置測試信號范圍,通過start和stop;2、設置RBW;3、峰值檢波設定。

有個前提,設備要正常工作,輸出滿足要求的調制信號和對應的輸出功率。

提問者:SPAN BW sweep 都是跟實驗室一樣的設置,檢波方式嘗試了峰值檢波、RMS檢波等都一樣的看不到那個干擾,我現在也不知道這個設備正不正常了?

EDA365-WH:從現在的視頻上看射頻信號,它都不占帶寬了,粗看上去更像一個單音信號了。

02

各位大神,請教一下,像這種SSMP連接器焊錫位置跟產品射頻性能(駐波)有關系嗎?

何老師:如果頻段很高,就有關系。有多大關系?可用HFSS仿真。廠家要求是對的。建議在EDA365網站問這個問題。

提問者:好的,謝謝何老師,但我跟廠家溝通過,說沒關系,只跟可靠性有關系。我們是Ku波段以下,請問影響大嗎?

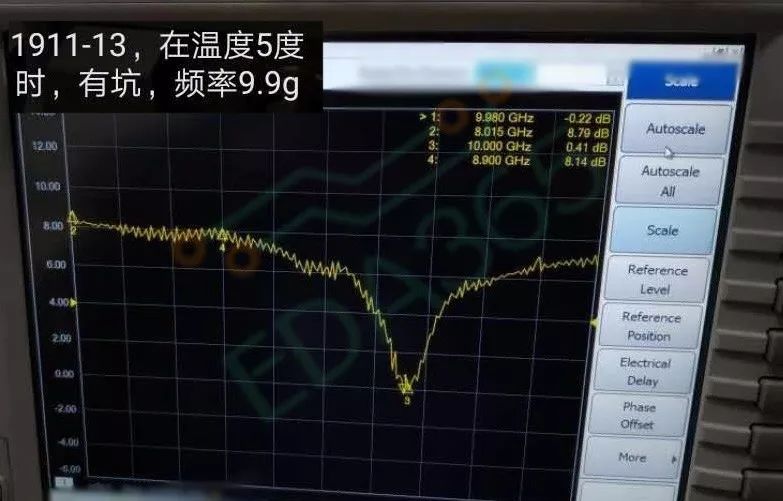

出現了這個諧振峰問題,請問是連接器焊接的問題嗎?

網友1:你測下駐波?

提問者:駐波沒問題,連接器的接地位置應該不會導致諧振產生吧?

EDA365-WH:肯定有影響呀。

提問者:為什么是在一定溫度下產生呢?也不是最低溫度?

EDA365-WH:Eda365 網站上有片帖子,說明一個SMA插座的接地孔設計不當,直接導致了一個諧振點。產生的根本原因是出現了一個諧振體,比如空隙等。

提問者:您的意思是焊縫有問題,而不是接地距離的問題?

EDA365-WH:?你的高低溫度范圍是多少?

提問者:-55到+85

EDA365-WH:其它什么都不變,只有溫度變化,在5攝氏度下發現10G諧波?完整描述是這樣嗎?

提問者:是的,您認為是什么原因導致的?

EDA365-WH:因為看你儀表輸出,本身帶有增益,說明,你現在的測試不僅僅是接插頭。所以建議,1、先探明一下這個諧振點發生的位置到底在哪兒?方法:1、有源電路擾動,2、接插頭擠壓擾動。

提問者:擠壓擾動的意思是?

網友1:駐波沒問題的話,你可以弄點吸附材料,看能不能改變一下諧振點。

提問者:好的,我做工藝的,也不太懂,我讓他們試試

EDA365-WH:用手用力壓,力量造成的SMA接觸位置形變一般會比你說的幾十度溫度變化造成的形變大。

提問者:好的,我讓設計師試試哈,謝謝。

03

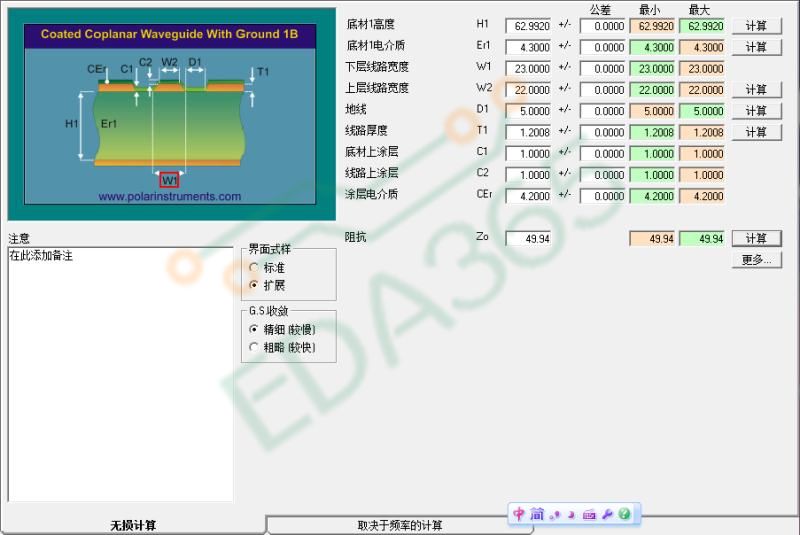

請教下,si9000算阻抗的時候,表層銅厚的選擇,是要加電鍍厚的銅厚嗎?如果1oz的基銅厚,計算的時候是應該按1.4mil計算還按加鍍銅后的總厚度2.9mil計算?

很多廠家給我是按1.4mil計算,然后調整的,是不是不對啊?請各位老師給個意見和看法,謝謝!

網友1:你讓他給你出阻抗報告就行了,讓他們控制好。

網友2:很多工廠不愿意給阻抗報告的。

網友1:那他們怎么保證他們控制的阻抗在范圍內,這個說法不合理吖!

網友2:很多工廠都做不好阻抗的。

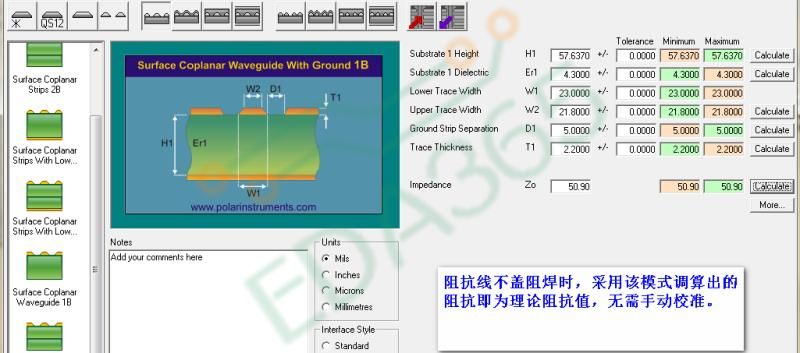

網友3:雙面板怎么做50歐阻抗啊,1.6mm板厚。

網友4:共面地。

網友5:用這種模型就可以了。

網友3:線寬要23嗎?W1怎么設置?

網友5:這個根據實際情況設置。

網友3:不是底面鋪地嗎?

網友4:標準線寬減0.6mil。

網友5:底面的地實際計算的時候影響不大,我是這么用的,要問問群里的大神老師們,不知道對不對。

提問者:線路厚度你取的1.2是不加鍍銅的厚度,加了鍍銅會厚一些,有些說法說要加鍍銅厚度,不知道是不是?

網友5:根據實際需要可以設置,POLAR右邊那些參數要找線路板廠要。距離厚度線寬等等,調整到50歐姆,調到合適你的要求。

網友4:

網友5:最終還是要儀器測試一下保證一致性。

網友4:是的!設計端給出理論設計參數,生產制程通過加工工藝實現阻抗要求,最終出貨前進行儀器檢測、提供檢驗報告。

何老師:群里也潛伏高手啊!提供的帶地平面的共面波導模型,就是解決雙面板厚介質的阻抗控制。我在EDA365公開課(4月13日)上也講過。

04

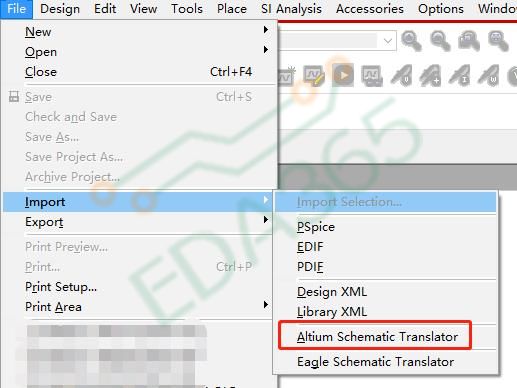

各位大師,請教個問題:AD軟件的原理圖怎么到cadence 的capture里面編輯?

網友1:在AD里直接編輯就是了,最后倒出來網表就行了。我記得還有版本限制,只能導成低版本的orcad,所以直接導網表最省事,沒版本限制。

提問者:想要用AD里面的封裝去設計新的圖紙,導網表不夠用。

網友2:capture里面有AD轉換器,需要AD的prj文件,只要在AD里面將SchDoc文件,.PcbDoc文件另存為ASCII碼文件,然后保存編譯文件*.rjPCBStructure,和工程文件*.PrjPCB,最后在capture里面導入工程文件就好了。

你用的哪個版本capture?

提問者:16.6的cadence。

網友2:16.6是可以的,好像再低版本就不行了。

網友2:PADS Logic原理圖可以通過EDIF格式的原理圖數據,直接導入Cadence Design Entry CIS原理圖環境中16.6和以上版本是可以的,低版本不知道。

提問者:我試試看,非常感謝。

網友4:具體怎么操作,可否指教下?

網友5:兩條差分線的間距在哪里設置啊?

網友4:是不是說這樣PADS LOGIC就可以轉成orcad。

賈老師:這份資料給到大家,可以讀讀看,很多問題便可以迎難而解。(公眾號首頁回復“賈老師”即可獲取!)

網友4:我以前在ti官網下到原理圖就是這樣操作的,成功過,但是AD或PADS的原理可以這樣轉成orcad嗎?有沒有試過。

網友2:AD是肯定可以的,我轉過,原理圖pcb都可以,PADS只是看了教程,因為還沒有pads軟件最近也用不到,所以沒試過。

-

單片機

+關注

關注

6035文章

44554瀏覽量

634683 -

AD

+關注

關注

27文章

868瀏覽量

150269 -

SRRC

+關注

關注

0文章

38瀏覽量

7598

原文標題:SRRC傳導輻射過不了?AD軟件怎么搞?看大咖們怎么說!

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SRRC傳導輻射過不了?AD軟件怎么搞?看大咖們怎么說

SRRC傳導輻射過不了?AD軟件怎么搞?看大咖們怎么說

評論