就像我們為系統功耗、接地及信號回路找到合適配置時,往往會引入一些干擾。在理解IC放大器的“去耦”、“接地”概念時也常常會被一些顯而易見的問題所愚弄。

下面為大家闡述一個一般性原則,之后我們再慢慢討論與集成電路放大器相關的去耦與接地問題——

首先請思考:電流流向何處?

表面來看,這是一個顯而易見的問題。但提到電流時,人們一般都會想到電流從某個地方“流出”,然后“流過”其他地方,卻忽視了電流如何流回源點的問題。在實際操作中,人們似乎認為所有“接地”或“電源電壓”點都是相等的。但忽略了一個事實 :這些點構成電流在其中流動并產生有限電壓,它們是導體網絡的一部分。

如果要進行前瞻性規劃,我們必須得考慮電流的起點及返回點,必須確定結果產生的電壓降的作用。而這又要求對去耦及接地電路的原理有一定的了解。然而在設計采用了集成電路時,這樣的信息往往無從獲取與難以理解。

我們的IC放大器是非常常用的線性IC之一,但幸運的是:就功率及接地問題而言,多數運算放大器都可歸入少數類別。盡管系統配置可能帶來令人生畏的去耦及信號回路問題,但通過了解運算放大器,我們可以找到解決更多此類問題的基本方法。

運算放大器有四個引腳

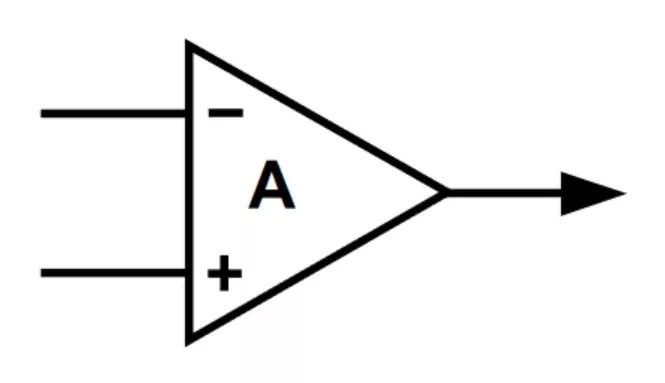

一般的讀者在看過任何一本運算放大器的課本之后,可以都會認為:理想的運算放大器應該有三個引腳——一對差分輸入引腳和一個輸出引腳。如下圖所示:

圖1:常規“三端”運算放大器

但如果你真的有了解基本原理,那么必然能看出事實并非如此。如果放大器有一個輸出電壓,那它必然以某個點為參考進行測量。從理想運算放大器來看,它擁有無限的共模抑制性能,因而可以排除輸入引腳作為參考點的可能。如此來看,必然還存在著第四個引腳。換個角度來看,如果放大器需要向負載提供輸出電流,則該電流必須從某個地方進入放大器。而理想情況來看,輸入電流不流動,這樣一來結論仍然是“需要第四個引腳”。

一種常見的做法是在圖中指出第四個引腳為“接地”端。我們不討論什么是“接地”端,多數集成電路運算放大器(包括很多模塊化運算放大器)并不存在“接地”端。對于這些電路 ,第四個引腳是電源引腳中的一個或兩個。這種情況 下,人們傾向于將兩個電源電壓與接地歸在一起。電源線路確實會在放大哭帶寬范圍內,在所有頻率下產生較低的阻抗。然而,當阻抗要求未得到滿足時,眾多問題就會隨之而來,包括噪聲、瞬態響應差,振蕩等問題。

差分至單端轉換

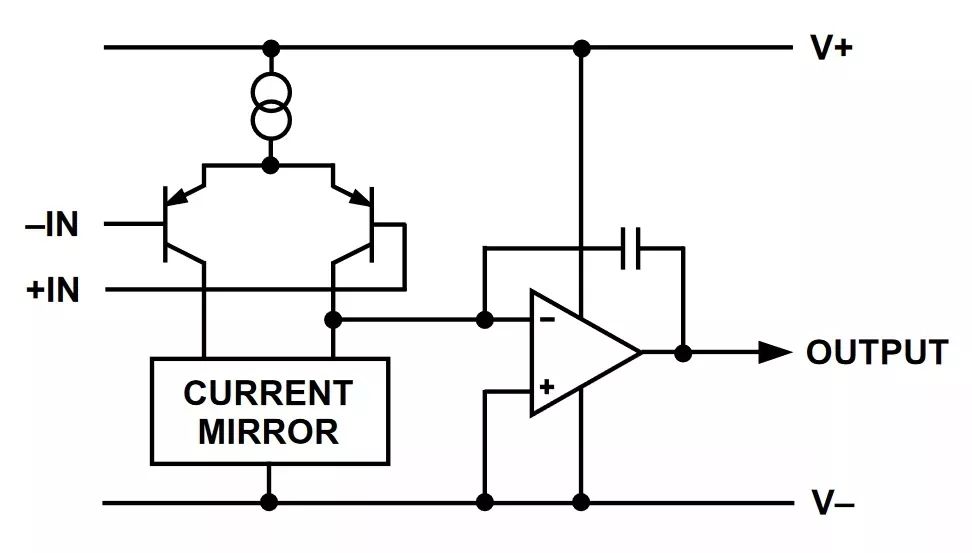

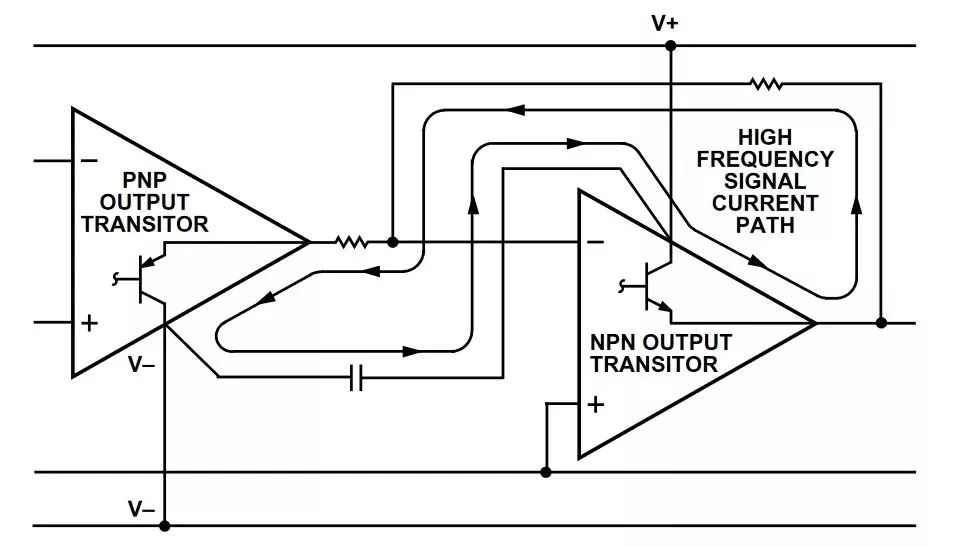

簡單運算放大器的基本要求之一是“輸入端加載的全差分信號必須轉換成單端輸出信號”。單端指的是相對于經常被忽視的第四個引腳而言的。這可能使問題復雜化。如下圖2所示:

圖2:簡化版“真實”運算放大器

上圖所示信號流用于多種流行的集成電路系列中。雖然細節不盡相同,但基本信號路徑與101、741、748、777、4136、503、515等集成電路運算放大器大致相同。電路首先將差分輸入電壓轉換成差分電流。該輸入級函數在圖2中表示為PNP晶體管。然后通過與負供電軌相連的電流鏡,將電流從差分轉換成單端形式。電流鏡像輸出驅動差一個電壓放大器以及作為積分器連接的功率輸出級。該積分器控制著開環響應,其電容既可外加亦可內置。關于上面這種簡化型號的說明大多都沒有突出積分器擁有一個差分輸入的事實 。由幾個基極發射極電壓提供正偏置,同相積分器輸入則以負電源作為參考 。

顯然,放大器輸出與負電源之間的大部分電壓差會出現在整個補償電容中。如果負電源電壓突然發生變化,積分器放大器將強制輸出隨之而變。當整個放大器處于閉環配置時,其輸入端產生的誤差信號將深度恢復輸出 ,但恢復程度受限于放大哭喊的壓擺率。結果就是,這類放大器可能擁有出色的低頻電源抑制性能,但負電源抑制卻存在較大限制。由于導致輸出恢復的是流程輸入端的反饋信號,因此,對于頻率輸出恢復的是流程輸入端的反饋信號。因此,對于頻率超過閉環帶寬的信號,負電源抑制比將接近0。即:高速高電平電路可以通過負電源線的公共阻抗與低電平電路“通信”。

Attention:此類放大器的問題與負電源端相關。雖然正電源抑制比也可能因頻率增加而下降,但其影響程度較輕。一般而言,正電源上的小瞬變只會對信號輸出產出輕微影響。這些靈敏度之間的差異可能使放大器瞬態響應出現明顯不對稱現象。如果驅動放大器的目的是在其額定負載范圍內產生正電壓擺幅,則放大器將從正電源吸取電流脈沖。

這樣的脈沖可能導致電源電源瞬變,但正電源抑制將最大程度地降低對放大器輸出信號的。在與此相對的情況下,負輸出信號將從負電源中抽取電流。如果脈沖在總線上導致“毛刺”,則欠佳的負電源抑制性能將在放大器輸出端帶來類似的“毛刺”。雖然正脈沖測試可以得到放大器瞬態響應,但負脈沖測試實際上可以助您更好地了解電源負軌瞬態響應,而不是放大器響應!

事實上,電源脈沖響應本身并不是放大器上可能出現的東西。30或40厘米的電線可以充當一下高Q電廠,從而給阻尼通常過高的電源響應增加高頻成分。在放大器附近安裝一個去耦電容也不一定能解決問題,因為電源必須在某個地方去耦。如果去耦電流注過較長路徑 ,仍有可能產生不良毛刺。

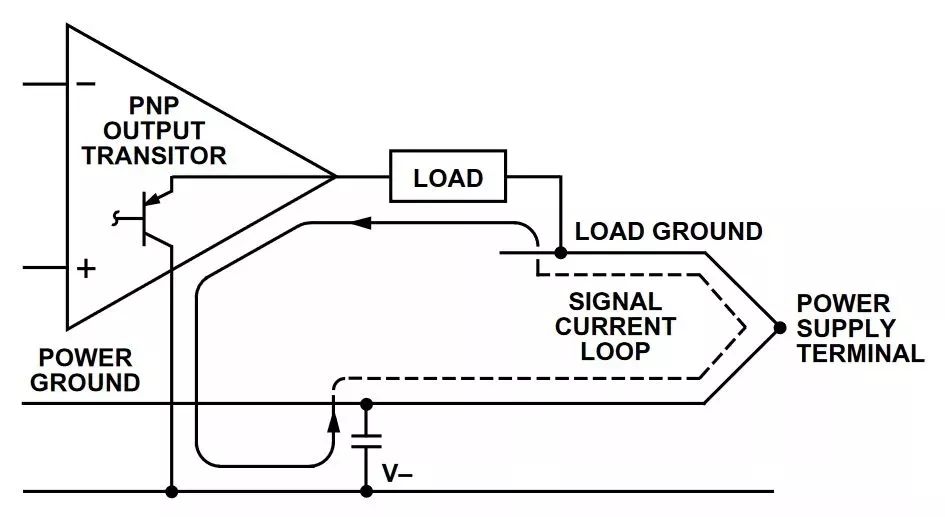

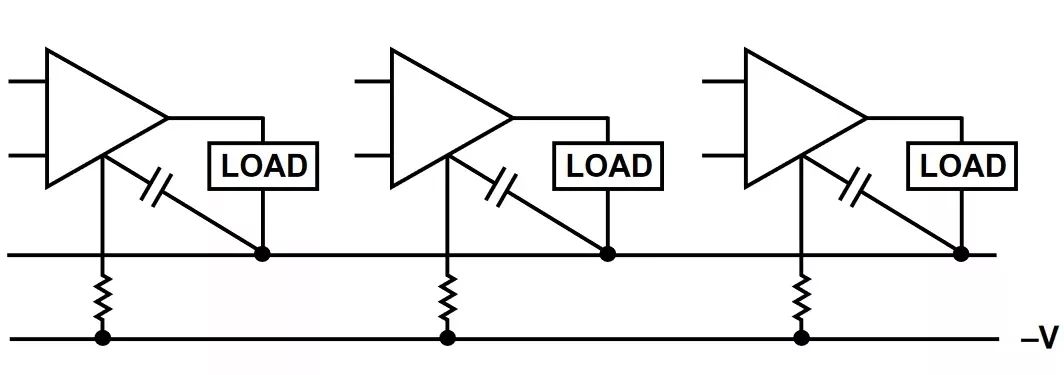

圖3所示為負電源去耦的三種可能配置。在3a中,虛線表示通過去耦線路及接地線路的負信號電流路徑。如果負載“接地”及去耦“接地”在電源處相接,則接地線路上的毛刺類似于負電源總線上的毛刺。根據反饋及信號源的“接地”方式,去耦電容導致的有效干擾可能大于電容的設計抗干擾能力。

圖3a:無效負電源去耦

圖3b展示了如何利用去耦電容降低V形及接地總線的干擾。負載電流中的高頻成分被限制在一個不含接地路徑的環路中。如果電容的容量夠大、質量符合要求,則可降低負電源上的毛刺而不干擾輸入或輸出信號路徑 。

圖3b:針對“接地”負載優化的去耦負電源

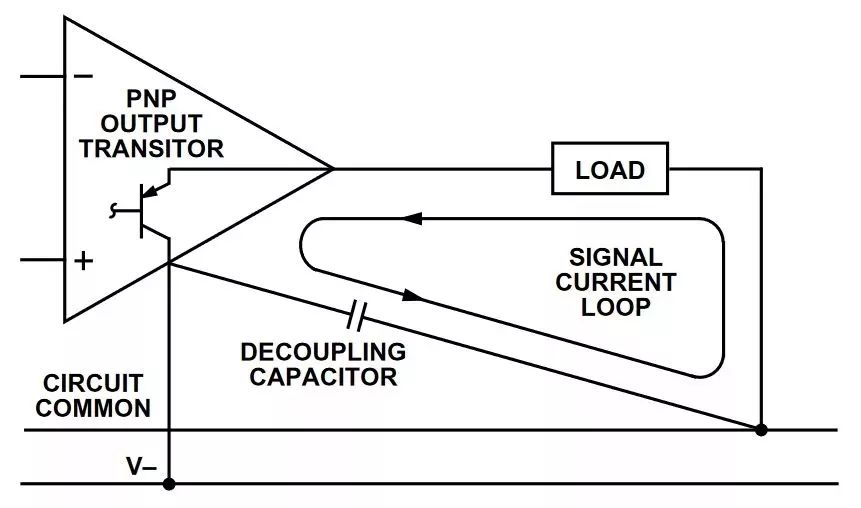

如果負載情況復雜(如圖3c),則需要進行更多的思考。如放大器驅動的是流向虛擬地的負載,則實際負載電流不會返回接地。相反,該電源必然由形成虛擬地的放大器提供。

圖3c:針對 “虛擬地”負載優化的去耦負電源

在這種情況下,如果將第一放大器的負電源去耦至第二放大器的正電源,則會閉合快速信號電流環路而不干擾接地路徑或信號路徑 。當然,為了避免干擾輸出基準電壓源,必須為第二放大器提供從接地至V形總線的低阻抗路徑。理解去耦電路的關鍵在于認清實際負載和信號電流的去向。而優化電路的關鍵是在接地等信號路徑旁路這些電流。

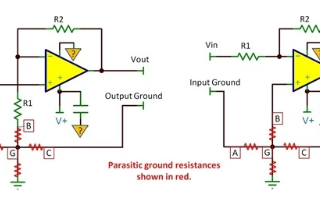

考慮整個電路時,通常會出現沖突。例如,多個放大器可能由同一電源驅動,而每個放大器又需要獨立的去耦電容。總體而言,去耦電容全部呈并聯 狀態。然而,事實 上,互連電源的電廠及接地線路 會將這種看似無礙的配置轉換成一個復雜的 L-C 網絡。在處理快速信號波陣面的電路中,通過數厘米線纜并聯的去耦網絡通常意味著麻煩。

圖4:并聯去耦諧振阻尼

圖4展示了通過小電阻來降低 不良諧振電路 Q 值的方法。一般情況下,這些電阻是可以容許的,因為它們在運算放大器電源端將不良高頻叮當聲轉換成小阻尼信號。雖然剩余信號具有較多的低頻成分,但可以通過運算放大器的電源抑制性能而予以處理。

-

放大器

+關注

關注

145文章

14115瀏覽量

216433 -

電流

+關注

關注

40文章

7118瀏覽量

134348 -

IC

+關注

關注

36文章

6102瀏覽量

178557

原文標題:一文助你掌握IC放大器中那些“去耦”、“接地”~

文章出處:【微信號:WW_CGQJS,微信公眾號:傳感器技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

去耦電容的接地原則

接地和去耦基礎知識

一文理清IC放大器中的去耦與接地問題

不良去耦技術對放大器和ADC的性能影響解析

IC的去耦有什么作用

去耦電容的接地原則

糟糕的去耦會增加放大器的失真

AN-202: IC放大器用戶指南:去耦、接地及其他一些要點

評論