近日,微電子所集成電路先導工藝研發中心,面向5納米及以下節點高性能和低功耗晶體管性能需求,基于主流后高K金屬柵(HKMG-last)三維FinFET器件集成技術,成功研制出高性能的負電容FinFET器件。

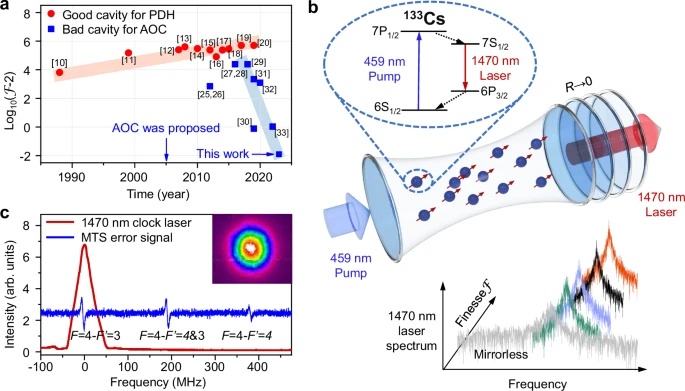

現有硅基晶體管受玻爾茲曼熱力學限制,室溫下亞閾值擺幅SS大于等于60mV/dec,阻礙了工作電壓的繼續降低。當集成電路技術進入5納米及以下節點,隨著集成度的持續增加,在維持器件性能的同時面臨功耗急劇增加的嚴重挑戰。先導中心殷華湘研究員的團隊在主流后HKMG FinFET集成工藝的基礎上,通過材料工藝優化和多柵器件電容匹配設計,結合高質量低界面態的3納米鉿鋯金屬氧化物薄膜,研制成功性能優異的NC-FinFET器件,實現了SS和閾值電壓回滯分別為34.5mV/dec和9mV的500納米柵長NC-FinFET器件,以及SS和閾值電壓回滯分別為53mV/dec和40mV的20納米柵長NC-FinFET器件。其中,500納米柵長NC-FinFET器件的驅動電流比常規HfO2基FinFET器件(非NC-FinFET)提升了260%且電流開關比(Ion/Ioff)大于1E6,標志著微電子所在新型NC-FinFET器件的研制方面取得了重要進展。

上述最新研究結果發表在國際微電子器件領域的頂級期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2019.2891364),并迅速受到國際多家研發機構的高度關注。

該項集成電路先導工藝的創新研究得到國家科技重大專項02專項和國家重點研發計劃等項目的資助。

圖1(a)負電容FinFET基本結構;(b-c)三維器件溝道結構與鐵電HZO膜層結構;(d-e)器件I-V與SS特性;(f)最新器件性能國際綜合對比(SS與回滯電壓越小越好)。

-

電容

+關注

關注

100文章

6038瀏覽量

150273 -

微電子

+關注

關注

18文章

380瀏覽量

41197

原文標題:【成員風采】微電子所在新型負電容FinFET器件研究中取得重要進展

文章出處:【微信號:iawbs2016,微信公眾號:寬禁帶半導體技術創新聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

上海光機所在多路超短脈沖時空同步測量方面取得研究進展

上海光機所在基于空芯光纖的超快脈沖壓縮與紫外飛秒激光產生研究中取得進展

中科院微電子所在光子集成激光探感技術方面取得進展

電子所受洛倫茲力是相反的嗎為什么

泰凌微電子、谷歌與和眾科技的Matter聯合項目取得重大進展

復旦大學在壓電能量采集接口電路方向取得重要科研進展

微電子所在新型負電容FinFET器件研究中取得重要進展!

微電子所在新型負電容FinFET器件研究中取得重要進展!

評論