現在的MOS驅動,有幾個特別的需求

1低壓應用

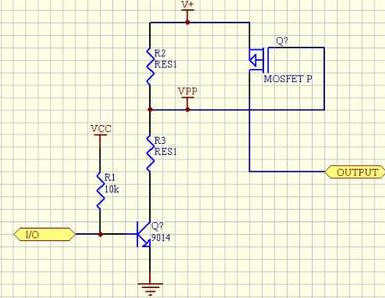

當使用5V電源,這時候如果使用傳統的圖騰柱結構,由于三極管的be有0.7V左右的壓降,導致實際最終加在gate上的電壓只有4.3V。這時候,我們選用標稱gate電壓4.5V的MOS管就存在一定的風險。

同樣的問題也發生在使用3V或者其他低壓電源的場合。

2寬電壓應用輸入電壓并不是一個固定值,它會隨著時間或者其他因素而變動。這個變動導致PWM電路提供給MOS管的驅動電壓是不穩定的。

為了讓MOS管在高gate電壓下安全,很多MOS管內置了穩壓管強行限制gate電壓的幅值。在這種情況下,當提供的驅動電壓超過穩壓管的電壓,就會引起較大的靜態功耗。

同時,如果簡單的用電阻分壓的原理降低gate電壓,就會出現輸入電壓比較高的時候,MOS管工作良好,而輸入電壓降低的時候gate電壓不足,引起導通不夠徹底,從而增加功耗。

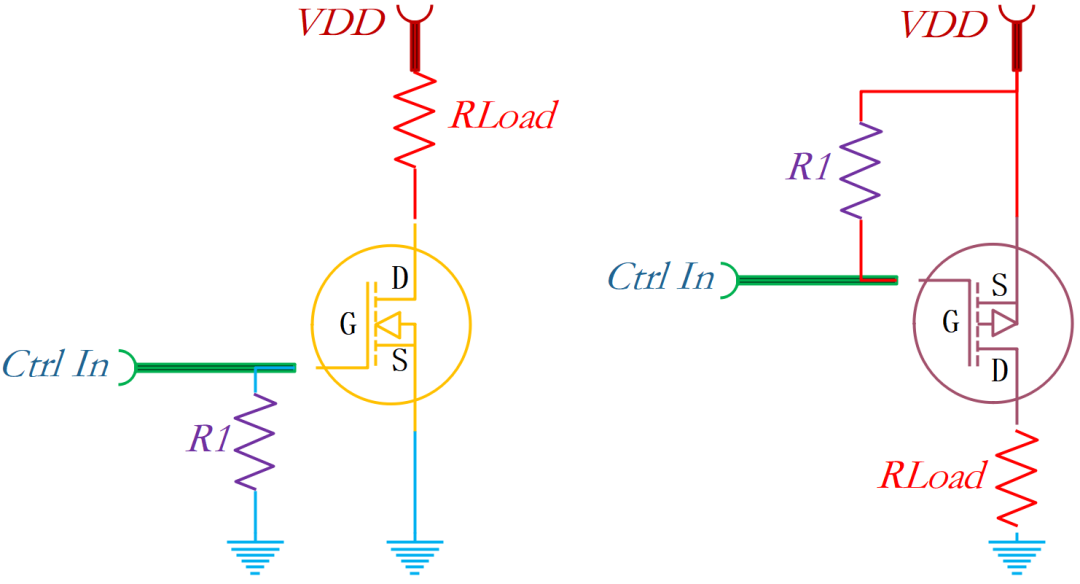

3雙電壓應用在一些控制電路中,邏輯部分使用典型的5V或者3.3V數字電壓,而功率部分使用12V甚至更高的電壓。兩個電壓采用共地方式連接。

這就提出一個要求,需要使用一個電路,讓低壓側能夠有效的控制高壓側的MOS管,同時高壓側的MOS管也同樣會面對1和2中提到的問題。

在這三種情況下,圖騰柱結構無法滿足輸出要求,而很多現成的MOS驅動IC,似乎也沒有包含gate電壓限制的結構。

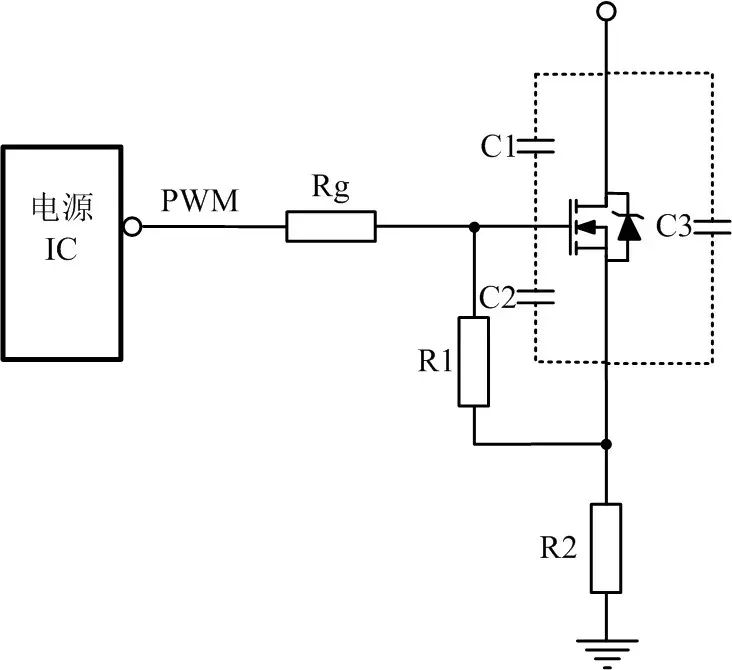

于是我設計了一個相對通用的電路來滿足這三種需求。

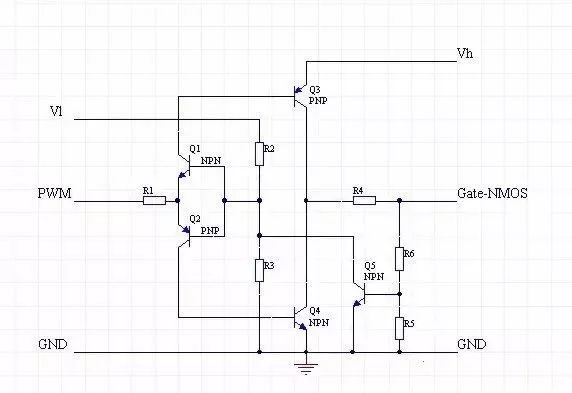

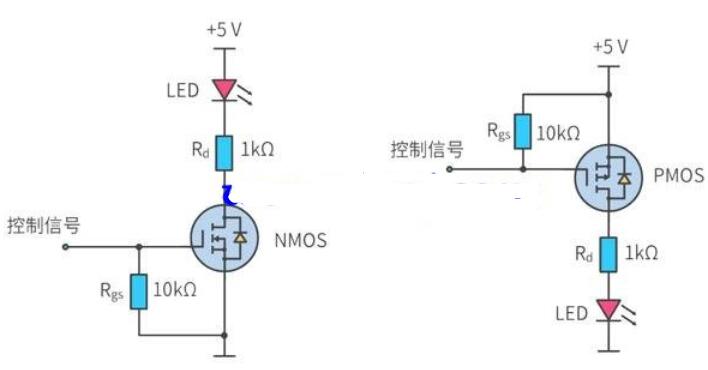

針對NMOS驅動電路做一個簡單分析:

Vl和Vh分別是低端和高端的電源,兩個電壓可以是相同的,但是Vl不應該超過Vh。Q1和Q2組成了一個反置的圖騰柱,用來實現隔離,同時確保兩只驅動管Q3和Q4不會同時導通。

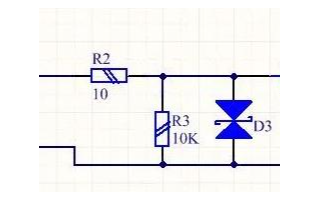

R2和R3提供了PWM電壓基準,通過改變這個基準,可以讓電路工作在PWM信號波形比較陡直的位置。

Q3和Q4用來提供驅動電流,由于導通的時候,Q3和Q4相對Vh和GND最低都只有一個Vce的壓降,這個壓降通常只有0.3V左右,大大低于0.7V的Vce。R5和R6是反饋電阻,用于對gate電壓進行采樣,采樣后的電壓通過Q5對Q1和Q2的基極產生一個強烈的負反饋,從而把gate電壓限制在一個有限的數值。這個數值可以通過R5和R6來調節。

最后,R1提供了對Q3和Q4的基極電流限制,R4提供了對MOS管的gate電流限制,也就是Q3和Q4的Ice的限制。必要的時候可以在R4上面并聯加速電容。

這個電路提供了如下的特性:

1用低端電壓和PWM驅動高端MOS管。

2用小幅度的PWM信號驅動高gate電壓需求的MOS管。

3gate電壓的峰值限制

4輸入和輸出的電流限制

5通過使用合適的電阻,可以達到很低的功耗。

6PWM信號反相。NMOS并不需要這個特性,可以通過前置一個反相器來解決。

-

電路

+關注

關注

172文章

5926瀏覽量

172359 -

MOS

+關注

關注

32文章

1272瀏覽量

93856

原文標題:【實戰】根據要求設計MOS驅動電路!!!

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MOS管驅動電路原理與MOS管驅動電路布線設計

MOS管驅動電路原理圖

mos管高端驅動電路 高手才可以搞定的mos管調壓電路

根據要求設計MOS驅動電路

根據要求設計MOS驅動電路

評論