引言

隨著CompactPCI在中國大范圍的普及和使用,越來越多的企業開始研制基于CompactPCI接口的產品,市場上有一些專用PCI接口芯片。FPGA(現場可編程門陣列)技術的快速發展使得萬門以上乃至幾十萬門邏輯陣列的使用越來越普遍。與專用PCI接口芯片相似,很多FPGA制造商都提供了PCI接口核邏輯。設計者可以將PCI用戶邏輯與PCI Core集成在一片FPGA里,并且可以在頂層通過仿真來驗證PCI接口以及用戶邏輯設計的正確與否,這樣可以大幅度提高調試速度、縮短開發周期、提高電路板的集成度和系統的性能。目前,開發者最常用的兩種PCI IP核是ALTERA公司的PCI MEGACORE和XILINX公司的PCI Logicore。本文所介紹的PCI_MT64 IP核是ALTERA公司開發的一個功能強大的CPCI接口內核,最高能實現64位的數據寬度和66MHz的工作頻率。文章介紹了PCI_MT64的工作原理以及此IP核在CPCI總線數據采集卡的應用設計,并通過本地邏輯設計測試了此IP核的功能。

PCI_MT64 IP核的原理和結構

根據用戶性質的不同,CPCI接口類型分為兩種:MASTER(主設備) 和TARGET(從設備)。ALTERA公司據此開發了多種 PCI IP核:PCI_MT64、PCI_MT32、PCI_T64和PCI_T32。由于設計需要完成66MHz、64位寬度數據傳輸,且在主模式下DMA控制器才能工作,因此選擇了PCI_MT64。

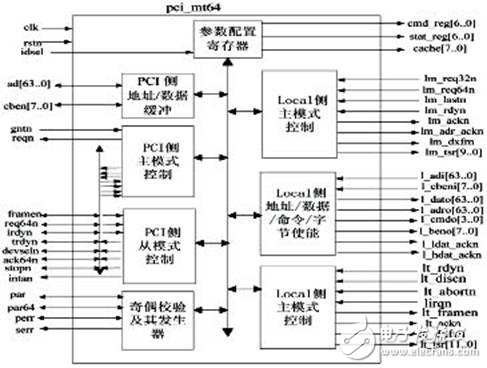

PCI_MT64是支持33/66MHz工作頻率、64位PCI總線、支持主/從模式的PCI IP功能模塊。當其寬度為64位、系統時鐘為66 MHz時,峰值傳輸速率為528 MB/s。其主要由8個模塊組成,如圖1所示。

圖1 PCI_MT64的模塊結構

參數配置寄存器:提供參數確定的寄存器,包括設備識別、供應商識別、分類代碼、修訂版本、基址寄存器和子系統供應商等信息。在設計中,ALTERA公司提供了參數化的圖形界面,用戶只需按PCI協議輸入或選擇合理的值即可完成該寄存器的配置。

PCI側地址/數據緩沖模塊:用來緩存PCI總線側的地址數據輸入、輸出信號。

PCI側主/從模式控制模塊:用于控制PCI總線的主設備和從設備的各種時序操作。

Local側主/從模式控制模塊:用于控制PCI_MT64與本地邏輯的各種操作。

Local側地址/數據/命令/字節使能模塊:接收和輸出用戶側的所有地址、數據、命令、字節使能等信號。

奇偶校驗模塊:用于對數據、地址、命令進行奇偶校驗。

PCI_MT64 IP核在CPCI數據采集卡中的應用設計

PCI_MT64 IP核在CPCI數據采集卡中的功能:與CPCI總線之間的通信和數據傳輸,并做奇偶校驗以保證正確性,即將復雜的CPCI總線信號轉換為相對簡單易操作的CPCI本地總線信號,它從CPCI總線側獲得傳輸命令和讀寫數據的地址后,一方面對這個操作命令做出反應,將其傳達給本地邏輯,另一方面將CPCI總線傳送過來的數據地址映射為本地邏輯可識別的地址。當本地端總線準備好后,PCI IP核會收到本地邏輯做出的響應信號,然后根據主從模式,讀/寫命令的不同執行相應的時序。簡單的說,它是CPCI總線和本地邏輯的橋梁,所以首先要設計CPCI本地側邏輯實現PCI IP核功能驗證,如圖2所示。

圖2 CPCI本地端邏輯設計

以上設計能快速評估PCI IP核的功能,當PCI_MT64作為一個主設備,主模式控制邏輯連接DMA控制器來完成一次PCI主模式讀寫傳輸。當PCI_MT64作為一個從設備,它觸發從模式控制邏輯來執行一次從模式傳輸。CPCI數據采集卡使用DMA方式上傳數據,即將數據采集模塊的數據處理后,緩存到FIFO,從FIFO中傳輸數據到上位機;使用從模式寫傳輸發送控制命令到板卡不同寄存器。當進行一次從模式傳輸時,PCI IP核不能啟動總線操作,只能依賴于主設備從其中讀取數據或向其傳送數據,相關設計較為簡單,而DMA模式是PCI_MT64配合自主設計的DMA控制器來實現的,所以DMA控制器是整個設計的關鍵。

DMA控制器由DMA寄存器和DMA狀態機兩個模塊構成。DMA寄存器是主機控制DMA的窗口,包括控制狀態寄存器、地址寄存器、字節寄存器、中斷狀態寄存器和本地地址寄存器。DMA寄存器的地址直接映射到PCI的地址空間,其基地址對應PCI IP核中的配置寄存器Bar0。主機通過設置在存儲器地址空間的DMA寄存器來控制DMA傳輸。DMA狀態機是控制主模式寫傳輸的核心,產生主模式傳輸需求的各種信號。狀態跳轉條件來自DMA寄存器,IP核以及DMA FIFO。狀態機流程圖如圖3所示。

圖3 DMA狀態機

以鏈式DMA傳輸為例介紹其流程:主機首先把多組字節寄存器和地址寄存器的值寫入描述符FIFO,每一組字節寄存器和地址寄存器就是一個描述符;主機再寫本地地址寄存器和控制狀態寄存器即啟動了DMA狀態機,開始鏈式的數據傳輸。狀態機跳入裝載DMA狀態,通過對DMA FIFO的讀取將需要的值寫入寄存器中,經寄存器有效狀態進入等待請求狀態。當外部FIFO數據準備好,DMA狀態機向主機發送總線請求信號,并等待主機的總線允許信號,此時狀態機進入等待允許狀態;一旦接收到主機的總線允許信號,整個DMA傳輸開始,狀態機也進入數據傳輸狀態。在數據傳輸周期中,字節寄存器的值逐漸減少直到零時,一個描述符傳輸完成,每一個描述符傳輸完成的時候,狀態機并不進入結束狀態,而是直接進入空閑狀態,開始下一次描述符的傳輸,所以不產生中斷。等到DMA FIFO為空的時候,狀態機認為本次鏈式DMA傳輸完成,進入到結束狀態,此時產生中斷,一次鏈式DMA傳輸結束。

實驗調試及分析

PCI_MT64 IP核在CPCI數據采集卡中的應用主要是完成數據的高速傳輸,包括從模式寫傳輸方式的數據下傳(控制命令)和DMA方式的數據上傳(采集卡數據)。在QuartusII9.0環境下,運用Megacore PCI Complier對PCI_MT64進行設置,并對CPCI本地端邏輯進行了綜合編譯,生成網表文件,運用Testbench工具對從模式寫傳輸方式進行仿真,驗證了PCI_MT64 IP核的穩定性。其時序仿真如圖4所示。

圖4 從模式單周期寫仿真時序

圖4中是一個對地址為8000H的MEM域空間的單周期寫操作,在第3個時鐘周期,FRAME#低電平有效,此時pci_ad的值是8000H,pci_cben的值是0111B,表示存儲器寫,在TRDY#和IRDY#同時有效的時候,數據由pci_ad傳給l_dato,這里寫入的數據是66666666H。由仿真圖可以看到,pci_ad和l_dato的數據是一樣的,所以從模式單周期寫傳輸正確。單周期讀寫適合少量數據傳輸,不同寄存器控制命令的發送及DMA寄存器的設置都是通過從模式下單周期讀寫實現的。

為測試PCI_MT64 IP核的本地端邏輯設計,調用基于Windriver編寫的驅動程序和用戶界面實現數據的傳輸。這樣,既驗證了CPCI數據采集卡硬件邏輯的正確性,又驗證了軟件的正確性。其測試結果如圖5所示。

圖5 應用軟件測試界面

圖5中數據采樣率為500MHz,輸入信號頻率為16MHz,一個周期的采樣點數N=500/16=31.25,故250個點內應有250/31.25=8個周期的數據。采樣數據的幅值以十六進制格式在列表框中顯示。波形顯示了有限數據的連續傳輸,沒有任何數據丟失,驗證了基于PCI_MT64 IP核在數據采集卡中采用DMA方式傳輸數據的完整性及傳輸速度。

結束語

PCI_MT64 IP核能有效的滿足CPCI數據采集卡對數據高速傳輸的要求,實現CPCI接口功能,并能與用戶邏輯配合工作,實現數據的緩存和傳輸。相較于使用PCI專用芯片實現接口功能的方法,本設計具有電路板集成性能高、功耗低、成本低、方便移植等優點。

-

IP

+關注

關注

5文章

1702瀏覽量

149508 -

PCI

+關注

關注

4文章

663瀏覽量

130251

發布評論請先 登錄

相關推薦

PCI_MT64 IP核的原理和結構設計

PCI_MT64 IP核的原理和結構設計

評論