隨著物聯(lián)網(wǎng)應(yīng)用的興起,對(duì)芯片低功耗的需求也會(huì)越來(lái)越多。分析幾個(gè)關(guān)鍵的低功耗技術(shù),對(duì)比通用的設(shè)計(jì)方法,未來(lái)會(huì)有更多低功耗架構(gòu)的電路及方法出現(xiàn)。低功耗的需求一定是和應(yīng)用相關(guān),沒(méi)有最低,只有最合適的。

1 引言

隨著物聯(lián)網(wǎng)和智能城市及智能電網(wǎng)的普及,MCU 的應(yīng)用也迎來(lái)了井噴式的發(fā)展。目前國(guó)外大廠如ST、NXP、TI 等芯片公司占據(jù) MCU 大部分的市場(chǎng)份額,且提供全系列芯片及產(chǎn)品來(lái)滿足客戶(hù)需求。對(duì)于國(guó)內(nèi)公司來(lái)說(shuō),面臨的壓力和挑戰(zhàn)是除了技術(shù)本身外面,構(gòu)建 MCU 的生態(tài)系統(tǒng)也很重要。中國(guó)公司的優(yōu)勢(shì)在于中國(guó)是 MCU 應(yīng)用最大的市場(chǎng),本土企業(yè)更了解客戶(hù)的需求和痛點(diǎn)。為此需要在架構(gòu)創(chuàng)新性、產(chǎn)品的可靠性,低功耗設(shè)計(jì)及性能提升上做更多的努力。

2 MCU 技術(shù)

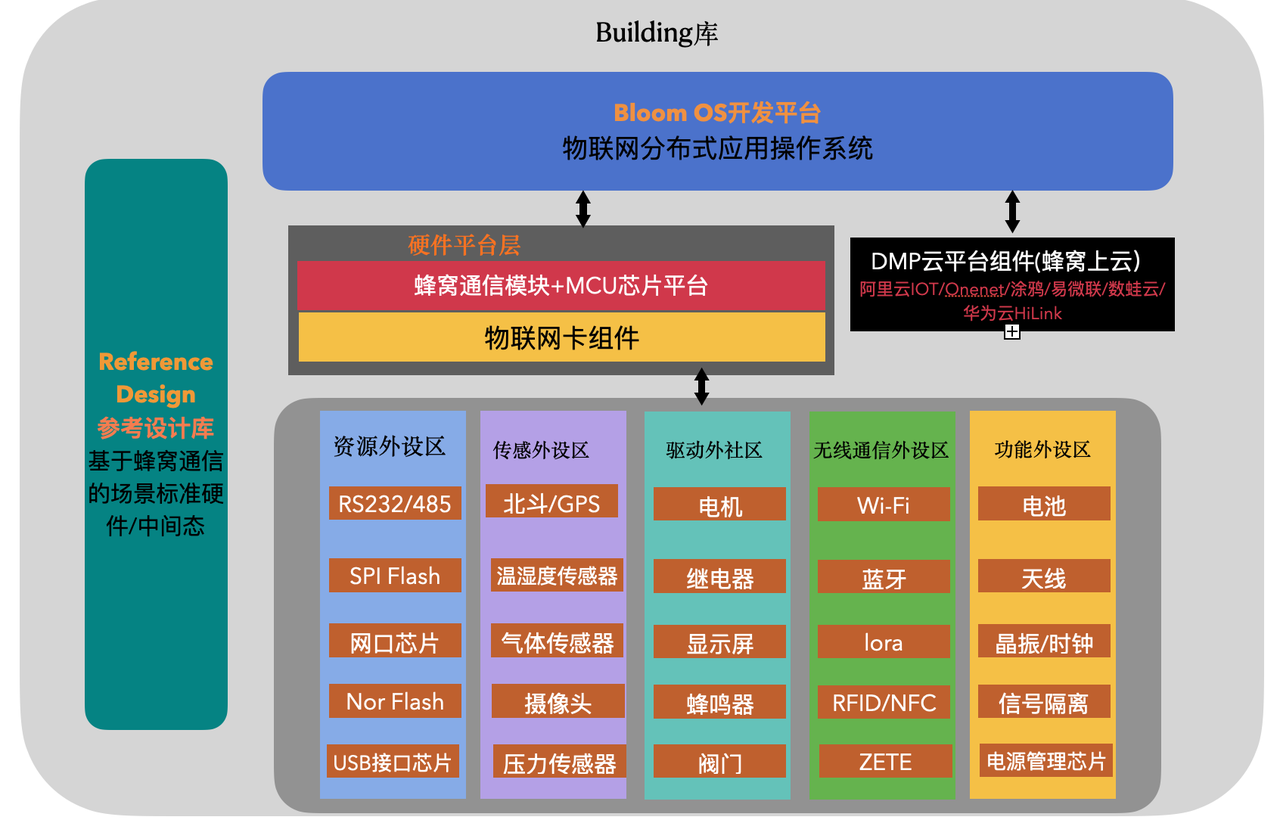

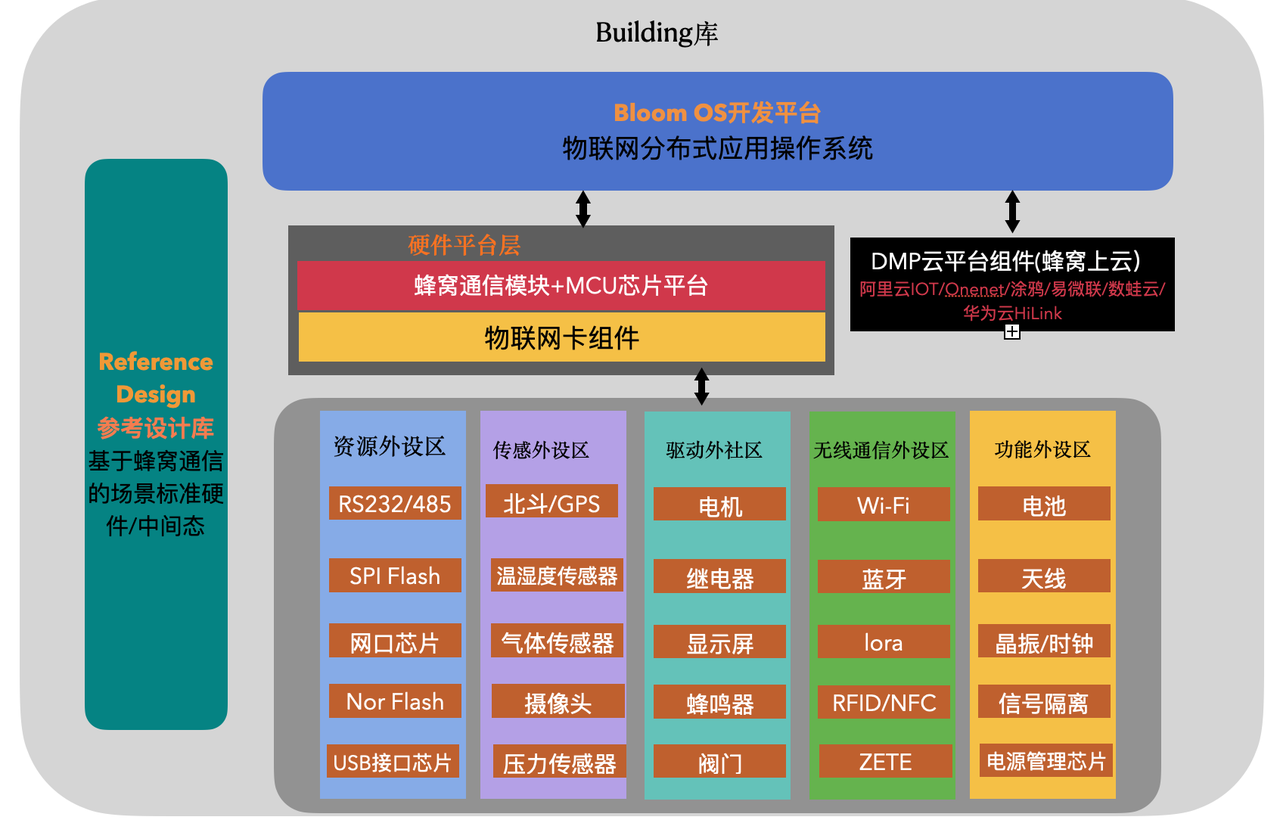

MCU 最初應(yīng)用領(lǐng)域主要在工業(yè)控制和消費(fèi)類(lèi)市場(chǎng),隨著 MCU 需求量和應(yīng)用的不斷擴(kuò)展,MCU 已全面向 SoC 方面發(fā)展,功能越來(lái)越強(qiáng)大,處理能力越來(lái)越強(qiáng),外設(shè)和接口不斷擴(kuò)充。為了滿足新的需求和高端應(yīng)用市場(chǎng),MCU 的架構(gòu)也發(fā)生了很大的變化,從 51 core 向 AMR 內(nèi)核發(fā)展,根據(jù)應(yīng)用場(chǎng)景和需求不同,8/16/32 bit MCU 會(huì)并存一段時(shí)間,圖 1 為 MCU 的應(yīng)用方向向各種智能應(yīng)用轉(zhuǎn)換。

選擇不同 bit MCU 要依據(jù)芯片的功能需求,性能需求,功耗要求及成本綜合考慮。圖 2 為各種 MCU 的占比圖(資料來(lái)源:SIA/WSTS Semico Research Corp)。

從成本方面來(lái)講,8 bit MCU 具有優(yōu)勢(shì),可滿足低端需求,而 32 bit MCU 因?yàn)樘峁└鼜?qiáng)大的運(yùn)算處理能力,更快的速度已經(jīng)成為高端 MCU 的標(biāo)配。而高端 MCU 通常搭載 AMR cortex-M 處理器,配合豐富的外設(shè)接口及高可靠性,高性能的模擬模塊,來(lái)提供滿足市場(chǎng)及客戶(hù)需求。MCU 中涉及的關(guān)鍵技術(shù)和問(wèn)題非常多,從系統(tǒng)設(shè)計(jì)開(kāi)始,如何定義系統(tǒng)架構(gòu),如何構(gòu)建平臺(tái)和MCU生態(tài)系統(tǒng)到數(shù)字電路設(shè)計(jì);從工藝的選擇到模擬電路的設(shè)計(jì),從可靠性設(shè)計(jì)到低功耗設(shè)計(jì);從應(yīng)用創(chuàng)新到滿足客戶(hù)各種需求 。每個(gè)方面都對(duì)設(shè)計(jì)公司提出很高的挑戰(zhàn)。

本文僅從低功耗設(shè)計(jì)的角度研究 MCU 在低功耗設(shè)計(jì)方面的一些技術(shù)挑戰(zhàn)和方向。

3 MCU 的低功耗設(shè)計(jì)

隨著物聯(lián)網(wǎng)的興起,各種可穿戴設(shè)備都需要電池供電,MCU 的要求除了豐富的功能模塊支持和高性能指標(biāo)之外,低功耗也成為一個(gè)非常重要的課題。特別是可穿戴設(shè)備大多采用電池供電,希望待機(jī)時(shí)間很長(zhǎng),所以低功耗設(shè)計(jì)的重要性就特別凸現(xiàn)。MCU 的低功耗設(shè)計(jì)不僅需要保證在正常模式下,芯片的功耗要低,而且需要合理配置工作模式,讓芯片能夠盡可能的省電,即大多數(shù)情況下,芯片處于省電模式下,盡可能延長(zhǎng)電池的使用壽命。圖 3 是一般 MCU 芯片的工作模式,為了省電,一般設(shè)計(jì)僅僅在需要工作時(shí)將必要的模塊打開(kāi),而大多數(shù)情況模塊處于 Sleep 模式,也即盡量降低處于 Normal 模式的時(shí)間。

低功耗的設(shè)計(jì)涉及正常模式的低功耗設(shè)計(jì)及睡眠模式下的低功耗設(shè)計(jì)兩個(gè)方面。這兩方面對(duì)于低功耗設(shè)計(jì)都非常重要,下面分別進(jìn)行分析。

3.1 Normal 模式的低功耗設(shè)計(jì)

MCU 芯片的周期從 Sleep 模式進(jìn)入 Normal 模式進(jìn)行數(shù)據(jù)處理,數(shù)據(jù)處理結(jié)束之后立即進(jìn)入 Sleep 模式。一般 MCU 還有一個(gè) Hold mode,功耗比 Normal 模式低,與系統(tǒng)定義相關(guān),即根據(jù)需要選擇性的開(kāi)關(guān)一些模塊并保持一定的狀態(tài)。

Normal 模式下的功耗包含數(shù)字動(dòng)態(tài)功耗和以模擬為主的靜態(tài)功耗。

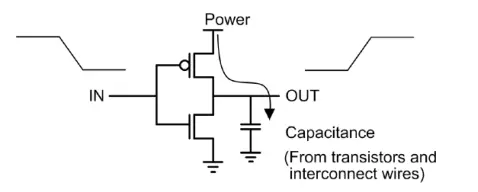

數(shù)字動(dòng)態(tài)功耗的表達(dá)式為式(1)

P=α×Vdd2×f×Cl (1)

其中,Vdd 為數(shù)字工作電壓,f 為數(shù)字工作頻率,Cl 數(shù)字模塊的負(fù)載,而α是開(kāi)關(guān)工作的比率。在 Normal 模式下,數(shù)字工作在低頻及采用深亞微米工藝使其 load 更小,盡量降低開(kāi)關(guān)的次數(shù)會(huì)大大降低數(shù)字部分的動(dòng)態(tài)功耗。但是工作電壓的降低會(huì)帶來(lái)速度的降低,會(huì)降低數(shù)字電路的抗干擾性能。圖 4 是不同模塊根據(jù)系統(tǒng)定義和需求工作在不同的電源電壓下的示例。 采用 Clock gated 技術(shù)[1](圖 5)可以大大降低功耗,使得數(shù)字模塊僅僅在需要工作時(shí)工作。另外降低系統(tǒng)頻率也會(huì)優(yōu)化功耗,但是會(huì)帶來(lái)處理速度的下降。所以數(shù)字動(dòng)態(tài)功耗的優(yōu)化需要結(jié)合系統(tǒng)需求來(lái)進(jìn)行。一般數(shù)字模塊通過(guò)合理的分配不同模塊工作在不同的電源電壓下,并且采用合理的門(mén)控時(shí)鐘方案和選擇合適的時(shí)鐘,以實(shí)現(xiàn)功耗的最優(yōu)化設(shè)計(jì)。

除了數(shù)字動(dòng)態(tài)功耗外,模擬模塊的設(shè)計(jì)也要求低功耗。在 Normal 模式下,模擬的模塊如電源管理模塊,Bandgap Reference 及 Voltage Regulation,在保證性能的情況下,盡可能降低模擬電路的功耗(圖 6)。

3.2 Sleep 模式下的低功耗設(shè)計(jì)

MCU 在睡眠模式下,為了得到低功耗,一般需要在如下幾個(gè)方面進(jìn)行設(shè)計(jì)優(yōu)化,系統(tǒng)級(jí),工藝級(jí),模擬及數(shù)字模塊設(shè)計(jì)。如圖 7 所示。

MCU 低功耗設(shè)計(jì)離不開(kāi)工藝的支持,工藝的選擇對(duì) MCU 的低功耗影響很大,一般 Foundry 廠家都提供 Low power 或 Low leakage 的工藝。芯片進(jìn)入睡眠模式后,數(shù)字電路大部分處于 power down的狀態(tài)。如果工藝選擇合適,數(shù)字電路在睡眠模式的漏電流就很小,芯片才可能實(shí)現(xiàn)低功耗的模式。

工藝越先進(jìn),漏電流越大。為此需要采用 Low leakage 的工藝來(lái)進(jìn)行低功耗的設(shè)計(jì)。器件的漏電流由 Gate 漏電流(由通過(guò) Gate 氧化層的載流子隧穿電流),深亞微米工藝下,Gate 氧化層厚度減小,進(jìn)入通過(guò)氧化層的電場(chǎng)增強(qiáng),隧穿效應(yīng)比較明顯。GIDL 電流,源漏的穿通電流,熱載流子效應(yīng)及反向PN結(jié)的遂穿電流都會(huì)導(dǎo)致漏電流的增加。所以工藝的評(píng)估非常重要[2](圖 8)。

另外進(jìn)入 Sleep 模式后,整個(gè)系統(tǒng)的功耗控制方案需要提前評(píng)估,是否需要 power gate 的控制,即斷開(kāi)模塊的電源,徹底斷電。或者需要規(guī)劃系統(tǒng)在進(jìn)入 Sleep 模式后,各個(gè)模塊的供電是如何考慮的?是否需要 DC-DC 或 LDO 供電,供電的電壓是多少?系統(tǒng)電源的策略對(duì)最終的低功耗有很大的影響。 比如采用 DC-DC 供電就比直接采用 LDO 更省電,但是 DC-DC 帶來(lái)的電源波動(dòng)對(duì)電路的影響需要結(jié)合系統(tǒng)需求來(lái)決定,也可以采用 DC-DC 加 LDO 的方式,但會(huì)帶來(lái)面積上的代價(jià)等,這些都需要綜合考慮。 另外一個(gè)考慮是進(jìn)入 Sleep 模式后,時(shí)鐘的頻率的大小,是來(lái)自 RC OSC 或 OSC 32k 等。

上面兩方面確定之后,就需要考慮低功耗的模擬及數(shù)字電路設(shè)計(jì),對(duì)于模擬模塊來(lái)說(shuō),提供低功耗的 LDO 和時(shí)鐘及復(fù)位模塊直接決定于 Sleep 模式下的 MCU 功耗,LDO 作為供電模塊,雖然在 Sleep 模式下驅(qū)動(dòng)電流很小,但其本身的功耗要盡可能的小,LDO 的參考 Bandgap 也同樣需要低功耗的設(shè)計(jì),一般情況下,Sleep 模式對(duì) LDO 的電壓精度要求不高,所以使得低功耗的設(shè)計(jì)成為可能。時(shí)鐘模塊需要結(jié)合系統(tǒng)定義,確定低功耗模式下是提供精準(zhǔn)的 OSC 32k 時(shí)鐘還是 RC OSC 的時(shí)鐘就可以滿足要求。另外模擬也需要提供 Reset 模塊來(lái)監(jiān)控外部電源的情況,如果電源電壓太低,也需要及時(shí)輸出相應(yīng)的指示信號(hào)。

對(duì)于低功耗模擬電路來(lái)說(shuō),從圖 9(gm/Id 圖)[3]中可以看到,如果模擬電路工作在低功耗區(qū)域,則模擬模塊需要工作在亞閾值區(qū)。亞閾值區(qū)模擬 MOS 管的電流和 VGS 的關(guān)系如式(2),VGS 輸入非常接近 Vth。在亞閾值區(qū)間,MOS 管的電流和 VGS 成指數(shù)關(guān)系[4]。

Id=Is×eVGS/(n×KT/q)(2)

對(duì)于數(shù)字電路的模塊,進(jìn)入 Sleep 模式后,常開(kāi)的邏輯電路一般對(duì)于時(shí)序要求不高,可以采用適當(dāng)降低其供電電壓來(lái)降低功耗,采用盡可能低的時(shí)鐘來(lái)保持一定的工作狀態(tài)。另外一個(gè)非常重要的模塊是 RAM 的設(shè)計(jì),RAM 在 Sleep 模式后,一部分會(huì) power down。另外一部分電路需要處于保持模式,來(lái)存儲(chǔ)一定的數(shù)據(jù),既不會(huì)讀也不會(huì)進(jìn)行寫(xiě)操作,只要保持狀態(tài)即可。而 RAM 的電流占到數(shù)字電流很大的比列,通常采用的 RAM 功耗降低的方法有降低 RAM 的工作電壓或采用特殊結(jié)果的 RAM 電路來(lái)降低功耗。

4 結(jié)語(yǔ)

MCU 的低功耗設(shè)計(jì)是 MCU 芯片非常核心的技術(shù),也是各家 MCU 進(jìn)行性能指標(biāo)對(duì)比最關(guān)鍵的一個(gè)環(huán)節(jié)。在 MCU 的低功耗設(shè)計(jì)中,涉及從芯片工藝﹑系統(tǒng)設(shè)計(jì)到模擬及數(shù)字實(shí)現(xiàn)的方方面面。隨著物聯(lián)網(wǎng)應(yīng)用的興起,對(duì)低功耗的需求也會(huì)越來(lái)越多,本文提到的幾個(gè)關(guān)鍵的低功耗技術(shù)是一些比較通用的設(shè)計(jì)方法,未來(lái)也會(huì)有更多低功耗架構(gòu)的電路及方法出現(xiàn),但不論怎樣,低功耗的需求一定是和應(yīng)用相關(guān)的——沒(méi)有最低,只有最合適的。

-

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423156 -

集成電路

+關(guān)注

關(guān)注

5387文章

11530瀏覽量

361643 -

單片微處理器

+關(guān)注

關(guān)注

0文章

3瀏覽量

6532

原文標(biāo)題:一種低功耗 MCU 芯片的設(shè)計(jì)方法

文章出處:【微信號(hào):appic-cn,微信公眾號(hào):集成電路應(yīng)用雜志】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

物聯(lián)網(wǎng)學(xué)習(xí)路線來(lái)啦!

低功耗SOC芯片的優(yōu)勢(shì)

物聯(lián)網(wǎng)系統(tǒng)中常用的低功耗自組網(wǎng)無(wú)線傳輸方案(三)_藍(lán)牙芯片篇

物聯(lián)網(wǎng)系統(tǒng)中TCP低功耗產(chǎn)品長(zhǎng)連接狀態(tài)下降低功耗功能的實(shí)現(xiàn)方案

引領(lǐng)智能未來(lái):英銳恩科技的國(guó)產(chǎn)低功耗單片機(jī)ENMCU

物聯(lián)網(wǎng)系統(tǒng)中音頻方案的“大腦”_語(yǔ)音芯片

國(guó)產(chǎn)化低功耗低延時(shí)廣覆蓋物聯(lián)網(wǎng)無(wú)線通訊方案_LAKI芯片

論述RISC-C在IOT領(lǐng)域的發(fā)展機(jī)會(huì)

低功耗藍(lán)牙模塊輕松實(shí)現(xiàn)智能防丟器

隨著非車(chē)規(guī)器件在汽車(chē)上泛濫FPGA會(huì)不會(huì)越來(lái)越多的出現(xiàn)在汽車(chē)上?

嵌入式會(huì)越來(lái)越卷嗎?

泰凌微電子推出超低功耗多協(xié)議物聯(lián)網(wǎng)無(wú)線SoC芯片TLSR925x

什么是非蜂窩物聯(lián)網(wǎng)芯片?非蜂窩物聯(lián)網(wǎng)芯片的使用場(chǎng)景

數(shù)據(jù)透?jìng)鬟x擇低功耗WiFi模塊還是選擇低功耗藍(lán)牙模塊?

物聯(lián)網(wǎng)應(yīng)用的興起 對(duì)芯片低功耗的需求會(huì)越來(lái)越多

物聯(lián)網(wǎng)應(yīng)用的興起 對(duì)芯片低功耗的需求會(huì)越來(lái)越多

評(píng)論