討論在標(biāo)準(zhǔn) 0.18μm CMOS 邏輯平臺上加入一次性編程單元(OTP Cell)后,工藝所面臨的問題。由于 OTP Cell 的設(shè)計尺寸遠(yuǎn)小于 0.18μm 技術(shù)代的設(shè)計要求,導(dǎo)致用傳統(tǒng)工藝對 OTP Cell 中具有高縱橫比的間距進(jìn)行填充時,會出現(xiàn)空洞。該空洞貫通前后接觸孔(CT),使得后續(xù)在沉積 TiN 時,TiN 會殘留在空洞側(cè)壁上,使相鄰接觸孔短路,從而導(dǎo)致 OTP 失效。為了解決這個問題,從多個方面進(jìn)行了方案設(shè)計,包括硼磷硅玻璃(BPSG)中硼(B)和磷(P)的濃度,BPSG 的厚度,回流溫度以及在 BPSG 之前先沉積一層高密度等離子體氧化物(HDP USG)。實驗結(jié)果表明,只有在 BPSG 之前先沉積一層 HDP USG 的工藝方案才是有效的,才可以消除空洞,從而消除 TiN 殘留物。同時,器件性能不受影響,并實現(xiàn)了高良率。

1 引言

在集成電路工藝中,0.18μm 制程作為一種低成本工藝制程,目前還是被大量、廣泛運用于制造一些集成電路產(chǎn)品,尤其是一些中低端產(chǎn)品或?qū)€寬尺寸不是很敏感的領(lǐng)域如汽車電子。通常的 0.18μm 制程,接觸孔 CT(Contact)的形成工藝是,首先,生長一層刻蝕終止層(Etching Stop Layer),接著沉積摻有元素硼(B)和磷(P)的硼磷硅玻璃 BPSG,在高溫回流工藝后再沉積一層等離子體增強(qiáng)型氧化層(PE-TEOS),然后用化學(xué)機(jī)械拋光法進(jìn)行表面平整化,接著進(jìn)行干式刻蝕形成接觸孔。緊接著在接觸孔四周側(cè)壁上沉積黏結(jié)層 Ti/TiN,隨后填埋鎢(W)作為連接導(dǎo)體。這對標(biāo)準(zhǔn)的 0.18 μm 技術(shù)代設(shè)計準(zhǔn)則來說,工藝很成熟,不會有任何問題,但如果在這個技術(shù)平臺上加入一些其他的器件或工藝如 OTP(One Time Program)工藝,為了降低成本,提高產(chǎn)品競爭力,我們通常超越設(shè)計準(zhǔn)則,使得這些器件或 OTP 尺寸做的非常小,不可避免地造成高縱橫比間距,這會帶來一些工藝上的問題。本論文討論的就是在 0.18μm 通用平臺的基礎(chǔ)上加入一個尺寸非常小的 OTP 單元后工藝上所面臨的問題和挑戰(zhàn),以及相應(yīng)的解決方案。

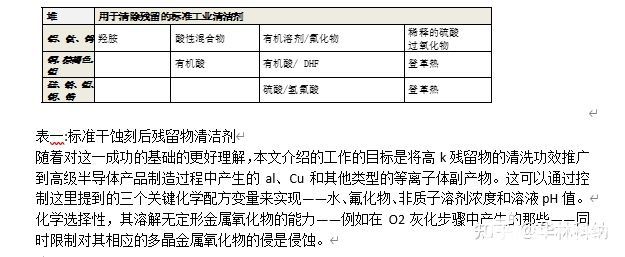

圖 1 為我們使用的 OTP Cell,覆蓋浮柵的相鄰 SAB(金屬硅化物阻擋層)的間距非常小,只有 0.28μm,而標(biāo)準(zhǔn)的 0.18μm 工藝平臺,相鄰 SAB 的最小間距為 0.42μm。這么小的間距,加上浮柵高度和特別為 OTP 工藝加厚的 SAB 厚度,形成了很高的縱橫比間距。如果在刻蝕終止層上直接沉積 BPSG,很容易導(dǎo)致間距頂已被 BPSG 合攏,但下面還沒填實,出現(xiàn)空洞,這些空洞會前后貫通,盡管接下來有 BPSG的高溫回流工藝,但該回流是一個微流動,有別于通常的流體流動,所以,這個空洞不會因為 BPSG 的高溫回流而消失。接觸孔側(cè)壁在形成 Ti/TiN 黏結(jié)層的過程中,采用的是化學(xué)氣相沉積(CVD)的形成方式,所以 TiN 同時也會在空洞的側(cè)壁上沉積,由于空洞是前后貫通的,導(dǎo)致其側(cè)壁上的 TiN 貫通前后接觸孔而造成 Bit Line 短路,從而使芯片失效,如圖 2 所示,其中 SEM 俯視圖顯示前后接觸孔被連起來了,TEM 剖面圖所示空洞側(cè)壁上有殘留物,SMIS 表明此殘留物含 Ti 和 N 元素,與接觸孔側(cè)壁上的黏結(jié)層是同一種物質(zhì),即 TiN。

2 實驗方案

為了解決高縱橫比間距下的 TiN 殘留物問題,我們從多個角度出發(fā),改變工藝條件進(jìn)行了研究,首先從物理層面確定工藝條件,然后從器件電性和芯片良率層面進(jìn)一步驗證該工藝條件的有效性。我們所用的樣品都取自于全工藝流程的晶圓,采用的是在標(biāo)準(zhǔn)的 0.18μm CMOS 工藝上加入 OTP 制程。這些晶圓除了變化的工藝步驟外,其他的工藝完全相同。表 1 所列為實驗方案,其中方案編號 #1 為當(dāng)前工藝,作為對比的控制組;我們分別從 BPSG 中摻雜的 B和 P 濃度,BPSG 厚度,BPSG 回流溫度設(shè)計了編號 #2~#4 的實驗方案,其目的是增加 BPSG的流動性,使其回流過程中填補(bǔ)其沉積時出現(xiàn)的空洞,為了控制整個厚度,以減少對后續(xù)化學(xué)機(jī)械研磨(CMP)和接觸孔刻蝕工藝的影響,我們同時調(diào)整了方案編號 #3 和 #4 中 TEOS 的厚度。方案編號#5 在 BPSG 之前,我們先沉積了一層高密度等離子體氧化物(HDP USG),這主要是考慮了 HDP 卓越的填洞能力,尤其在高縱橫比間距的情況下。

3 實驗結(jié)果與討論

表 2 為實驗結(jié)果,圖 3 為相應(yīng)的 SEM 俯視圖,在所設(shè)計的方案中只有方案 #5 才能實現(xiàn)無 TiN 殘留物的目標(biāo)。表中“嚴(yán)重程度”表示殘留物的多少,最嚴(yán)重的情況是前后兩個接觸孔已被空洞側(cè)壁上的 TiN 殘留物短路了。BPSG 的回流特性對摻雜的 B 和 P 的濃度非常敏感[1],濃度稍有升高,回流溫度降低明顯,BPSG 的回流效果就越好,但濃度并非越高越好,P 高了,會影響 BPSG 的穩(wěn)定性和可靠性,B 高了抗潮能力會減弱。在標(biāo)準(zhǔn) 0.18μm 工藝中,B/P 通常在 4.6%/3.5% 左右。BPSG 的回流性能還跟溫度有關(guān),溫度越高,回流性能越好。在方案 #2 中,B/P 濃度增加到 4.9%/4.4%,回流溫度提升至 700℃,雙管齊下改善回流性能,在回流平坦化過程中使空洞消失,從而消除 Ti N殘留物,然而,實驗結(jié)果表明,盡管本方案較當(dāng)前工藝 #1 有改善,但仍然存在 TiN 殘留物。而且,器件性能因過高的回流溫度而徹底改變,閾值電壓 Vt 相較當(dāng)前工藝 #1,NMOS漂了 25%,而 PMOS 更是漂了 40%。方案 #3,BPSG 的厚度從 2 k 增加到 3 k,以確保 BPSG 在回流平坦化過程中有足夠的量來填充空洞使其消失。從而消除 TiN 殘留物,但實驗結(jié)果顯示,TiN 殘留物狀況未見明顯改善,說明空洞依然存在。為了改善回流特性,同時盡量減少回流溫度對前端器件性能的影響,方案 #4 在方案 #3 的基礎(chǔ)上,回流溫度略微增加至 650℃。同樣,該方案無法消除空洞,TiN 殘留物也未見其明顯好轉(zhuǎn)。以上方案表明,通過 BPSG 厚度,B/P 濃度以及回流溫度來解決 TiN 殘留物,收效甚微,必須另辟蹊徑。

眾所周知,用高密度等離子體法(HDP)沉積氧化物能實現(xiàn)非常好的臺階覆蓋(Step coverage),特別適合填充高縱橫比間隙,具有卓越的填洞能力[2]。在 HDP 氧化物形成過程中,通過調(diào)節(jié)其刻蝕(Etch)和沉積(Deposition)之比來實現(xiàn)其最佳的填充效果,達(dá)到消除空洞的目標(biāo)。然而,HDP 中含有大量的離子,同時,通過濺射(Sputter)來實現(xiàn)的刻蝕,也能產(chǎn)生大量的電子、缺陷,這些離子、電子、缺陷對 OTP 的數(shù)據(jù)保持(Data Retention)是有害的。為了消除空洞,我們在方案 #5 中用了 2 k 的 HDP 氧化物,該 HDP 氧化物先于 BPSG 沉積。在沉積時,特別優(yōu)化了刻蝕和沉積之比,以盡量減少離子、電子、缺陷對 Data Retention 的影響。另外,在該方案中,我們把 BPSG 增加到 3 k,同時降低 TEOS 的厚度到 6 k,以保持總厚度不變。

實驗結(jié)果表明,空洞沒有了,空洞側(cè)壁上的 TiN 殘留物也隨之消失了,如圖 3 所示。在電性層面,我們對晶圓進(jìn)行了測試,結(jié)果顯示,無論是 MOS 器件的性能(Ids,Vt 等),還是接觸孔的電阻值,都與當(dāng)前工藝一致。良率方面,由于最主要的 Data Retention 性能未見下降,所以得到了很高的良率。這充分說明,方案 #5 是有效的。用該方案作為我們生產(chǎn)標(biāo)準(zhǔn)后,從出貨的幾十萬片晶圓數(shù)據(jù)來看,再一次證明該方案是非常成功的。

4 結(jié)語

本文討論的是標(biāo)準(zhǔn) 0.18μm CMOS 邏輯平臺上引入了超越規(guī)則的 OTP Cell 后,工藝所面臨的問題。用傳統(tǒng)工藝對 OTP Cell 中的高縱橫比間距進(jìn)行填充時,會留下貫通前后接觸孔的空洞,在接觸孔沉積 TiN 時,TiN 同樣會殘留在空洞側(cè)壁上,使相鄰接觸孔短路,從而導(dǎo)致 OTP 失效。為了解決這個問題,我們從 BPSG 中 B/P 的濃度,BPSG 厚度,回流溫度,以及在 BPSG 之前先沉積一層 HDP USG 的方式進(jìn)行了多個方案設(shè)計。實驗結(jié)果表明,只有在 BPSG 之前先沉積一層 HDP USG 的工藝方案才是有效的,才可以消除 TiN 殘留物,同時,器件性能不受影響,并實現(xiàn)了高良率,以此為量產(chǎn)工藝條件生產(chǎn)出的幾十萬片晶圓數(shù)據(jù)進(jìn)一步驗證了該方案的有效性和可靠性。

-

集成電路

+關(guān)注

關(guān)注

5387文章

11530瀏覽量

361645 -

Tin

+關(guān)注

關(guān)注

0文章

4瀏覽量

7264

原文標(biāo)題:高縱橫比間距下 TiN 殘留物的解決方案

文章出處:【微信號:appic-cn,微信公眾號:集成電路應(yīng)用雜志】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

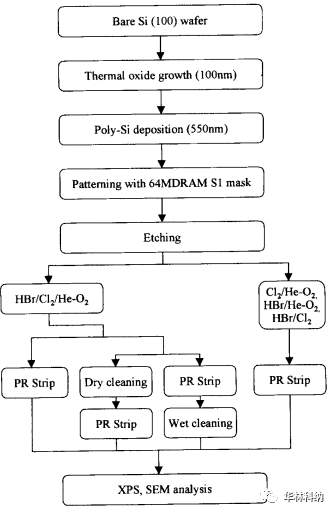

多晶硅蝕刻殘留物的的形成機(jī)理

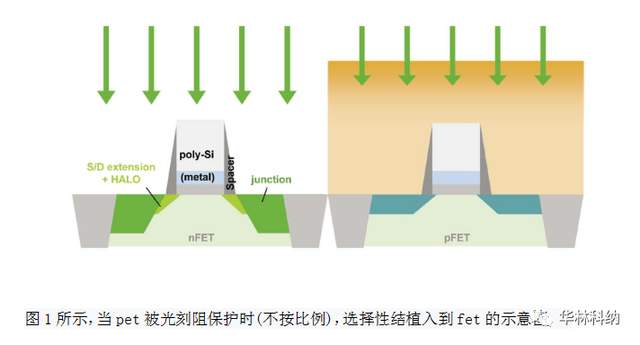

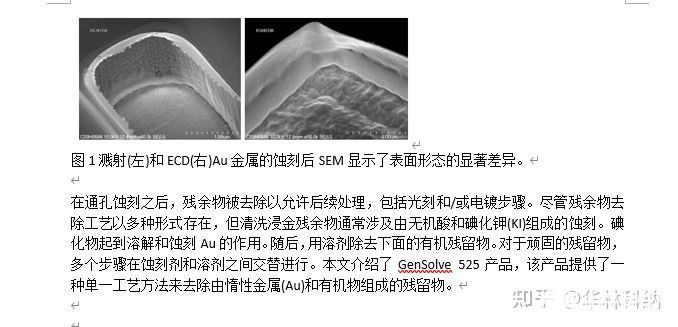

蝕刻后殘留物和光刻膠的去除方法

【已解決】FPGA的TQFP封裝焊接后引腳間留有白色松香殘留物...

U1252A交流電壓殘留物

一文看懂污染物殘留物對PCB點焊的影響

印刷電路板上焊劑殘留物會造成哪些危害性

波峰焊工藝中的焊點殘留物的形成原因說明

農(nóng)藥殘留物檢測儀可快速檢測出農(nóng)藥殘留問題

使用濕化學(xué)物質(zhì)去除光刻膠和殘留物

刻蝕后殘留物的去除方法

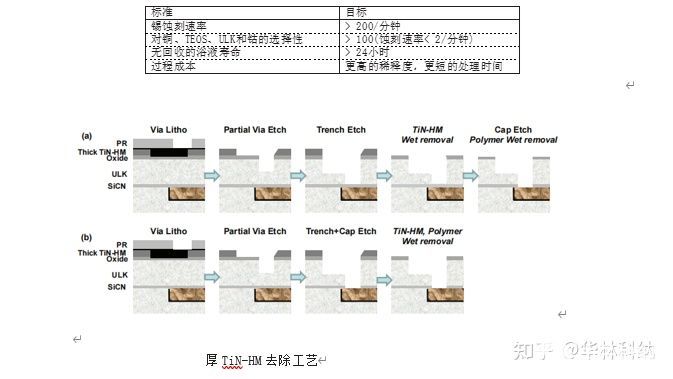

TiN硬掩模濕法去除工藝的介紹

適用于清潔蝕刻后殘留物的定制化學(xué)成分(1)

PCBA殘留物的影響及清洗,助焊劑殘留物怎么樣清除

焊后錫膏殘留物帶來的危害有哪些?

錫膏焊接后殘留物如何清洗?

集成電路 | 高縱橫比間距下 TiN 殘留物的解決方案

集成電路 | 高縱橫比間距下 TiN 殘留物的解決方案

評論