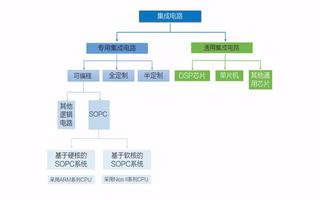

根據IP使用的劃分,IP建立者可按下列三種形式設計IP:可再用、可重定目標以及可配置。可再用IP是著眼于按各種再使用標準定義的格式和快速集成的要求而建立的,便于移植,更重要的是有效集成。可重定目標IP是在充分高的抽象級上設計的,因而可以方便地在各種工藝與結構之間轉移。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603017 -

開發板

+關注

關注

25文章

5033瀏覽量

97378 -

IP核

+關注

關注

4文章

327瀏覽量

49485

發布評論請先 登錄

相關推薦

【鋯石A4 FPGA試用體驗】鋯石科技-A4 FPGA開發板開箱鑒賞-您將得到的是一門技術

全家福開啟說明書與光盤包裝盒,包含以下附件:鋯石科技-A4 FPGA開發板引導手冊一本鋯

發表于 07-29 16:33

【鋯石A4 FPGA試用體驗】初識鋯石A4 FPGA開發板

` 本帖最后由 jinglixixi 于 2017-8-3 11:14 編輯

期待中的鋯石A4 FPGA開發板終于如期而至了,欣喜中快速

發表于 08-03 11:12

【鋯石A4 FPGA試用體驗】鋯石A4智能家庭娛樂系統-結項報告

` 本帖最后由 超級開發板 于 2017-10-8 10:45 編輯

今天,我們來進行基于鋯石A4 FPGA

發表于 09-28 08:58

鋯石FPGA A4_Nano開發板視頻:LED的IP核應用

利用IP核設計電子系統,引用方便,修改基本元件的功能容易。具有復雜功能和商業價值的IP核一般具有知識產權,盡管IP

鋯石FPGA A4_Nano開發板視頻:DA外設IP核定制

IP核有三種不同的存在形式:HDL語言形式,網表形式、版圖形式。分別對應我們常說的三類IP內核:軟核、固核和硬核。這種分類主要依據產品交付的

鋯石FPGA A4_Nano開發板視頻:定制最基本LED的IP核

IP主要分為軟IP、固IP和硬IP。軟IP是用Verilog/VHDL等硬件描述語言描述的功能塊,但是并不涉及用什么具體電路元件實現這些功能

鋯石FPGA A4_Nano開發板視頻:什么是Qsys?如何構建一個Qsys系統?

視頻中進一步介紹了Nios II處理器的體系結構、Qsys豐富多彩的內置IP,以及Avalon總線接口規范,然后我們又以Avalon總線接口規范為基礎,進一步定制了開發板所有外設的

鋯石FPGA A4_Nano開發板視頻:VGA外設的IP核定制

IP核有三種不同的存在形式:HDL語言形式,網表形式、版圖形式。分別對應我們常說的三類IP內核:軟核、固核和硬核。這種分類主要依據產品交付的

鋯石FPGA A4_Nano開發板視頻:紅外IP核的定制

鋯石FPGA A4_Nano開發板視頻:紅外IP核的定制

評論