針對普通時鐘系統存在著限制時鐘頻率的弊端,人們設計了一種新的時序系統,稱之為源同步時序系統。它最大的優點就是大大提升了總線的速度,在理論上信號的傳送可以不受傳輸延遲的影響。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

時鐘

+關注

關注

10文章

1733瀏覽量

131451 -

總線

+關注

關注

10文章

2878瀏覽量

88052 -

時序

+關注

關注

5文章

387瀏覽量

37318

發布評論請先 登錄

相關推薦

對邊沿對齊源同步輸入端口的約束

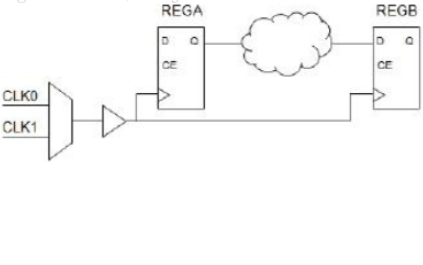

相對于FPGA來說,邊沿對齊源同步輸入端口,指的是FPGA同時接收外部器件傳過來的數據和時鐘信號,并且用接收到的時鐘信號去鎖存傳過來的數據。模型如下圖所示:對此模型進行約束,分下面幾個步驟

發表于 12-25 14:28

ETD第14期:SDR源同步接口時序約束方法

。本次沙龍主要介紹怎樣通過Quartus? II軟件中的TimeQuest時序分析器來約束并分析單倍數據速率源同步接口。會議焦點 1、源

發表于 12-31 14:21

FPGA沙龍:SDR源同步接口時序約束方法沙龍精彩內容回顧!

草叢中兩只花,今天的沙龍現場我們還迎來了兩位美女工程師,有木有感覺本次沙龍的氛圍更加輕松了呢~~~!張工正在為大家介紹SDR源同步接口時序約束,學會這個保證你貫穿全部

發表于 12-31 14:25

FPGA實戰演練邏輯篇55:VGA驅動接口時序設計之2源同步接口

可以分析一下這個接口的時序要求,然后對其進行約束。這個輸出的信號,其實是很典型的源同步接口,它的時鐘和數據都是由FPGA來驅動產生的。一般的源

發表于 07-29 11:19

基于Cadence的源同步時序仿真

根據源同步的一些基本問題,在Cadence仿真環境下,對源同步時序進行仿真,仿真結果表明,設計能滿足噪聲容限和過沖,仿真后的可知數據線和時間

發表于 05-29 15:26

?0次下載

FPGA時序約束的常用指令與流程詳細說明

說到FPGA時序約束的流程,不同的公司可能有些不一樣。反正條條大路通羅馬,找到一種適合自己的就行了。從系統上來看,同步時序

發表于 01-11 17:46

?13次下載

時序約束步驟:系統同步與源同步

時序約束步驟:系統同步與源同步

評論