- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:60fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

SignalTap II全稱SignalTap II Logic Analyzer是第二代系統(tǒng)級(jí)調(diào)試工具,可以捕獲和顯示實(shí)時(shí)信號(hào),觀察在系統(tǒng)設(shè)計(jì)中的硬件和軟件之間的互相作用。Quartus II軟件可以選擇要捕獲的信號(hào)、開(kāi)始捕獲的時(shí)間,以及要捕獲多少數(shù)據(jù)樣本。還可以選擇時(shí)間數(shù)據(jù)從器件的存儲(chǔ)器塊通過(guò)JTAG端口傳送至SignalTap II Logic Analyzer,還是至I/O引腳以供外部邏輯分析儀或示波器使用。將實(shí)時(shí)數(shù)據(jù)提供給工程師幫助debug。

-

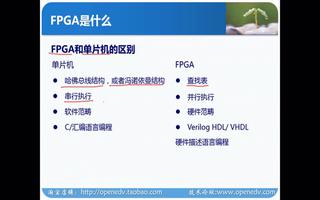

FPGA

+關(guān)注

關(guān)注

1644文章

22007瀏覽量

616347 -

示波器

+關(guān)注

關(guān)注

113文章

6633瀏覽量

188644 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7643瀏覽量

166811

發(fā)布評(píng)論請(qǐng)先 登錄

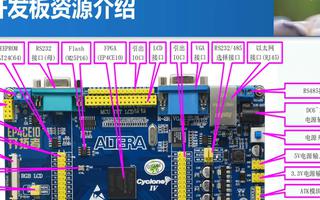

【正點(diǎn)原子FPGA連載】第十二章 動(dòng)態(tài)數(shù)碼管顯示實(shí)驗(yàn)

分享正點(diǎn)原子FPGA開(kāi)發(fā)板全套資料

正點(diǎn)原子開(kāi)拓者FPGA開(kāi)發(fā)板資料連載第二十一章 VGA圖片顯示實(shí)驗(yàn)

正點(diǎn)原子開(kāi)拓者FPGA開(kāi)發(fā)板資料連載第四十三章 以太網(wǎng)通信實(shí)驗(yàn)(2)

正點(diǎn)開(kāi)拓者FPGA開(kāi)發(fā)板使用問(wèn)題

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:uC/GUI圖片/數(shù)字顯示實(shí)驗(yàn)

正點(diǎn)原子開(kāi)拓者FPGA視頻:Modelsim軟件的使用

正點(diǎn)原子開(kāi)拓者FPGA視頻:Quartus II軟件的使用

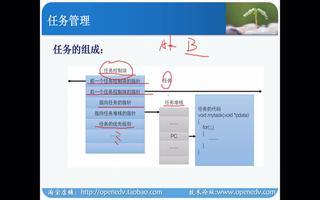

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:uCOS II任務(wù)管理與時(shí)間管理(2)

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:自定義IP核之?dāng)?shù)碼管(2)

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:PIO按鍵控制LED

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:PIO IRQ

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:Hello World

評(píng)論