- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:61fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

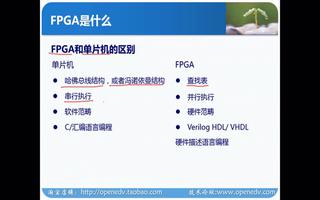

Quartus II design是唯一一個包括以timing closure 和 基于塊的設計流為基本特征的programmable logic device (PLD)的軟件。 Quartus II 設計軟件改進了性能、提升了功能性、解決了潛在的設計延遲等,在工業領域率先提供FPGA與mask-programmed devices開發的統一工作流程。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1638文章

21859瀏覽量

609829 -

quartus

+關注

關注

17文章

171瀏覽量

74949

發布評論請先 登錄

相關推薦

Quatus使用Nios2時生成.sof文件帶有time limited

最近購買了發燒友的開拓者fpga開發板。目前學習Nios2。以hello world例程為例,完全編譯后生成“qsys_hello_world

發表于 05-28 01:19

【正點原子FPGA連載】第十二章 動態數碼管顯示實驗

`1)實驗平臺:正點原子開拓者FPGA開發板2)平臺購買地址:https://item.taobao.com/item.htm?id=5797492098202)全套實驗源碼+手冊+

發表于 06-15 22:54

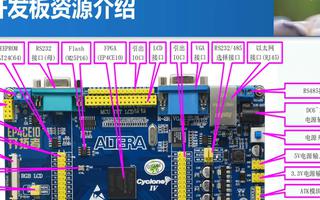

分享正點原子FPGA開發板全套資料

本帖最后由 100dongdong 于 2020-5-16 23:48 編輯

正點原子FPGA開拓者開發板,Intel(Altera) FPG

發表于 05-16 23:35

正點原子開拓者FPGA開發板資料連載第二十三章RGBTFT-LCD字符顯示

1)實驗平臺:正點原子開拓者FPGA 開發板2)摘自《開拓者FPGA開發指南》關注官方微信號公眾

發表于 08-08 11:03

正點開拓者FPGA開發板使用問題

求問各位大佬,剛剛入門正點開拓者FPGA開發板,用板載pcf8591采集信號發生器單一頻率正弦波,再用ip核做fft,結果和matlab上fft不一樣,請問是怎么回事呢?

發表于 01-04 09:34

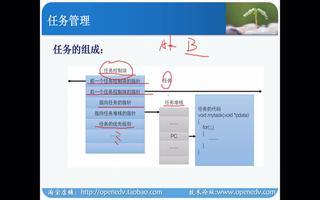

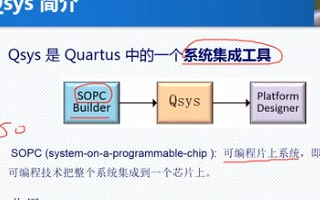

正點原子開拓者FPGA Qsys視頻:uCOS II任務管理與時間管理(2)

該課程是正點原子團隊編寫,詳細講解了quartus中的qsys。也可以從我頭像點進去看FPGA verilog相關的視頻。

評論