乘法器可以通過使用一系列計算機算數(shù)技術來實現(xiàn)。乘法器不僅作為乘法、除法、乘方和開方等模擬運算的主要基本單元,而且還廣泛用于電子通信系統(tǒng)作為調制、解調、混頻、鑒相和自動增益控制;另外還可用于濾波、波形形成和頻率控制等場合,因此是一種用途廣泛的功能電路。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603010 -

計算機

+關注

關注

19文章

7488瀏覽量

87854 -

乘法器

+關注

關注

8文章

205瀏覽量

37043

發(fā)布評論請先 登錄

相關推薦

#硬聲創(chuàng)作季 #FPGA 玩轉FPGA-12 BJ-EPM240實驗5-乘法器設計實驗-1

fpga乘法器EPMepM240

水管工

發(fā)布于 :2022年10月29日 12:27:43

#硬聲創(chuàng)作季 #FPGA 玩轉FPGA-12 BJ-EPM240實驗5-乘法器設計實驗-2

fpga乘法器EPMepM240

水管工

發(fā)布于 :2022年10月29日 12:28:04

怎么設計基于FPGA的WALLACETREE乘法器?

在數(shù)字信號處理中,乘法器是整個硬件電路時序的關鍵路徑。速度和面積的優(yōu)化是乘法器設計過程的兩個主要考慮因素。由于現(xiàn)代可編程邏輯芯片FPGA的集成度越來越高,及其相對于ASIC設計難度較低和產(chǎn)品設計

發(fā)表于 09-03 07:16

基于FPGA的WALLACE TREE乘法器設計

本文著重介紹了一種基于WALLACETREE優(yōu)化算法的改進型乘法器架構。根據(jù)FPGA內部標準獨特slice單元,有必要對WALLACE TREE部分單元加以研究優(yōu)化,從而讓在FPGA的乘法器

發(fā)表于 11-17 10:50

?5320次閱讀

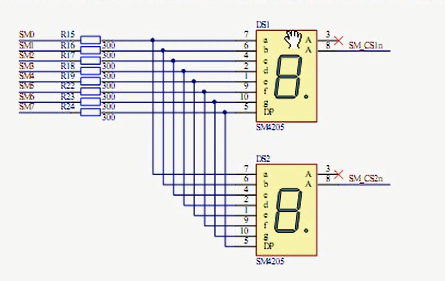

FPGA視頻教程之使用BJ-EPM240學習板進行數(shù)碼管顯示實驗的資料說明

本文檔的主要內容詳細介紹的是FPGA視頻教程之使用BJ-EPM240學習板進行數(shù)碼管顯示實驗的資

發(fā)表于 02-28 10:35

?5次下載

FPGA視頻教程之BJ-EPM240學習板的詳細資料介紹

本文檔的主要內容詳細介紹的是FPGA視頻教程之BJ-EPM240學習板的詳細資料說明免費下載,BJ-EP

發(fā)表于 03-01 11:35

?20次下載

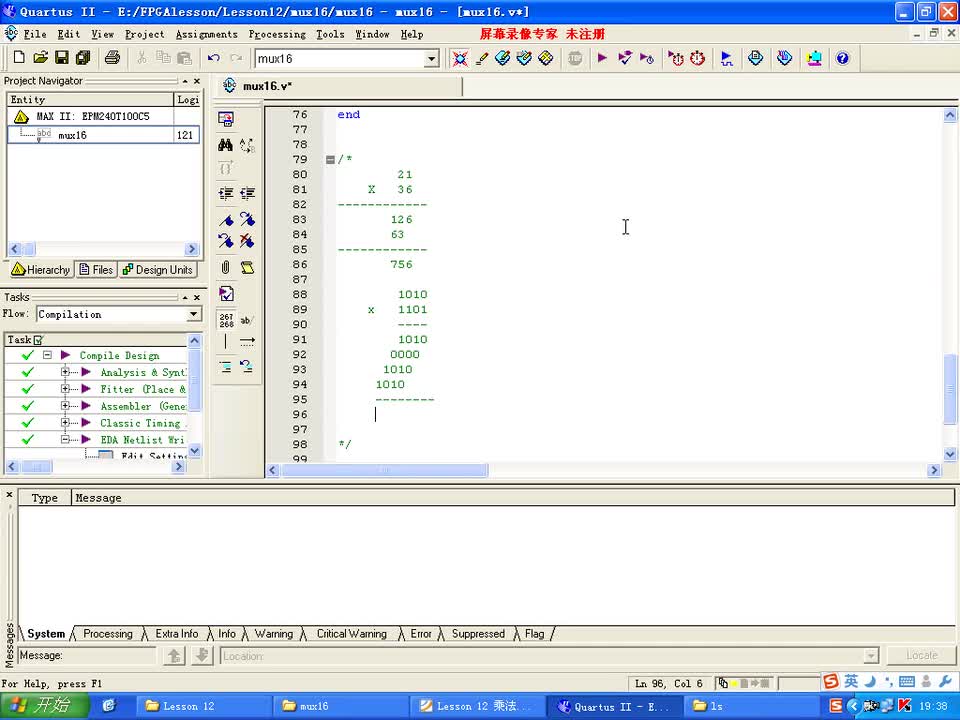

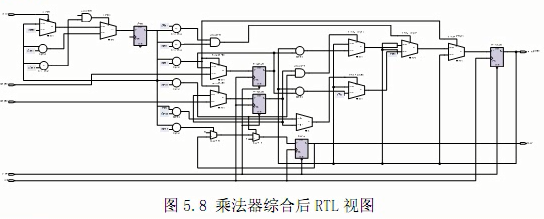

FPGA視頻教程之BJ-EPM240學習板乘法器設計實驗的詳細資料說明

乘法器是眾多數(shù)字系統(tǒng)中的基本模塊。從原理上說它屬于組合邏輯范疇:但從工程實際設計上來說,它往往會利用時序邏輯設計的方法來實現(xiàn),屬于時序邏輯的范疇。

發(fā)表于 03-04 17:06

?1次下載

BJ-EPM240學習板介紹

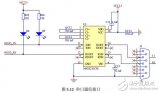

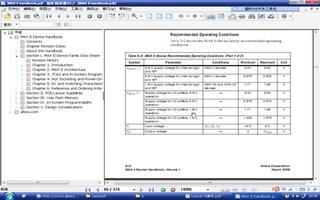

主芯片使用的是Altera公司的MAXII系列EPM240T100C5,該芯片有240個邏輯單元,等效宏單元192個,資源比較豐富,內有8KbitFlash的存儲空間。

BJ-EPM240學習板之Johnson.計數(shù)器實驗

本視頻主要內容詳細介紹的是FPGA視頻教程之BJ-EPM240學習板計數(shù)器

BJ-EPM240學習板之乘法器設計實驗

乘法器是眾多數(shù)字系統(tǒng)中的基本模塊。從原理上說它屬于組合邏輯范疇:但從工程實際設計上來說,它往往會利用時序邏輯設計的方法來實現(xiàn),屬于時序邏輯的范疇。

BJ-EPM240學習板:乘法器設計實驗

乘法器是模擬式電子式電能表的重要組成部分,也是電能表計量誤差的最主要來源。對時分割乘法器在諧波條件下的計量誤差進行了定量的研究與分析,根據(jù)時分割乘法器的工作原理,推導其在諧波條件下計量誤差的理論表達式,并通過仿真計算驗證計量誤差

FPGA視頻教程:BJ-EPM240學習板-乘法器設計實驗

FPGA視頻教程:BJ-EPM240學習板-乘法器設計實驗

評論