聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603976 -

布線

+關注

關注

9文章

772瀏覽量

84352 -

代碼

+關注

關注

30文章

4793瀏覽量

68701

發布評論請先 登錄

相關推薦

如何在不改變RTL代碼的情況下,優化FPGA HLS設計

用軟件從 C 轉化來的 RTL 代碼其實并不好理解。今天我們就來談談,如何在不改變 RTL 代碼的情況下,提升設計性能。 本項目所需應用與工具:賽靈思HLS、Plunify Cloud

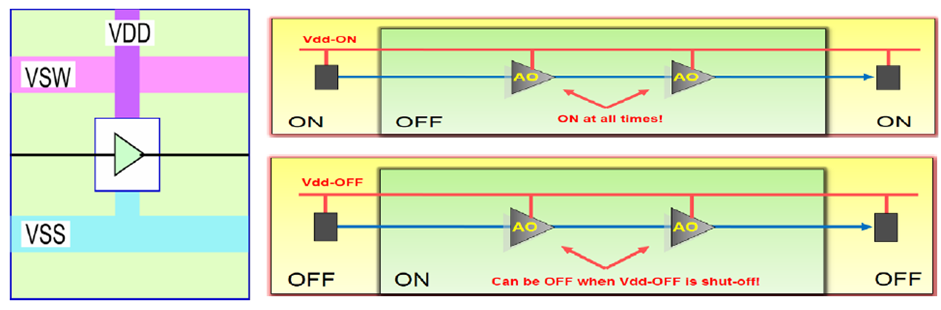

什么是always on buffer?什么情況下需要插always on buffer?

相比普通的buffer cell,always on buffer(AOB)有secondary always on pin,可以讓AOB即使在primary power off的情況下保持on的狀態;AOB在secondary

使用增量式編碼器,在PI參數不改變情況下,為什么MCSDK初始定位后轉速波動大?

使用增量式編碼器,第一次啟動時,轉速波動較大,然后第二次啟動轉速波動就平穩了,我想問一下,在PI參數不改變情況下,為什么MCSDK初始定位后轉速波動大?

發表于 03-20 06:03

有沒有什么辦法在不改變電源和功率的情況下來解決TPA311XD2失真的問題?

換了大電源之后就沒有失真了,有沒有什么辦法在不改變電源和功率的情況下來解決芯片失真的問題,謝謝!!!

發表于 10-25 08:34

AIC3106如何在不改變BCLK和LRCLK的情況下,能夠調好?

你好,請問:AIC3106現在配置為從設備、DAC采樣率為16K、數據寬度為32位。現在主設備給的BCLK是2048K,LRCLK為16K,播放現在有問題,如何在不改變BCLK和LRCLK的情況下,能夠調好?

發表于 10-28 07:06

在不改變內部程序的情況下,只想改變外部元件,如晶振等,怎樣才能讓實時時鐘加快,

在不改變內部程序的情況下,只想改變外部元件,如晶振等,怎樣才能讓實時時鐘加快,如用1秒的時間跳30秒?

發表于 05-16 17:55

不改變電路的情況下13003可以完全代換13001嗎?

不改變電路的情況下13002 -13003-13005可以完全代換13001嗎?我用新的充電器實驗了下13002-13003代換13001好像不太穩定,當時換上好似,充電10多分鐘開關管炸了,基本就是當時好使,一會就炸了,是不能

發表于 07-06 21:07

如何在負載不變的情況下 對電機的電流進行控制??

電機的電流與負載成正比,當負載增加到足以使電機發生堵轉時,電機的電流就會達到最大值。我想問一下,在這種情況下,如何在不改變負載的情況下,來減小電機的電流??

發表于 06-30 10:11

電機運行不正常,在不改變每轉線數的情況下,有什么辦法能夠解決這個情況?

驅動器控制電機,在每轉設置時,編碼器分辨率每轉線數比之前大一倍,電機運行不正常,在不改變每轉線數的情況下,有什么辦法能夠解決電機不正常的情況

發表于 07-24 10:36

請問CC1101不改變硬件電路可以頻段相互調頻么?

本帖最后由 人間煙火123 于 2018-5-18 15:59 編輯

CC1101在不改變硬件電路的情況下,可以通過軟件將315M和433M頻段相互調頻么?

發表于 05-15 02:59

什么情況下使用示波器

用于測量電壓、電流、頻率、相位差、調幅度。 在以下情況下使用示波器: 一次在最多四個信號上檢定信號穩定性 測量信號邊沿和電壓,評估定時余量,如建立時間/保持時間、傳播延遲 檢測瞬態問題,如毛刺、欠幅脈沖、亞穩定跳變

同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO各在什么情況下應用

同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO各在什么情況下應用? 1. 同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO在處理時序有明顯的區別。同步FIFO相對來說是較為

Python 在什么情況下才進行重試

為了避免由于一些網絡或等其他不可控因素,而引起的功能性問題。比如在發送請求時,會因為網絡不穩定,往往會有請求超時的問題。 這種情況下,我們通常會在代碼中加入重試的代碼。重試的代碼本身不

受控源什么情況下可看為電阻

受控源,又稱為非獨立源,是指其電壓或電流值受電路中其他部分的電壓或電流控制的電源。受控源在電路分析中具有重要的作用,其特性和行為與獨立源(如電池、發電機等)有所不同。在某些特定情況下,受控源可以看作

在不改變原來時序的情況下簡化部分代碼

在不改變原來時序的情況下簡化部分代碼

評論