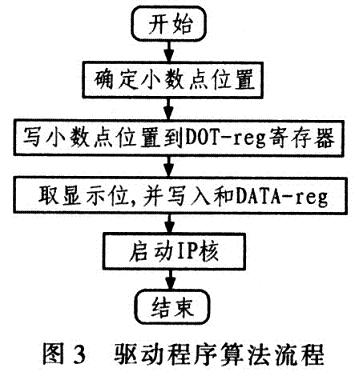

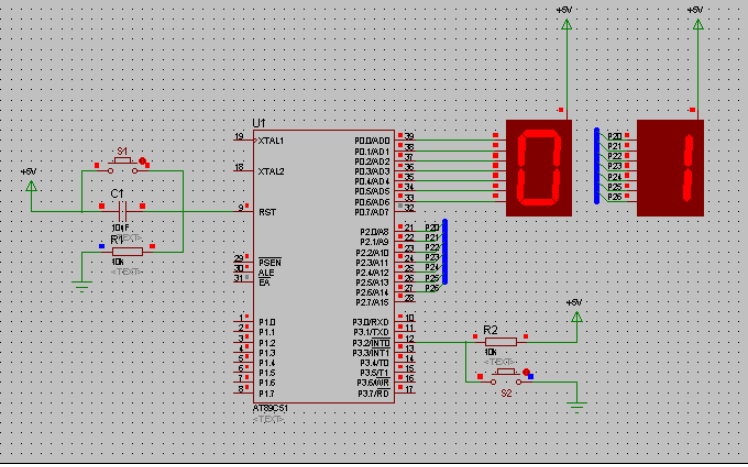

數碼管動態顯示接口是單片機中應用最為廣泛的一種顯示方式之一,動態驅動是將所有數碼管的8個顯示筆劃"a,b,c,d,e,f,g,dp"的同名端連在一起,另外為每個數碼管的公共極COM增加位選通控制電路,位選通由各自獨立的I/O線控制,當單片機輸出字形碼時,所有數碼管都接收到相同的字形碼,但究竟是哪個數碼管會顯示出字形,取決于單片機對位選通COM端電路的控制,所以我們只要將需要顯示的數碼管的選通控制打開,該位就顯示出字形,沒有選通的數碼管就不會亮。通過分時輪流控制各個數碼管的的COM端,就使各個數碼管輪流受控顯示,這就是動態驅動。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603016 -

單片機

+關注

關注

6035文章

44554瀏覽量

634681 -

數碼管

+關注

關注

32文章

1882瀏覽量

91064

發布評論請先 登錄

相關推薦

【正點原子FPGA連載】第十二章 動態數碼管顯示實驗

/1WzZfnb0gGPkthV7x_SrsKw 提取碼:vjpn4)對正點原子FPGA感興趣的同學可以加群討論:712557122點擊加入:5)關注正點

發表于 06-15 22:54

基于FPGA的8段數碼管動態顯示IP核設計

基于FPGA的8段數碼管動態顯示IP核設計

引言

數碼管可顯示簡單的字符和數字,由于其價格低廉、性能穩定、

發表于 02-03 10:03

?2389次閱讀

FPGA入門系列實驗教程之使用FPGA實現數碼管動態顯示的資料免費下載

實現開發板上 8 個數碼管動態顯示 0~7。通過這個實驗,掌握采用 Verilog HDL語言編程實現 7 段數碼管顯示譯碼器以及

發表于 06-12 16:32

?15次下載

正點原子開拓者FPGA:數碼管動態顯示實驗

正點原子開拓者FPGA:數碼管動態顯示實驗

評論