- Load:10.33 second

- Duration:1366 second

- Size:480x360

- Volume:0%

- Fps:60fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

乘法器是模擬式電子式電能表的重要組成部分,也是電能表計(jì)量誤差的最主要來(lái)源。對(duì)時(shí)分割乘法器在諧波條件下的計(jì)量誤差進(jìn)行了定量的研究與分析,根據(jù)時(shí)分割乘法器的工作原理,推導(dǎo)其在諧波條件下計(jì)量誤差的理論表達(dá)式,并通過(guò)仿真計(jì)算驗(yàn)證計(jì)量誤差量化表達(dá)式的準(zhǔn)確性。

-

仿真

+關(guān)注

關(guān)注

52文章

4252瀏覽量

135518 -

電能表

+關(guān)注

關(guān)注

5文章

790瀏覽量

33833 -

乘法器

+關(guān)注

關(guān)注

9文章

211瀏覽量

37888

發(fā)布評(píng)論請(qǐng)先 登錄

#硬聲創(chuàng)作季 #FPGA 玩轉(zhuǎn)FPGA-12 BJ-EPM240實(shí)驗(yàn)5-乘法器設(shè)計(jì)實(shí)驗(yàn)-1

#硬聲創(chuàng)作季 #FPGA 玩轉(zhuǎn)FPGA-12 BJ-EPM240實(shí)驗(yàn)5-乘法器設(shè)計(jì)實(shí)驗(yàn)-2

乘法器的基本概念

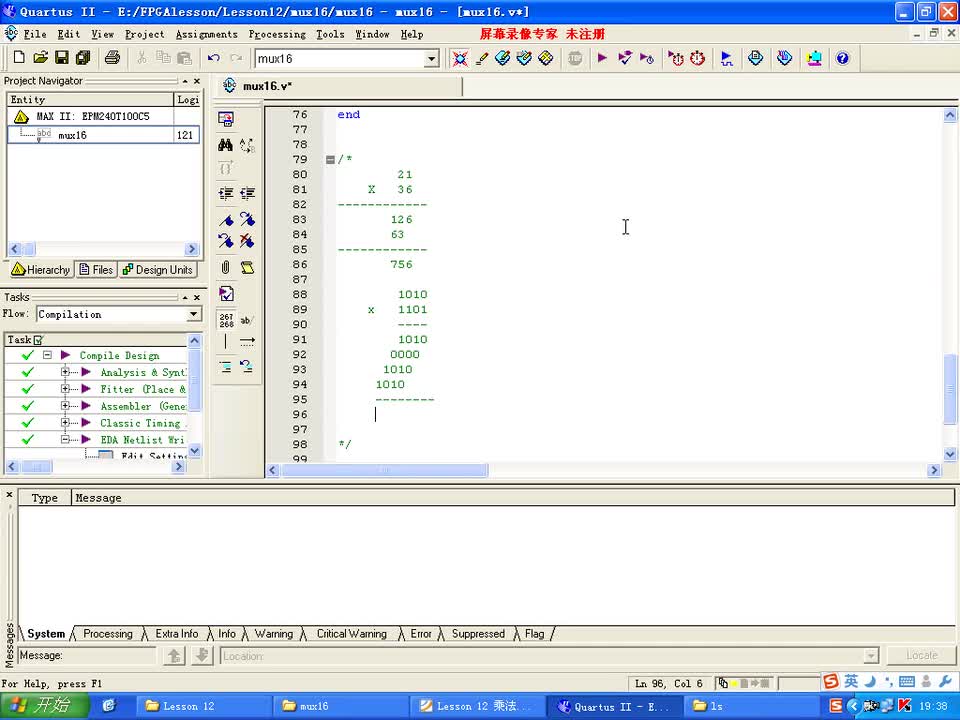

使用verilogHDL實(shí)現(xiàn)乘法器

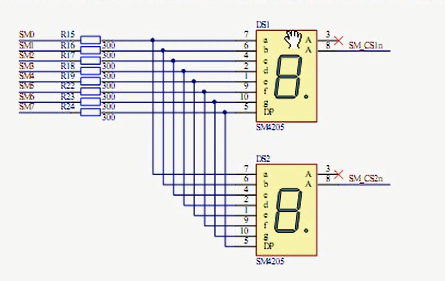

FPGA視頻教程之使用BJ-EPM240學(xué)習(xí)板進(jìn)行數(shù)碼管顯示實(shí)驗(yàn)的資料說(shuō)明

FPGA視頻教程之BJ-EPM240學(xué)習(xí)板的詳細(xì)資料介紹

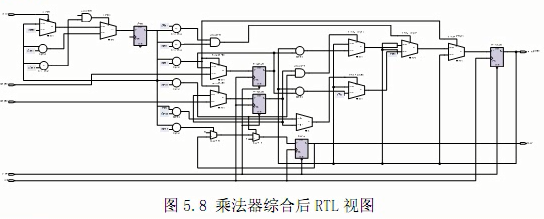

FPGA視頻教程之BJ-EPM240學(xué)習(xí)板乘法器設(shè)計(jì)實(shí)驗(yàn)的詳細(xì)資料說(shuō)明

BJ-EPM240學(xué)習(xí)板介紹

BJ-EPM240學(xué)習(xí)板之Johnson.計(jì)數(shù)器實(shí)驗(yàn)

BJ-EPM240學(xué)習(xí)板之乘法器設(shè)計(jì)實(shí)驗(yàn)

課程5:BJ-EPM240學(xué)習(xí)板介紹

深入淺出玩轉(zhuǎn)FPGA視頻:BJ-EPM240學(xué)習(xí)板介紹

FPGA視頻教程:BJ-EPM240學(xué)習(xí)板-乘法器設(shè)計(jì)實(shí)驗(yàn)

FPGA視頻教程:BJ-EPM240學(xué)習(xí)板介紹

乘法器原理_乘法器的作用

評(píng)論