聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

寄存器

+關注

關注

31文章

5355瀏覽量

120510 -

時鐘

+關注

關注

11文章

1734瀏覽量

131532 -

時序

+關注

關注

5文章

389瀏覽量

37347

發布評論請先 登錄

相關推薦

FPGA 高級設計:時序分析和收斂

設計都首先要進行周期約束,這樣做的好處除了在綜合與 布局布線時給出規定目標外,還能讓時序分析工具考察整個設計的 Fmax 等。

Altera 的周期定義如圖 6 所示,公式描述如下:

圖 6

發表于 06-17 17:07

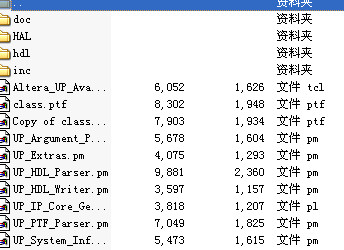

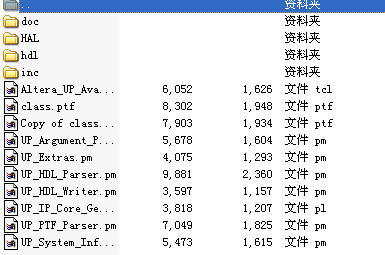

Modelsim SE 進行時序仿真及altera庫的添加 [轉]

Modelsim進行時序仿真。 第一部分介紹Quartus II自動調用Modelsim進行時序仿真的操作過程;第二部分介紹altera仿真庫(Verilog)的添加操作過程;第三部分簡單的介紹一下

發表于 02-01 11:37

通向FPGA之路---七天玩轉Altera教程

本系列教程的宗旨是在力求全面介紹Altera及其QuartusII軟件原理的基礎上,對何如使用Altera FPGA進行基礎設計、時序分析、驗證、優化四大方面進行

發表于 12-04 14:36

altera時序約束與分析

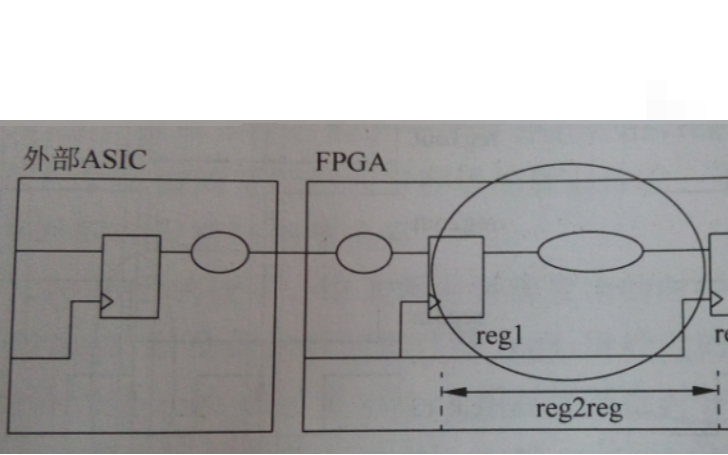

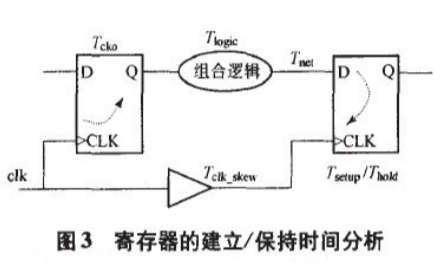

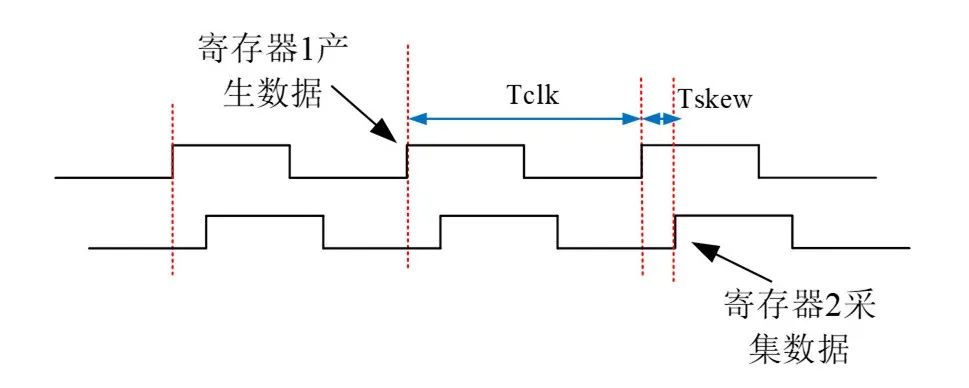

時序分析的主要對象是:在REG2中,時鐘信號CLK經過路徑③的有效沿,與從REG1寄存器輸出的數據經過路徑①到達REG2的D端時的關系。

正點原子FPGA靜態時序分析與時序約束教程

靜態時序分析是檢查芯片時序特性的一種方法,可以用來檢查信號在芯片中的傳播是否符合時序約束的要求。相比于動態時序

發表于 11-11 08:00

?63次下載

ALTERA系列的FPGA時序分析

其中前三類路徑是和內部寄存器reg和時鐘CLK有關的,因此還需關注內部數據信號與時鐘鎖存沿的建立時間和保存時間(具體見時序分析一),而最后一類信號的傳輸通常不經過時鐘,因此它的約束也相對簡單

發表于 01-08 16:47

?13次下載

FPGA的靜態時序分析詳細講解分析

任何學FPGA的人都跑不掉的一個問題就是進行靜態時序分析。靜態時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內容又不那么一致,為了徹底解決這個問題,我研究了一天,終于找到了一種

發表于 01-12 17:48

?19次下載

altera時序分析基礎項目講解

altera時序分析基礎項目講解

評論