防止電路閂鎖的建議

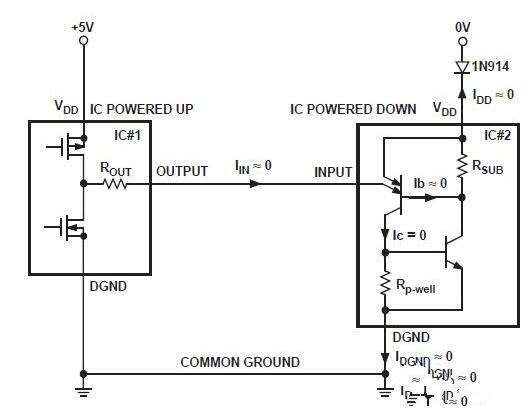

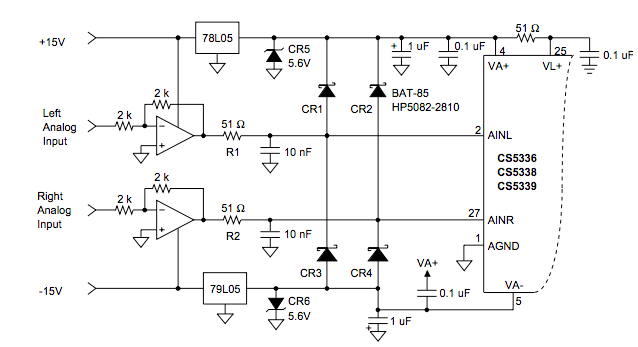

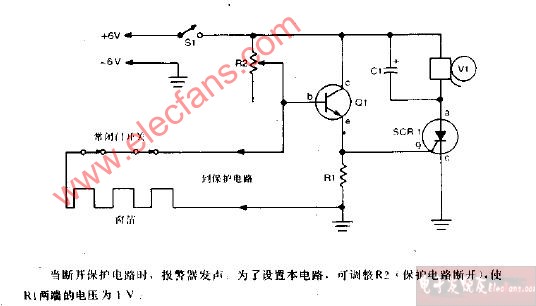

1、如果由于上電排序而發(fā)生閂鎖,可以利用二極管與VDD串聯(lián)如果任何時候器件的數(shù)字輸入或輸出都超過VDD,可以在VDD串聯(lián)二極管(如下圖使用1N914)來阻止SCR觸發(fā)和隨后的閂鎖產(chǎn)生。這是因為二極管能夠防止寄生橫向PNP晶體管的基極電流從VDD引腳流出,從而防止SCR觸發(fā)。

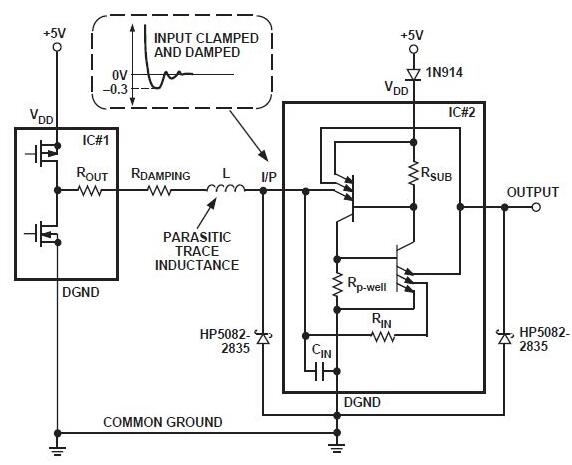

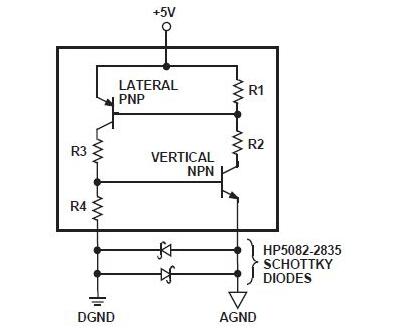

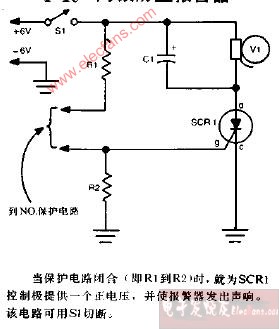

2、將肖特基二極管添加到DGND(數(shù)字地)可防止電壓不足如果器件的數(shù)字輸入和輸出隨時低于DGND,則可以從這些輸入或輸出連接到DGND的肖特基二極管將有效地將負(fù)偏移鉗位在-0.3V至-0.4V之間。這可以防止寄生NPN晶體管的發(fā)射極與基極結(jié)導(dǎo)通,并且還可以防止SCR觸發(fā)。

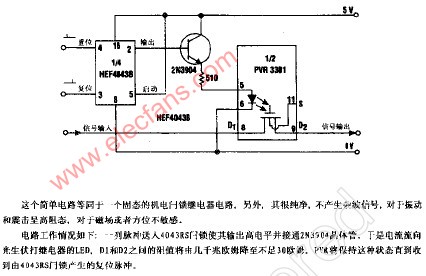

3、在DGND和AGND(模擬地)之間連接肖特基二極管如果DGND電位偶爾會超過AGND0.3V或更多,則可以在器件兩個引腳之間放置肖特基二極管來將阻止相關(guān)寄生NPN晶體管的導(dǎo)通。這提供了額外的防止閂鎖的保護(hù)。此外,與前面提到的反向并聯(lián)連接的額外二極管可以在另一個方向上將DGND限制到AGND,這大大減少了數(shù)字噪聲被注入器件的可能性。

閂鎖效應(yīng)介紹

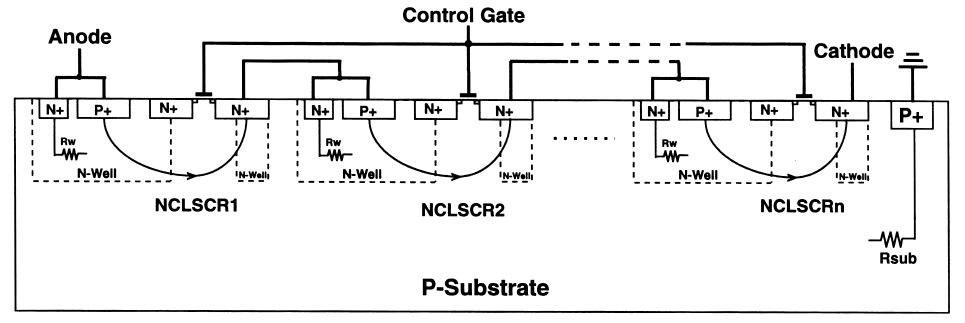

閂鎖效應(yīng)是CMOS工藝所特有的寄生效應(yīng),嚴(yán)重會導(dǎo)致電路的失效,甚至燒毀芯片。閂鎖效應(yīng)是由NMOS的有源區(qū)、P襯底、N阱、PMOS的有源區(qū)構(gòu)成的n-p-n-p結(jié)構(gòu)產(chǎn)生的,當(dāng)其中一個三極管正偏時,就會構(gòu)成正反饋形成閂鎖。避免閂鎖的方法就是要減小襯底和N阱的寄生電阻,使寄生的三極管不會處于正偏狀態(tài)。 靜電是一種看不見的破壞力,會對電子元器件產(chǎn)生影響。ESD 和相關(guān)的電壓瞬變都會引起閂鎖效應(yīng)(latch-up),是半導(dǎo)體器件失效的主要原因之一。

如果有一個強(qiáng)電場施加在器件結(jié)構(gòu)中的氧化物薄膜上,則該氧化物薄膜就會因介質(zhì)擊穿而損壞。很細(xì)的金屬化跡線會由于大電流而損壞,并會由于浪涌電流造成的過熱而形成開路。這就是所謂的“閂鎖效應(yīng)”。在閂鎖情況下,器件在電源與地之間形成短路,造成大電流、EOS(電過載)和器件損壞。

-

電路

+關(guān)注

關(guān)注

172文章

5904瀏覽量

172139 -

閂鎖電路

+關(guān)注

關(guān)注

0文章

2瀏覽量

8601

發(fā)布評論請先 登錄

相關(guān)推薦

淺談SCR閂鎖及不同的輸入保護(hù)技術(shù)

CMOS閂鎖測試中的電流脈沖如何加上的?

高速ADC的單粒子閂鎖和瞬態(tài)

需要多少電流電壓來引起閂鎖

閂鎖代碼幫助

電路設(shè)計中CMOS器件閂鎖的分析與對策

防閂鎖型開關(guān)ADG5412 和ADG5413性能及優(yōu)勢分析

AN-793: iCoupler?隔離產(chǎn)品的ESD/閂鎖考慮因素

U-tec宣布推出首款帶指紋讀取器的鎖閂智能鎖

可控硅結(jié)構(gòu)靜電防護(hù)器件的防閂鎖工程

如何防止電路中的閂鎖問題

如何防止電路中的閂鎖問題

評論