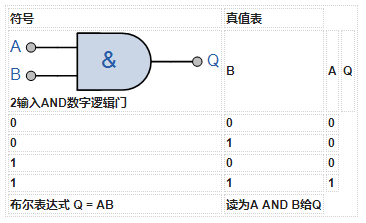

數字邏輯門是一種電子電路,它根據輸入上存在的數字信號的組合做出邏輯決策

數字邏輯門可能有多個輸入,(A,B) ,C等,但通常只有一個數字輸出,(Q)。各個邏輯門可以連接在一起形成組合或順序電路,或更大的邏輯門功能。

標準的商用數字邏輯門有兩種基本系列或形式,TTL代表晶體管 - 晶體管邏輯,如7400系列,CMOS代表互補金屬氧化物硅,它是4000系列芯片。這種TTL或CMOS符號是指用于制造集成電路(IC)或“芯片”的邏輯技術,因為它通常被稱為。

數字邏輯門

一般來說,TTL邏輯IC使用NPN和PNP型雙極結型晶體管,而CMOS邏輯IC則使用互補MOSFET用于輸入和輸出電路的JFET型場效應晶體管。

除TTL和CMOS技術外,還可以通過將二極管,晶體管和電阻連接在一起來制作簡單的數字邏輯門,以生成RTL,電阻器 - 晶體管邏輯門,DTL,二極管 - 晶體管邏輯門或ECL,發射極 - 耦合邏輯門,但與流行的CMOS系列相比,這些都不太常見。

集成電路或IC,因為它們通常被稱為,它們可以根據它們包含的晶體管數量或“門”組合成一個系列。例如,一個簡單的 AND 門只包含幾個單獨的晶體管,因為更復雜的微處理器可能包含數千個單獨的晶體管門。集成電路根據邏輯門的數量或單個芯片內電路的復雜程度進行分類,其中單個門的數量的一般分類如下:

集成電路的分類

小規模集成或(SSI) - 在單個封裝中最多可包含10個晶體管或幾個門,例如AND,或,不是門。

中等規模集成或(MSI) - 在一個封裝內的10到100個晶體管或數十個門之間執行數字操作例如加法器,解碼器,計數器,觸發器和多路復用器。

大規模集成或(LSI) - 介于100和1,000個晶體管或數百個之間門控和執行特定的數字操作,如I / O芯片,存儲器,算術和邏輯單元。

超大規模集成或(VLSI) - 介于1,000和10,000之間nsistor或數千個門并執行計算操作,如處理器,大型存儲器陣列和可編程邏輯器件。

超大規模集成或(SLSI) - 單個封裝中的10,000到100,000個晶體管,并執行計算操作,如微處理器芯片,微控制器,基本PIC和計算器。

超大規模集成或(ULSI) - 超過100萬個晶體管 - 用于計算機CPU,GPU,視頻處理器,微控制器,FPGA和復雜PIC的大男孩。

雖然“超大規模”ULSI分類使用得不太好,但代表集成電路復雜性的另一級集成稱為片上系統或(SOC)簡而言之。在這里,微處理器,存儲器,外圍設備,I / O邏輯等各個組件都是在一塊硅片上生成的,它代表了一個芯片內的整個電子系統,字面上將“集成”字放入集成電路中。

這些完整的集成芯片可在一個封裝內容納多達1億個硅CMOS晶體管柵極,通常用于移動電話,數碼相機,微控制器,PIC和機器人類應用。 / p>

摩爾定律

1965年,英特爾公司聯合創始人戈登摩爾預測,“單個芯片上的晶體管和電阻器的數量將每18個月增加一倍”。半導體門技術。當Gordon Moore在1965年發表他的著名評論時,單個硅片或芯片上只有大約60個單獨的晶體管柵極。

1971年世界上第一個微處理器是具有4位的Intel 4004數據總線在單個芯片上包含大約2,300個晶體管,工作頻率約為600kHz。今天,英特爾公司已經在其近4GHz的新型四核i7-2700K Sandy Bridge 64位微處理器芯片上放置了驚人的12億個獨立晶體管柵極,片上晶體管數量仍在增加,因為更快的微處理器和微控制器開發。

數字邏輯狀態

數字邏輯門是構建所有數字電子電路和基于微處理器的系統的基本構建模塊。基本數字邏輯門對二進制數執行 AND , OR 和 NOT 的邏輯運算。

僅在數字邏輯設計中允許兩個電壓電平或狀態,這些狀態通常稱為邏輯“1”和邏輯“0”,或高和低,或者為真和假。這兩種狀態分別用“1”和“0”的二進制數字表示在布爾代數和標準真值表中。

一個很好的例子數字狀態是簡單的燈開關。開關可以是“ON”或“OFF”,一種是另一種狀態,但不能同時是兩種狀態。然后我們可以總結這些不同數字狀態之間的關系:

| 布爾代數 | 布爾邏輯 | 電壓狀態 |

| 邏輯“1” | TRUE(T) | HIGH(H) |

| 邏輯“0” | FALSE(F) | LOW(L) |

大多數數字邏輯門和數字邏輯系統使用“正邏輯”,其中邏輯電平為“0”或“LOW”由零電壓,0v或地表示,邏輯電平“1”或“HIGH”由更高的電壓表示,例如+5伏,從一個電壓電平切換到另一個電壓電平邏輯電平“0”到“1”或“1”到“0”盡可能快地進行,以防止邏輯電路的任何錯誤操作。

還存在一個互補的“否定邏輯“系統中邏輯的值和規則”0“并且邏輯“1”相反,但在本教程中關于數字邏輯門的部分我們只會參考正邏輯約定,因為它是最常用的。

在標準TTL(晶體管 - 晶體管邏輯)中IC有一個預先定義的輸入和輸出電壓電壓范圍,它確切地定義了什么是邏輯“1”電平,什么是邏輯“0”電平,這些如下所示。

TTL輸入和輸入輸出電壓電平

雙極7400和CMOS 4000都有各種各樣的邏輯門類型數字邏輯門系列,如74Lxx,74LSxx,74ALSxx,74HCxx,74HCTxx,74ACTxx等,每一個都有其獨特的優點和缺點。產生邏輯“0”或邏輯“1”所需的確切開關電壓取決于特定的邏輯組或系列。

然而,當使用標準+5伏電源時,任何TTL電壓輸入之間2.0v和5v被認為是邏輯“1”或“高”,而任何低于0.8v的電壓被認為是邏輯“0”或“低”。這兩個電壓電平之間的電壓區域作為輸入或輸出稱為 Indeterminate Region ,在此區域內工作可能會導致邏輯門產生錯誤輸出。

與TTL類型相比,CMOS 4000邏輯系列使用不同的電壓電平,因為它們是使用場效應晶體管或FET設計的。在CMOS技術中,邏輯“1”電平工作在3.0和18伏之間,邏輯“0”電平工作在1.5伏以下。然后下表顯示了傳統TTL和CMOS邏輯門的邏輯電平之間的差異。

TTL和CMOS邏輯電平

| 設備類型 | 邏輯0 | 邏輯1 |

| TTL | 0到0.8v | 2.0到5v(V CC ) |

| CMOS | 0到1.5v | 3.0到18v(V DD ) |

然后從上面的觀察中,我們可以將理想的TTL數字邏輯門定義為具有0伏(地)的“低”電平邏輯“0”和“高”電平邏輯的邏輯門。 + 1伏特的“1”,這可以證明為:

理想的TTL數字邏輯門電壓電平

開關的打開或關閉產生的任何一個邏輯電平“1”或邏輯電平“0”,電阻 R 稱為“上拉”電阻。

數字邏輯噪聲

然而,在這些定義的HIGH和LOW值之間存在通常被稱為“無人區域”(上面的藍色區域),如果我們在這個無人區域內應用一個值的信號電壓,我們不知道是否邏輯門將響應它作為電平“0”或電平“1”,輸出將變得不可預測。

噪聲是隨機給出的名稱通過外部干擾(例如來自附近的開關,電源波動或來自拾取雜散電磁輻射的導線和其他導體)感應到電子電路中的不需要的電壓。然后為了使邏輯門不受噪聲影響必須具有一定的噪聲容限或抗噪聲能力。

數字邏輯門噪聲抗擾度

在上面的示例中,噪聲信號疊加在Vcc電源電壓上,只要它保持在最小電平以上(V ON(min) ))輸入邏輯門的相應輸出不受影響。但是當噪聲電平變得足夠大并且噪聲尖峰導致HIGH電壓電平下降到低于該最小電平時,邏輯門可以將該尖峰解釋為低電平輸入并且相應地切換輸出產生錯誤輸出切換。然后,為了使邏輯門不受噪聲影響,它必須能夠容忍其輸入上的一定量的不需要的噪聲而不改變其輸出狀態。

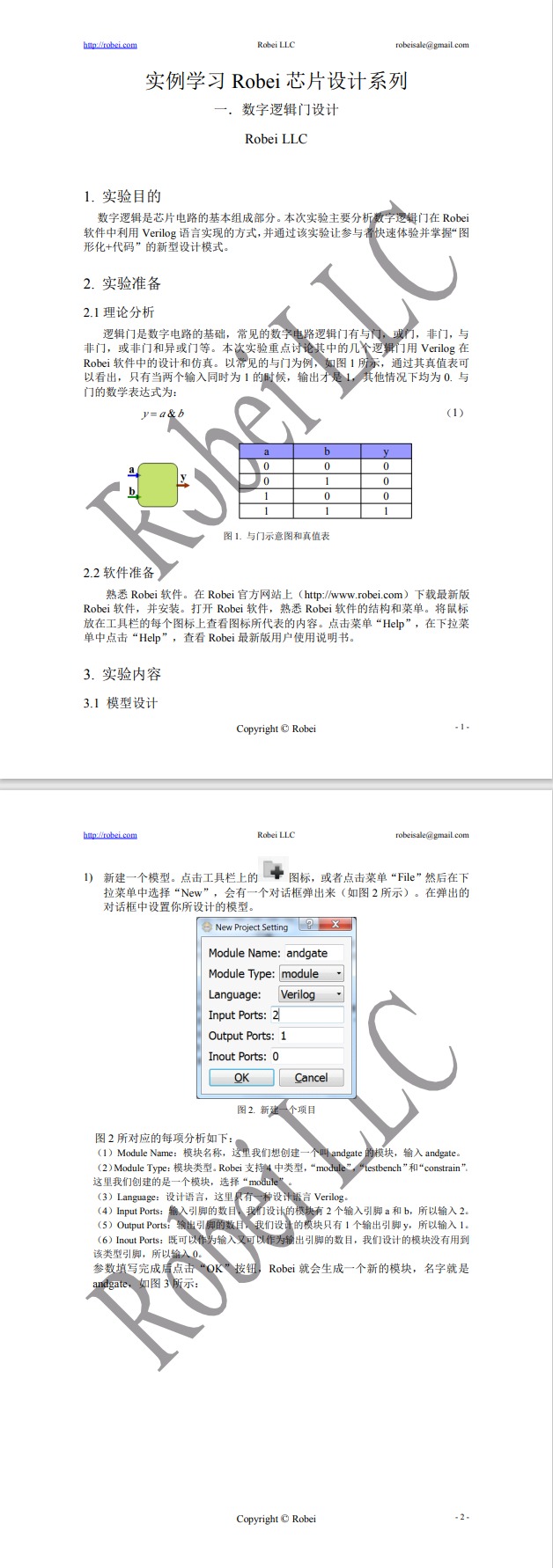

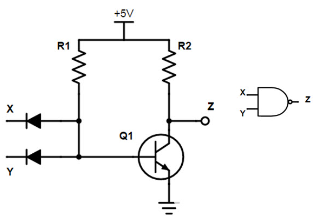

簡單的基本數字邏輯門

簡單的數字邏輯門可以通過將晶體管,二極管和電阻器與二極管電阻邏輯(DRL) AND 門和二極管 - 晶體管邏輯(DTL)的簡單示例相結合來制作下面給出 NAND 門。

| 二極管電阻電路 | 二極管 - 晶體管電路 |

|

|

2輸入與非門 |

簡單的2輸入二極管電阻 AND <通過添加單個晶體管反相( NOT )級,可以將/ span> gate轉換為 NAND 門。使用諸如二極管,電阻器和晶體管之類的分立元件來制造數字邏輯門電路并不用于實際商用邏輯IC,因為這些電路會受到傳播延遲或柵極延遲以及由于上拉電阻引起的功率損耗。

二極管電阻邏輯的另一個缺點是沒有“扇出”功能,即單個輸出能夠驅動下一級的許多輸入。此類設計也沒有完全“關閉”,因為邏輯“0”產生0.6v的輸出電壓(二極管電壓降),因此使用以下TTL和CMOS電路設計。

基本TTL邏輯門

上面的簡單二極管電阻 AND 門為其輸入使用單獨的二極管,每個輸入一個。由于晶體管由連接在一起代表NPN或PNP器件的兩個二極管電路組成,因此DTL電路的輸入二極管可以由一個具有多個發射極輸入的NPN晶體管代替,如圖所示。

2輸入與非門

由于與非門包含單級反相NPN晶體管電路( TR 2 ) Q 時的輸出邏輯電平“1”僅在 TR 1 的兩個發射極連接到邏輯時出現電平“0”或接地允許基極電流通過發射極的PN結而不是集電極。 TR 1 的多個發射極作為輸入連接,從而產生 NAND 門功能。

在標準TTL邏輯門中,晶體管完全在“截止”區域工作,或者完全在飽和區域工作,晶體管作為開關類型工作。

發射極耦合數字邏輯門

發射極耦合邏輯或 ECL 是另一種使用雙極晶體管邏輯的數字邏輯門,晶體管不在飽和區工作,因為它們與標準的TTL數字邏輯門。相反,輸入和輸出電路是推挽式連接晶體管,電源電壓相對于地為負。

這樣可以提高發射極耦合邏輯門的工作速度,達到千兆赫茲范圍與標準TTL類型相比,噪聲對ECL邏輯的影響更大,因為不飽和晶體管在其有源區域內工作并放大和切換信號。

集成電路的“74”子系列

考慮到傳播延遲,電流消耗,扇入和扇出要求等電路設計的改進,這種類型的TTL雙極晶體管技術構成了前綴“74”系列數字邏輯IC的基礎,例如“7400”四路2輸入 AND 門,或“7402”四路2輸入或門等

74xx系列IC的子系列可用于制造門的不同技術,它們用74號和之間的字母表示。設備編號。有許多TTL子系列可提供各種開關速度和功耗,例如74L00或74ALS00 AND gate,“L”代表“低功率TTL”,“ALS”代表“高級低功率肖特基TTL”,下面列出了這些。

?74xx或74Nxx:標準TTL - 這些器件是70年代早期推出的原始TTL系列邏輯門。它們具有大約10ns的傳播延遲和大約10mW的功耗。供電電壓范圍:4.75至5.25伏

?74Lxx:低功率TTL - 通過增加內部電阻的數量,功耗比標準類型提高,但代價是降低在切換速度。電源電壓范圍:4.75至5.25伏

?74Hxx:高速TTL - 通過減少內部電阻數量來改善開關速度。這也增加了功耗。電源電壓范圍:4.75至5.25伏

?74Sxx:肖特基TTL -Schottky技術用于改善輸入阻抗,開關速度和功耗(2mW),與74Lxx和74Hxx類型。電源電壓范圍:4.75至5.25伏

?74LSxx:低功率肖特基TTL - 與74Sxx類型相同,但內部電阻增加,以提高功耗。電源電壓范圍:4.75至5.25伏

?74ASxx:高級肖特基TTL - 改進的設計超過74Sxx肖特基類型,經過優化可提高開關速度,但功耗約為22mW。電源電壓范圍:4.5至5.5伏

?74ALSxx:高級低功耗肖特基TTL - 與74LSxx類型相比,功耗約為1mW,開關速度更高,為4nS。電源電壓范圍:4.5至5.5伏

?74HCxx:高速CMOS -CMOS技術和晶體管,通過CMOS兼容輸入降低功耗小于1uA。供電電壓范圍:4.5至5.5伏

?74HCTxx:高速CMOS -CMOS技術和晶體管,可降低小于1uA的功耗,但傳播延遲增加約16nS到TTL兼容輸入。電源電壓范圍:4.5至5.5伏

基本CMOS數字邏輯門

TTL數字邏輯門系列的主要缺點之一是邏輯門基于在雙極晶體管邏輯技術和晶體管是電流操作器件時,它們從固定的+5伏電源消耗大量電能。

此外,TTL雙極晶體管門在切換時的工作速度有限“OFF”狀態為“ON”狀態,反之亦然,稱為“門”或“傳播延遲”。為了克服這些限制,互補MOS稱為“CMOS”(C> > > > > > 這些門使用“場效應晶體管”或FET開發。

由于這些門同時使用P溝道和N溝道MOSFET作為輸入器件,在沒有開關的靜態條件下,CMOS門的功耗幾乎為零(1至2μA),非常適合用于低功耗電池電路,開關速度高達100MHz,適用于高頻定時和計算機電路。

2輸入與非門

此CMOS門示例包含三個N溝道MOSFET,每個輸入FET一個 1 和FET 2 ,一個用于輸出FET 3 。當輸入 A 和 B 都處于邏輯電平“0”時,FET 1 和FET 2 都是切換為“OFF”,從FET 3 的源提供輸出邏輯“1”。

當一個或兩個輸入處于邏輯電平“1”時,電流流過相應的FET在 Q 處提供相當于邏輯“0”的輸出狀態,從而產生 NAND 門功能。

電路設計的改進方面開關速度,低功耗和改進的傳播延遲導致標準CMOS 4000“CD”系列邏輯IC正在開發中,以補充TTL范圍。

與標準TTL數字邏輯門一樣,所有CMOS封裝中提供主要的數字邏輯門和器件,如CD4011,四路2輸入 NAND 門,或CD4001,四路2輸入 NOR 門及其所有子系列。

與TTL邏輯一樣,互補MOS(CMOS)電路利用了N溝道和P溝道器件可以在同一襯底材料上一起制造以形成各種邏輯功能的事實。

其中一個主要缺點是與同等TTL類型相比,CMOS系列IC容易被靜電損壞。與TTL邏輯門不同,它們的輸入和輸出電平均采用+ 5V單電壓工作,CMOS數字邏輯門工作在+3至+18V的單電源電壓下。

通用CMOS子電路系列產品包括:

?4000B系列:標準CMOS - 這些器件是70年代初推出的原始緩沖CMOS系列邏輯門,運行電源電壓為3.0至18V dc

?74C系列:5v CMOS - 這些器件與標準5v TTL器件引腳兼容,因為它們的邏輯開關采用CMOS實現,但與TTL兼容的輸入。它們的工作電壓為3.0至18V dc

請注意,CMOS邏輯門和器件對靜電非常敏感,因此請務必采取適當的防靜電墊或接地工作臺的預防措施,防靜電腕帶,除非需要,否則不要從防靜電包裝中取出部件。

在下一個關于數字邏輯門的教程中,我們將看到數字邏輯與門功能,如下所用TTL和CMOS邏輯電路以及布爾代數定義和真值表。

-

TTL

+關注

關注

7文章

503瀏覽量

70231 -

數字邏輯

+關注

關注

0文章

73瀏覽量

16645

發布評論請先 登錄

相關推薦

什么是數字邏輯門_數字邏輯門基礎知識

什么是數字邏輯門_數字邏輯門基礎知識

評論