電源和地平面

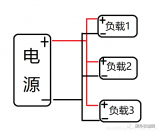

應該盡可能的使用電源和地平面,

Why?

在設備和電源之間提供一個低阻抗的

路徑

提供屏蔽

提供散熱

降低分布電感

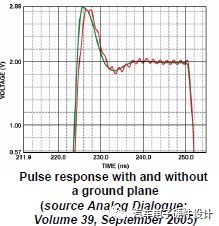

一個完整的無破損的平面是最優選擇

破碎的地平面會在走線的上下層之間引入寄生電感

Remember!

低頻時,電流總是流過最小電阻路徑

高頻時,電流總是渡過最小電感路徑

去耦電容(或“旁路電容”)

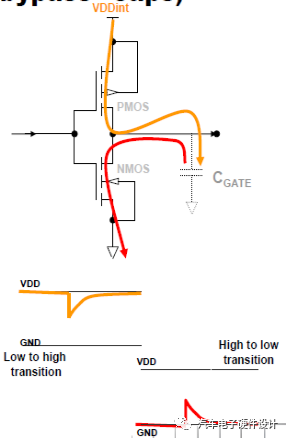

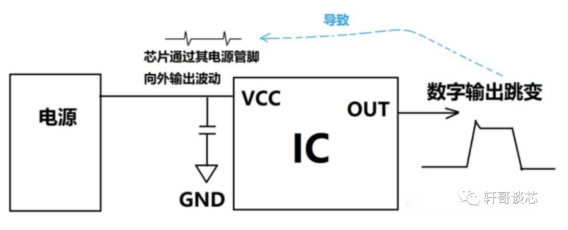

當設備里的門電路開關時,設備里的阻抗會有一個瞬時的變化

結果就是電流會有一個瞬時的變化

去耦電容會這些瞬時的變化提供一個低阻抗的電流源

降低電源地之間的電壓波動

幫助電源地信號工作在設備的工作SPEC之內

高速設計中有5個頻段需要調節

DC至10Khz

通過調節模塊來調節

10Khz至100Khz

通過去耦電容來調節

100Khz to 10Mhz

通過100nf(0.1uf)來調節

10 Mhz to 100Mhz

通過10 nf來調節

100Mhz至更高

通過1nf和PCB電源和地平面來調節

需要多少去耦電容才夠用呢?

取決于系統

需要考慮工作頻率,I/O的開關數量,每個Pin腳的容性負載,走線的特征阻抗, 結點的溫度,芯片內部的運算

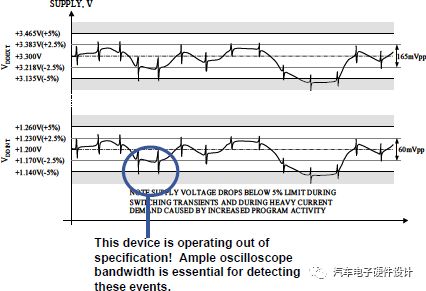

經驗法則:從DC至高頻的每個頻段內,供電引腳的電壓波動都就小于5%

DC供電電壓的最大波動加上噪聲的最大值應該小于供電電壓的5%

需要一個足夠帶寬的示波器

有很多的方法去評估總共需要的容值,以及如何分布電容

這是一個復雜的問題,特別是在處理現在那些包含有成千上萬門電電路的處理器的時候.

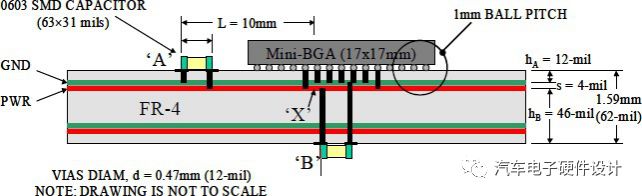

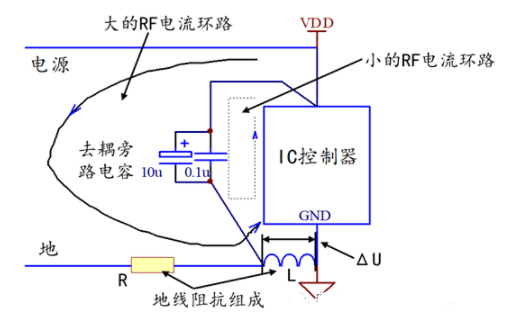

為了獲得最好的性能, 應該盡可能的降低供 電引腳與去耦電容之 間的電感與電阻

PCB布線和過孔會增加阻抗

當使用電源/地平面對時,電容如同在PCB頂層 一樣有效

100Mhz以上的有效電容…

隨著時鐘頻率和邊緣變化率的提高,如何有效的使用旁路電容變得越來越困難

電容的ESL(等效串聯電感)隨著頻率的增加而增加

電容的ESR(等效串聯電阻)的增加會降低電容的效力

電容的寄生參數(pads,vias)所帶來的電抗會隨著頻率增加而增加

100nf的電容在100Mhz之上是無用的

-

電源

+關注

關注

184文章

17735瀏覽量

250501 -

pcb

+關注

關注

4319文章

23111瀏覽量

398247 -

去耦電容

+關注

關注

11文章

316瀏覽量

22384

原文標題:優秀的高速PCB設計之去耦電容

文章出處:【微信號:QCDZYJ,微信公眾號:汽車電子工程知識體系】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速PCB設計指南

專業PCB設計,高速PCB設計,PCB設計外包, PCB Layout,PCB Design,PCB畫板公司,PCB設計公司,迅安通科技公司介紹

去耦電容的擺放位置和作用

巧了不是,原來你也不知道啥是去耦電容的“濾波半徑”啊!

什么是去耦電容 有什么作用

去耦電容越大越好嗎,去耦電容值的選擇

耦合和去耦有什么區別,耦合電容和去耦電容的作用分別是什么?

分享PCB中的去耦電容設計

優秀的高速PCB設計之去耦電容

優秀的高速PCB設計之去耦電容

評論