-新型Si539x抖動清除器實現更高端口數的前傳/回傳、城域/核心以及數據中心設計-

中國,北京 - 2019年6月20日 - Silicon Labs (亦稱“芯科科技”,NASDAQ:SLAB)日前擴展了Si539x抖動衰減器系列產品,其新器件型號具有完全集成的參考時鐘、增強了系統可靠性和性能,同時簡化了高速網絡設計中的PCB布局布線。新型Si539x抖動衰減器設計旨在滿足100/200/400/600/800G設計中苛刻的參考時鐘要求,為最先進的以太網交換機SoC、PHY、FPGA和ASIC中56G PAM-4 SerDes所需的嚴格抖動要求提供超過40%的余量,同時也為新興的112G SerDes設計提供符合未來需求的解決方案。

Silicon Labs時鐘產品總經理James Wilson表示: “網絡設備供應商正在競相開發能夠處理5G無線流量的更高速、更高容量的設備。這種轉變推動了對前傳/回傳(fronthaul/backhaul)、城域/核心以及數據中心應用中對更高性能時鐘解決方案的需求。集成56 Gbps SerDes的FPGA和PHY支持更高容量的100/200/400/600/800G光纖和以太網線卡,但是卻要面臨越來越復雜的電路板設計以及布局布線帶來的挑戰。通過在Silicon Labs最新的Si539x抖動衰減器中集成參考時鐘,助力整個行業更加輕松的遷移到更高端口數量、更高容量的100/200/400/600/800G設計。”

提高系統可靠性和性能 — 新型Si539x抖動衰減器集成了一個高度可靠的晶體,該晶體已在全溫度范圍內進行了全面測試,并針對活性下降(activity dip)進行了預篩選。 Si539x器件已經完全通過各種可靠性測試,包括沖擊、振動、溫度循環和晶體老化。規格嚴謹的晶體和創新的器件結構降低了晶體對系統風扇引起的溫度變化的敏感度,從而實現更加一致、可靠的操作。

高聲頻發射噪聲抗擾度 — 集成參考時鐘的器件結構比外部晶體設計具有更高的聲頻發射(AE)抗擾度。AE是當PCB板經受溫度梯度或外部機械力而導致PCB組裝中的微裂紋或塑性變形時發生的噪聲波輻射。與由于AE引起的更大頻率誤差的分立晶體不同,Si539x器件的創新封裝結構可隔離并保護晶體免受AE噪聲影響,確保可靠的操作和一致的頻率響應。

節省板面積 — 設計高端口數的光纖和以太網線卡的客戶非常重視縮減整體電路板面積。通過使用帶有集成參考時鐘的抖動衰減器,開發人員可以將PCB占位面積減少35%以上,并帶來額外的益處:集成的參考時鐘消除了對晶體下方的禁布區的需求,因此可在器件周圍進行更密集的時鐘布線,從而進一步簡化了PCB布局布線。

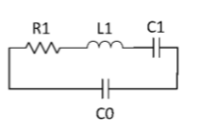

頻率靈活性和時鐘分發 — Si539x器件可在多達12個差分時鐘輸出上產生100 Hz至1028 MHz頻率的任意組合,無須常用的獨立時鐘發生器和時鐘緩沖器。這些優勢實現了“片上時鐘樹”時鐘,同時消除了與離散時鐘樹解決方案相關的附加抖動。

價格與供貨

新型Si539x抖動衰減器現已量產,可提供樣片。 Silicon Labs提供各種評估板(EVB),零售價為299美元,它們適用于選擇帶有內部或外部參考時鐘的Si539x器件。EVB使客戶能夠快速從設備配置轉向詳細的性能評估,通過與ClockBuilder Pro軟件工具無縫協作,開發人員能夠快速開發自定義配置并衡量性能。有關Si539x產品定價,請聯系各地的Silicon Labs銷售代表或授權經銷商。

-

衰減器

+關注

關注

4文章

640瀏覽量

34336 -

時鐘設計

+關注

關注

0文章

27瀏覽量

10908 -

Silicon Labs

+關注

關注

11文章

328瀏覽量

62470 -

5G

+關注

關注

1354文章

48436瀏覽量

563971

發布評論請先 登錄

相關推薦

常見衰減器故障及解決方案

精密衰減器的校準方法 工業自動化中的衰減器應用

高頻信號衰減器的工作原理 如何測量衰減器的衰減值

高性能抖動衰減器和時鐘發生器的推薦晶體、TCXO和OCXO參考手冊(之二)

高性能抖動衰減器和時鐘發生器的推薦晶體、TCXO和OCXO參考手冊(之一)

固定衰減器是什么意思

什么是衰減器?

光纖衰減器的優點

光纖衰減器的類型

光纖衰減器的應用

光纖衰減器的作用

毫微微時鐘網絡同步器、抖動衰減器和時鐘發生器RC32112A 數據表

π型衰減器的原理是什么?

光衰減器的作用 光衰減器的使用方法

FemtoClock2抖動衰減器和時鐘發生器RC325008A數據手冊

Silicon Labs推Si539x抖動衰減器 簡化高速網絡時鐘設計

Silicon Labs推Si539x抖動衰減器 簡化高速網絡時鐘設計

評論