FPGA的寬廣世界

“邏輯”一詞決定了FPGA的多功能性,讓FPGA有不同的模型,每個(gè)都有特定有時(shí)是獨(dú)一無二的屬性來滿足不同應(yīng)用的需要。在這當(dāng)中最有需求力的是防御雷達(dá)、電子戰(zhàn)還有信號(hào)情報(bào)領(lǐng)域,這方面的需求是如此嚴(yán)重以至于很難相信任何一個(gè)沒有超級(jí)計(jì)算機(jī)的系統(tǒng)能夠滿足這些需求。然而FPGA已經(jīng)席卷了防御工業(yè),多虧了它們大規(guī)模并行處理能力和I/O口,還有低功耗,以及最近具備的能夠處理浮點(diǎn)型算法的能力,該能力是解決許多類型計(jì)算問題的關(guān)鍵。

為這些應(yīng)用服務(wù)的是高性能FPGA如Altera的Stratix 10系列,其帶有400萬個(gè)邏輯單元,加工在Intel 14nm Tri-Gate處理器上,配合64位ARM Cortex-A53四核處理器。相比它們的處理器,它們有四倍的處理數(shù)據(jù)吞吐量、四倍的串行收發(fā)器帶寬、一個(gè)28-Gb/s的底板、56Gb/s的片到片/模塊速率、超過2.5Tb/s的串行內(nèi)存帶寬、超過1.3Tb/s的并行內(nèi)存接口帶寬,支持DDR4內(nèi)存,最高速度可達(dá)3200Mb/s.為了滿足前述浮點(diǎn)計(jì)算能力需求,它們提供超過單精度DSP 10倍的TFLOPs。

總體上,它們耗費(fèi)的能量是上一代單精度浮點(diǎn)型效率為100GFLOPS/W的高端FPGA的70%。Stratix 10設(shè)備被Altera的高級(jí)開發(fā)調(diào)試工具如OpenCL和SoC嵌入式設(shè)計(jì)套件中的Altera SDK所支持。

在中檔范圍的是Altera的立即啟動(dòng)型MAX 10 FPGA(圖3),集成了DSP、帶有12位ADC和溫度傳感器的模擬電路模塊、鎖相環(huán)、低延時(shí)全局時(shí)鐘、嵌入式軟處理器支持、內(nèi)存控制器、達(dá)到736KB的雙配置flash,允許你進(jìn)行存儲(chǔ)和在單片上的兩個(gè)圖像間動(dòng)態(tài)切換。它們基于TSMC系列的55-nm工藝嵌入式flash技術(shù)設(shè)計(jì),該技術(shù)支持立即啟動(dòng)配置以使它們可以控制系統(tǒng)中其它元件的上電或初始化。器件密度達(dá)2000到50000個(gè)邏輯元素。其它特點(diǎn)包括多達(dá)500個(gè)的用戶I/O引腳、18路模擬輸入通道還有128位AES加密。

圖3:評(píng)估板上的Altera MAX 10FPGA來源:Altera

特別有意思的是結(jié)合了Nios II代處理器內(nèi)核、片上外設(shè)和帶有片下內(nèi)存接口內(nèi)存的Nios II處理器。相比固化的微控制器,該Nios II代處理器是一個(gè)可配置的“軟”IP核,這意味著處理器內(nèi)核是可編程的并且不是固化在芯片里的。當(dāng)它在FPGA上實(shí)現(xiàn)的時(shí)候,它允許軟硬件工程師協(xié)同工作來優(yōu)化硬件以及測(cè)試?yán)镞呥\(yùn)行的軟件。

就連給大眾應(yīng)用服務(wù)的FPGA也有令人生畏的性能。例如,Lattice Semiconductor宣稱它的MachXO3 FPGA家族是尺寸最小、每I/O成本最低的平臺(tái),旨在擴(kuò)展系統(tǒng)能力和同時(shí)利用如MIPI、PCIe及千兆以太網(wǎng)之類的并行和串行I/O來橋接新興的連接。它們的封裝技術(shù)消除了連接線,此舉減少了成本,增大了I/O密度。基于模型可以看出它們有640到6900個(gè)查找表。典型的應(yīng)用領(lǐng)域包括消費(fèi)電子、計(jì)算及存儲(chǔ)、無線通信、工業(yè)控制還有汽車。他們的設(shè)計(jì)工具庫包括流行的邏輯綜合軟件、預(yù)先設(shè)計(jì)的IP、還有專門適合MachXO3L家族產(chǎn)品的免費(fèi)參考設(shè)計(jì)。為了讓開發(fā)更簡(jiǎn)單化,Terasic,一家專門使用FPGA(還有其它設(shè)備)定制子系統(tǒng)的公司,提供了基于Altera Cyclone V代GX FPGA搭建的Cyclone 5代GX開發(fā)套件硬件設(shè)計(jì)平臺(tái)。該板(圖4)包括相關(guān)硬件如一個(gè)Arduino接頭、板載USB Blaster、帶有高速收發(fā)器的音頻視頻功能。該公司的目標(biāo)是簡(jiǎn)化評(píng)估和制造FPGA子系統(tǒng)的任務(wù),而只需額外增加一臺(tái)基于Windows的PC機(jī)而已。

圖4:Terasic的Cyclone五代GX開發(fā)套件。(來源:Cyclone五代GX開發(fā)套件用戶指南)

并不是板上的唯一成員

FPGA可能確實(shí)很性感(以工程師的說法),但它們并不是唯一的可編程邏輯器件;其它設(shè)備也可以用單一設(shè)備提供一系列功能。看看來自Cypres半導(dǎo)體公司的“片上可編程系統(tǒng)”(PSoC)架構(gòu)吧,它是工業(yè)上唯一一個(gè)在單片上結(jié)合了高性能模擬模塊、可編程PLD、內(nèi)存以及微控制器的可編程嵌入式SOC,并且功耗很低。最高級(jí)的PSoC變體——PSoC-5家族集成了最新的ARM Cortex-M混合信號(hào)解決方案。

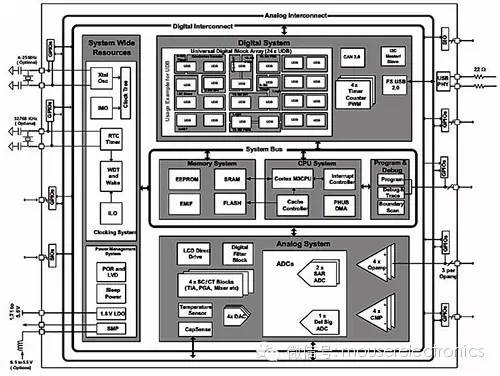

例如PSoC-5家族的CY8C56LP系列(圖5)在一個(gè)CPU子系統(tǒng)中提供可配置的模擬、數(shù)字還有互連電路。結(jié)合了模擬子系統(tǒng)、數(shù)字子系統(tǒng)、路由和I/O的CPU使其在一大片消費(fèi)者領(lǐng)域、工業(yè)領(lǐng)域還有醫(yī)藥領(lǐng)域中很有吸引力。該P(yáng)SoC的數(shù)字子系統(tǒng)通過其數(shù)字系統(tǒng)互聯(lián)電路高效地把任何一個(gè)外設(shè)與任何一個(gè)管腳連接,同時(shí)通過小型、快速、低功耗的通用數(shù)據(jù)模塊(UDB)來提供功能靈活性。

圖5:CY8C56LP的主要器件是ARM Cortex-M3內(nèi)核CPU,數(shù)字、模擬、可編程、調(diào)試還有測(cè)試子系統(tǒng),I/O,時(shí)鐘還有供電部分。來源:Cypress半導(dǎo)體公司

它支持測(cè)試版的PSoC創(chuàng)建庫、標(biāo)準(zhǔn)數(shù)字外設(shè)(UART、SPI、LIN、PRS、CRC、定時(shí)器、路由器、PWM、與門、或門等),這些都映射在UDB陣列中。每一個(gè)UDB包含可編程邏輯功能,還有一個(gè)小型狀態(tài)機(jī)引擎來允許它支持一系列外設(shè)。其它可配置的數(shù)字模塊可以用于特定的功能,如4個(gè)16位定時(shí)器,路由器,PWM模塊,I2C從、主和多-主模式,還有USB和CAN 2.0總線。該設(shè)備通常被稱為MCU,但是卻和FPGA一樣有很強(qiáng)的靈活性,并且相對(duì)編程容易。

總結(jié)

如果到此處你還沒有領(lǐng)略到如今可編程邏輯器件的強(qiáng)大性和多功能性,看看這個(gè):如今僅用三個(gè)OpenVPX外形設(shè)計(jì)(為防御系統(tǒng)使用)的卡就可以構(gòu)建一個(gè)完整的信號(hào)捕捉及處理子系統(tǒng)了。其主要設(shè)備包括兩片高端FPGA、高級(jí)ADC和DAC(每一個(gè)用兩片)、一個(gè)Intel i7四核處理器、SERDES 收發(fā)器、內(nèi)存和I/O口。多虧了較寬的帶寬還有高采樣率的DAC以及有強(qiáng)悍處理能力的FPGA,該三卡解決方案甚至可以利用DC捕捉到空中高達(dá)6GHz的信號(hào)。而幾年前要實(shí)現(xiàn)這個(gè)目標(biāo),則需要一個(gè)5到10倍體積的解決方案。

由于更多的市場(chǎng)部門,從消費(fèi)者電子到圖像處理、汽車、防御電子、工業(yè)自動(dòng)化和控制及醫(yī)藥領(lǐng)域,正利用這些設(shè)備的優(yōu)勢(shì),這方面的發(fā)展以及取得的成就讓人吃驚。因此盡管FPGA和其它可編程邏輯器件并不是一個(gè)新的概念,它們正實(shí)現(xiàn)著一些尖端領(lǐng)域的創(chuàng)舉。

-

微控制器

+關(guān)注

關(guān)注

48文章

7892瀏覽量

153553 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

524瀏覽量

44528

發(fā)布評(píng)論請(qǐng)先 登錄

可編程邏輯器件

PLD可編程邏輯器件

可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗(yàn)指導(dǎo)書

什么是PLD(可編程邏輯器件)

EDA技術(shù)與應(yīng)用(可編程邏輯器件)

可編程邏輯器件FPGA/CPLD結(jié)構(gòu)與應(yīng)用

電可編程邏輯器件EPLD是如何設(shè)計(jì)的

可編程邏輯器件測(cè)試

評(píng)論