在本系列中,我們將回顧和探討影響當今高速印刷電路板(PCB)設計的各種信號完整性(SI)問題,以及如何通過仿真來避免這些問題。

如果您是貿然進入了高速設計領域的新手工程師之一,并且被“信號完整性仿真”這個術語所震撼,請不要煩惱。在這次博客之旅中,我們先來回顧一下基礎知識,然后再介紹一些更高深的話題。

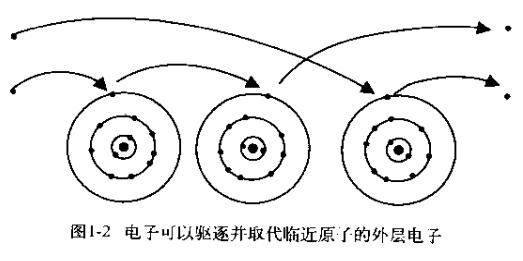

我們已不再生活在信號“0”和“1”的數字領域里了,因此我們現在需要考慮在從發射器到接收器的傳輸過程中模擬對信號都有些什么樣的影響。

隨著時鐘速度的增加和上升/下降時間的加快,PCB走線不再是理想的導線,而且對其承載的信號不透明。根據一般的經驗法則,任何長于“3倍(以厘米為單位)于上升時間(以ns為單位)或1.18倍(以英寸為單位)于上升時間(以ns為單位)”的走線都應該被視為傳輸線,再加上用于今天的高速信號的、以納秒(ns)/皮秒(ps)范圍計算的上升/下降時間,您就會發現即使是短走線,最后也會象傳輸線一樣工作。

封裝走線、引線、PCB走線、連接器和電纜都開始影響那些高速信號了。如果這些接口的阻抗設計和匹配得不當,可能會導致信號完整性問題,從而會影響到系統的性能和可靠性。

理想的數字信號

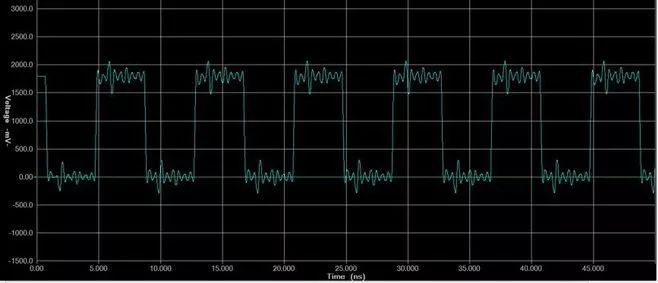

現實的數字信號

在上面的例子中,信號的模擬特性顯而易見。如果沒有恰當地考慮其影響,信號最終可能會出現過沖、下沖和毛刺,從而降低信號質量并影響器件的操作。

過沖會降低器件的可靠性,在極端情況下還會對器件造成不可逆轉的損壞。下沖可能會引起相同的反向偏置,以及反向偏置基板,這會導致器件以從未打算操作的方式進行操作。

隨著PCB技術以及可以具有微通孔、埋入式通孔和盲孔的高速PCB設計方面的進步,探測感興趣的信號并對其進行調試已不再總是可行。結合更短的設計周期和更快的產品上市時間要求,硬件仿真(也被稱為信號完整性仿真)不再是可選的選項了。為了在第一時間開發出設計恰當的產品并節省在實驗室里調試有問題的PCB設計所需的大量成本和時間,它已成為不可或缺的要求。

在本系列課程中,我們會介紹與設計人員必須處理的高速PCB設計的各個方面相關的主題,并一起來了解硬件仿真如何有助于消除設計階段的猜測。撰寫本博客的目的是幫助設計人員在設計周期的早期捕獲并解決問題。這比起在實驗室里調試原型、經歷多個布局周期,并花費寶貴的時間、金錢和精力要更經濟、更有效。

Mentor Graphics Hyperlynx v9.4.2是一個SI仿真工具,將在本系列中用作一個幫助描述各種概念的機制。Hyperlynx 只是市場上的一種SI工具,還有許多其他供應商提供的其他工具。無論使用哪種工具,本系列中涵蓋的概念都保持不變。賽靈思對任何第三方 SI 工具均提供完美的支持,Hyperlynx 只是碰巧是本系列中用來詳細說明所涵蓋概念的工具。

SI仿真模型

我們先來看看可用于SI仿真的各種模型、它們之間的差異,以及在運行SI仿真時人們首選的模型。

SPICE模型:

SPICE代表以集成電路為重點的仿真程序。顧名思義,模型設計得非常詳細(詳細到到晶體管級別和工藝參數)。這些模型非常準確且非常復雜。然而,由于電路是在晶體管級進行描述的(這是專有信息),并非所有器件供應商都將這些模型用于SI仿真。還有一個限制,即并非所有SPICE仿真器都完全兼容。

賽靈思提供加密的HSPICE模型(UltraScale +系列除外),而這種模型需要使用Synopsys的HSPICE仿真工具進行運行。

IBIS模型:

IBIS代表I/O緩存信息規范,是用于使用純ASCII文本格式數據描述數字器件緩存區的模擬行為的標準。這些是行為級模型,表示用于輸入和輸出的典型、最小和最大外殼角的I/V特性和dV/dt。由于這些模型是沒有顯示適當數據的行為模型,所以他們是供應商發布的、用于模擬輸入/輸出(IO)的最流行的類型。它們還具有受所有SI工具支持的優勢及其易用性。

快速瀏覽IBIS模型中的重要部分:

報頭:包含模型的一般信息(諸如文件名、版本、源、注釋等這類信息)

組件:將器件中所有不同的模型組織到引腳

模型:描述各種緩存區的驅動和接收器的特征

定義封裝模型:描述器件的封裝模型,并提供器件引腳的RLC矩陣

IBIS規范v6.1(最新版本)包含IBIS文件的各種語法和標題描述的詳細描述,是了解IBIS模型的推薦文檔。如需下載,請訪問http://ibis.org/。

下圖對這兩種模型進行了比較:

| IBIS Models | SPICE Models |

|

- Blackbox with no transistor level information. - Fast simulation speed. - Compatible with all simulation tools. - Lower accuracy compared to SPICE simulations. - Easily available from vendors. |

- Circuit level with propriety transistor level information. - Slow simulation speed. - Most simulation tools are not fully compatible. - Highly accurate. - Not easily available and may need NDA. |

賽靈思IBIS模型適用于所有器件,可以從這里。這些模型本質上是通用的,不會將特定的封裝引腳映射到任何I/O標準模型。與ASIC不同的是,FPGA是用戶可編程的,除了少數專用引腳外,管腳是用戶特定的。

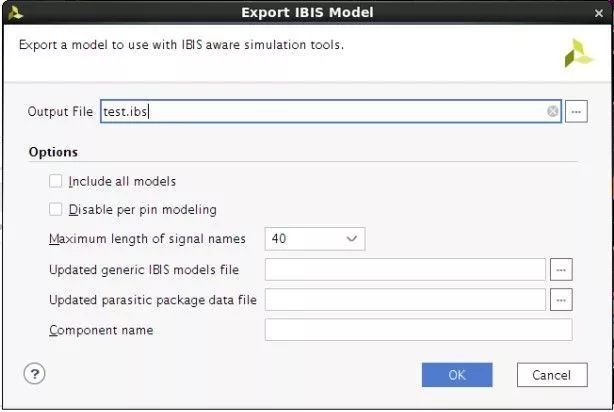

我們建議從Vivado Design Suite中獲取IBIS模型(該套件允許您生成IBIS模型)。Vivado使用設計中的網表和實現細節,并將該信息與可用的每引腳寄生封裝信息相結合,為設計創建定制的IBIS模型。

請記住,仿真結果僅與所提供模型的質量一樣好。從Vivado生成模型會為您提供一個映射到您的設計的I/O端口的IBIS模型,以及完全不會出現錯誤的最佳機會。

以下是以下列用例為例從Vivado生成IBIS模型的步驟:

1.有RTL設計:

如果您有RTL設計,請按照以下步驟操作:

打開精心設計、綜合或實現的設計。

要么a)單擊“File -> Export -> Export IBIS Models”。

要么b)在Tcl控制臺中使用以下語法運行“write_ibis”命令。

Write_ibis

Write IBIS models for current floorplan.

Syntax

write_ibis [-force] [-allmodels] [-nopin] [-truncate ] [ -component_name ] [-ibs ] [-pkg ] [-quiet] [-verbose]

2.沒有RTL設計:

如果您沒有RTL設計并且計劃使用管腳排列,請按照以下步驟操作。如果您不熟悉I/O管腳分配方面的詳情,請參閱(UG899)。

- 打開Vivado I/O Planning工程。

- 選擇器件。

-通過CSV或XDC文件導入此管腳文件。如-果沒有可用的管腳,請選擇“No I/O Ports at this time”選項。(注意:此選項將提供包含封裝數據的通用IBIS模型。)

-完成創建項目,系統隨即會打開封裝視圖。

-查看“I/O端口”標簽以確保已正確導入管腳。如果需要,運行DRC。

-要么a)單擊“File -> Export -> Export IBIS Models”。(見方法1)

-要么b)在Tcl控制臺中使用以下語法運行“write_ibis”命令:(見方法1)

3.基于Zynq MPSoC或Zynq-7000的設計:

如果只有Zynq器件的PS部分需要IBIS模型,您可以按照以下步驟操作:

- 在Vivado中啟動新的RTL工程并選擇目標Zynq器件和包。

-準備好新項目后,在IP集成器中創建塊設計。

-單擊“+”按鈕在IP選擇器窗口中添加IP,并根據所選器件系列選擇“Zynq UltraScale + MPSoC”或“Zynq7 Processing System”。

-相應的基于Zynq的塊將添加到圖表窗口中。

-雙擊Zynq塊打開“Re-customize IP”窗口。在“Re-customize IP”窗口中,選擇要在“Page Navigator”中設置的選項,并設置必要的參數,例如I/O配置、時鐘配置、DDR配置等。

-單擊“OK”,系統隨即會更新IP。右鍵單擊Zynq IP塊,然后單擊“Make External”。Vivado將自動添加到外部信號。

-要避免收到有關未分配地址的警告,單擊“Address Editor”窗口并單擊“Auto Assign Address”。

-在“Hierarchy”窗口中,單擊“Sources”標簽。右鍵單擊設計,然后單擊“Create HDL Wrapper”。

-選擇“Let Vivado manage wrapper”,然后單擊“OK”。

-當封裝完成后,在Flow Navigator中選擇“Open Elaborated Design”。系統隨即會打開一個對話框,該對話框中列出了有關Elaborated設計的詳細信息。單擊“OK”,然后打開細化設計。

-要么a)單擊“File -> Export -> Export IBIS Models”。(見方法1)

-要么b)在Tcl控制臺中使用以下語法運行“write_ibis”命令:(見方法1)

S-參數模型:

請輸入文字

過去,S參數(散射參數的簡稱)在頻域中使用得最為廣泛。然而,隨著今天的高速數字信號達到> 1 GHz的速度,S參數在SI仿真中被用作無源互連的行為模型,例如電阻器、電容器、PCB走線、背、連接器、電纜等。

大多數連接器和電纜供應商提供其產品的S參數,可用于在SI仿真中對其進行建模(尤其是在對多板接口進行仿真時)。大多數SI工具支持將S參數模型與IBIS模型相結合,以對接口進行端到端的仿真。

運行SI仿真所需的模型列表合并在下圖中。

| Transmitter (Tx) and Receiver (Rx) | IBIS Models |

| Lumped Elements (R, L, C) | Primitives within simulator or S-parameter from vendor if available. |

| PCB Traces | Transmission line primitive in simulator or S-parameter model if derived from a PCB layout file. |

| Connectors, Cables | S-Parameter models or IBIS models from the respective vendor. |

-

PCB設計

+關注

關注

394文章

4683瀏覽量

85558 -

完整性

+關注

關注

1文章

12瀏覽量

10319 -

SI仿真

+關注

關注

0文章

2瀏覽量

5421

發布評論請先 登錄

相關推薦

PCB設計各種信號完整性問題

PCB設計各種信號完整性問題

評論