如果你已經有了一個設計并且想將這個設計移植到另一款目標器件上,這篇文章將幫助你確定這種轉換所應遵循的步驟。

這篇文章不會涉及與原設計完全不同的轉換方式,從底層組件來看并非完全不同的。

對于這種轉換你應該遵循特定的轉換指南,比如UltraScale系列轉換為Versal系列器件,這篇文章的主題就是這種轉換的方法,轉換的方式通常是相似的。

設計的 RTL 部分

底層的RTL結構和Verfilog/VHDL代碼不需要任何更改。

大部分的實例化原語也不需要任何更改,Vivado工具將會用等效的實例化原語來進行替換來滿足目標設計的需要。

可能有一些特定的原語不能進行替換,這可能與最初組件的選擇和目標設計的結合有一定關系。對于這種情況,你就需要手動找到最接近的等效功能從而替換之前的原語模塊。

對RTL源碼進行一次綜合操作,不用擔心時序約束的正確性,甚至不用去考慮是否是最優的綜合。

然后仔細查看綜合操作的日志文件,如果你看到某些與無法綜合的原語相關的信息,那么這些原語就需要你親自來替換了。

還要注意那些關鍵的警告,如果某些原語被重新設計了,但是功能就可能得不到保證。

使用綜合操作的日志文件來確定可能需要修改是一種比較快速的方法,而不用遍歷所有的RTL源碼。

設計的 IP 部分

如果你的設計采用了IP模塊,首先你需要檢查來確定相同的IP在新的芯片上是否還能夠使用。

大部分軟核IP在新的目標器件上都應該能夠使用,然而硬核IP有可能就不適用了,當然這與選擇的器件有關。

你想做的第一件事就是“升級”你的IP組件。

檢查IP說明文檔或者IP升級日志,這些文件包含更改了哪些參數、管腳輸出等詳細信息,IP升級日志可以在你的工程目錄下找到。

對于采用的所有IP,你要快速檢查可以自定義的參數,通常IP的自定義配置可以保留不變,然而在新的設計結構中可能還需要一些額外的參數設置,當然一些參數可能不再適用了,你希望看到的是采用當前的參數設置每個IP的功能都能正常工作。

同樣的輸入管腳配置也需要修改,如果有必要的話你需要檢查管腳輸出,更改實例化IP組件的管腳連接。

然后“生成輸入文件”——面向新的器件

即使在修改不同組件之前已經執行了“生成輸入文件”操作,那些輸入文件可能不再有意義,因此需要重新生成。

設計的 IPI/BD 部分

整個設計的IPI/BD部分與IP部分應該非常的相似。

首先要檢查一下在BD中使用的IP模塊在目標器件上是否可用。

對于設計的BD部分,執行“報告IP狀態”操作,升級建議的IP模塊。一般來說它會將以對BD中使用的所有IP進行升級。

查看IP升級日志文件,其中包括需要更改哪些參數、輸入管腳等詳細信息,IP升級日志可以在工程目錄下找到。

檢查每個IP的參數,可能會增加一些新的參數,一些之前版本的參數可能棄用了,同樣的管腳輸出也需要修改。

如果管腳輸出被更改了,你應該能夠借助自動化連接操作來找回丟失的連接。

一旦BD部分為新的設計準備好了,那么就可以執行“驗證BD”操作了,驗證成功后執行“生成輸入文件”操作即可。

檢查BD級的管腳輸出是否仍然保持不變,否則就需要重新實例化BD模塊并且更新BD模塊的管腳連接。

I/O 管腳規劃和布局

如果有需要還要根據新的目標器件的管腳輸出重新執行I/O布局操作。

實現步驟

一旦IP(包括工程目錄下的和BD目錄下的)都進行了更新,那么整個設計還需要重新執行編譯操作,包括綜合(synthesis)和實現(implementation)等操作。

在驗證過程中還需要對實現策略、執行順序、管腳規劃布局以及LOC約束進行仔細的檢查。

最后感謝來自CortexRF公司的格倫·英格利希(Glen English)對本篇文章的建議,確認了設計轉換器件過程中要注意的事項和操作步驟,從而保證整個設計的正常工作。

-

轉換器

+關注

關注

27文章

8717瀏覽量

147382 -

IP

+關注

關注

5文章

1711瀏覽量

149639 -

器件

+關注

關注

4文章

312瀏覽量

27861

發布評論請先 登錄

相關推薦

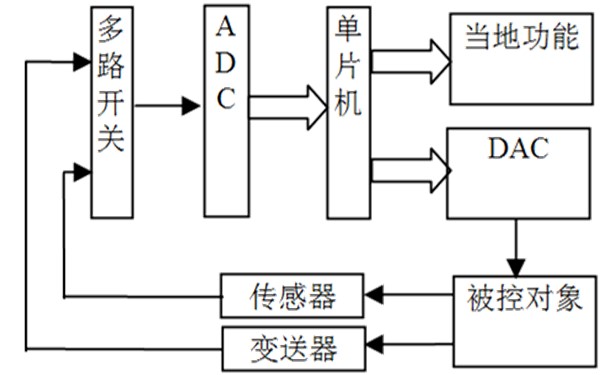

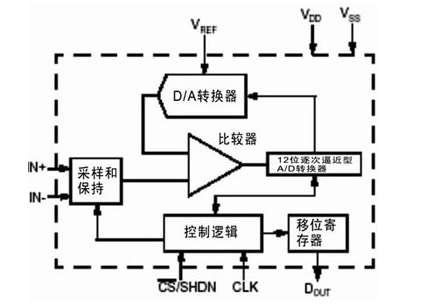

A/D轉換器概述及分類

數模轉換器是什么

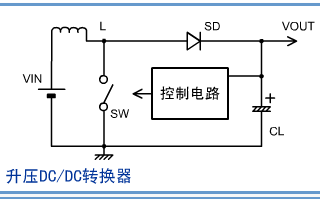

DC/DC轉換器,DC/DC轉換器是什么意思

模數轉換器和數模轉換器概述

如何選用DC/DC轉換器IC外圍器件?

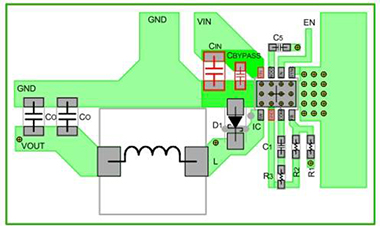

DC/DC轉換器的基板布局-DC/DC轉換器的PCB板布局概述

A/D轉換器所需的PCB布線策略

設計轉換器和器件移植概述

設計轉換器和器件移植概述

![RA6T2的16位模數<b class='flag-5'>轉換器</b>操作 [1] 簡介,A/D<b class='flag-5'>轉換器</b><b class='flag-5'>概述</b>](https://file1.elecfans.com/web2/M00/BB/1B/wKgZomWXtb6ACk_NAAARMuEl9ZA261.png)

評論