2011 年,我開始加入 Xilinx 公司,當時 Xilinx 正處于啟動從 ISE 到 Vivado 設計套件的轉型期。在 Xilinx 的最近幾年對我來說是一個非常棒的學習階段,除了學習到專業的技術知識,同時也看到了Xilinx不斷推陳出新,引領設計潮流。

Xilinx 努力做出的變化有:

1. 讓其FPGA或者SoC產品都能夠適用于ISE和Vivado工具。

2. 從輸入和輸出格式來講,讓Vivado工具盡可能的兼容行業標準(尤其是不同于ISE)。

3. 增加了功能更強大的算法和引擎支持,這也會帶來不同的結果。

在這段時間里雖然我看到很多熟悉ISE的老用戶正在從ISE轉向Vivado,但是對于那些熟悉行業標準和工具的新用戶而言,好像不那么順利。所以,在這里我分享一點兒我對Xilinx目前工具/解決方案的看法和技巧。同時也會有一些技術文章介紹Xilinx工具的使用方法或者解釋某個具體操作的原理和功能。

為什么CPR操作得出的效果卻是相反的?

在進行時序分析時片上工藝差別通常會導致嚴重的“時鐘悲觀效應”。這種問題可以通過CPR(Clock Pessimism Reduction)操作來恢復.然而經常有用戶咨詢我們說在他們的設計中CPR操作并沒有降低“時鐘悲觀效應”,效果卻是相反的,在時序上并沒有增加反而離時序要求差的更多了。

在setup分析時,CPR通常會被添加到目標(目的)時鐘路徑,因此增加了要求時間。然而因為在用戶的設計中CPR已經從目標時鐘路徑中移除,要求時間變得更早,而不是延后。結果就是用戶認為他們損失了時間,而不是獲得補償時間。其實實際情況是用戶沒有任何損失。

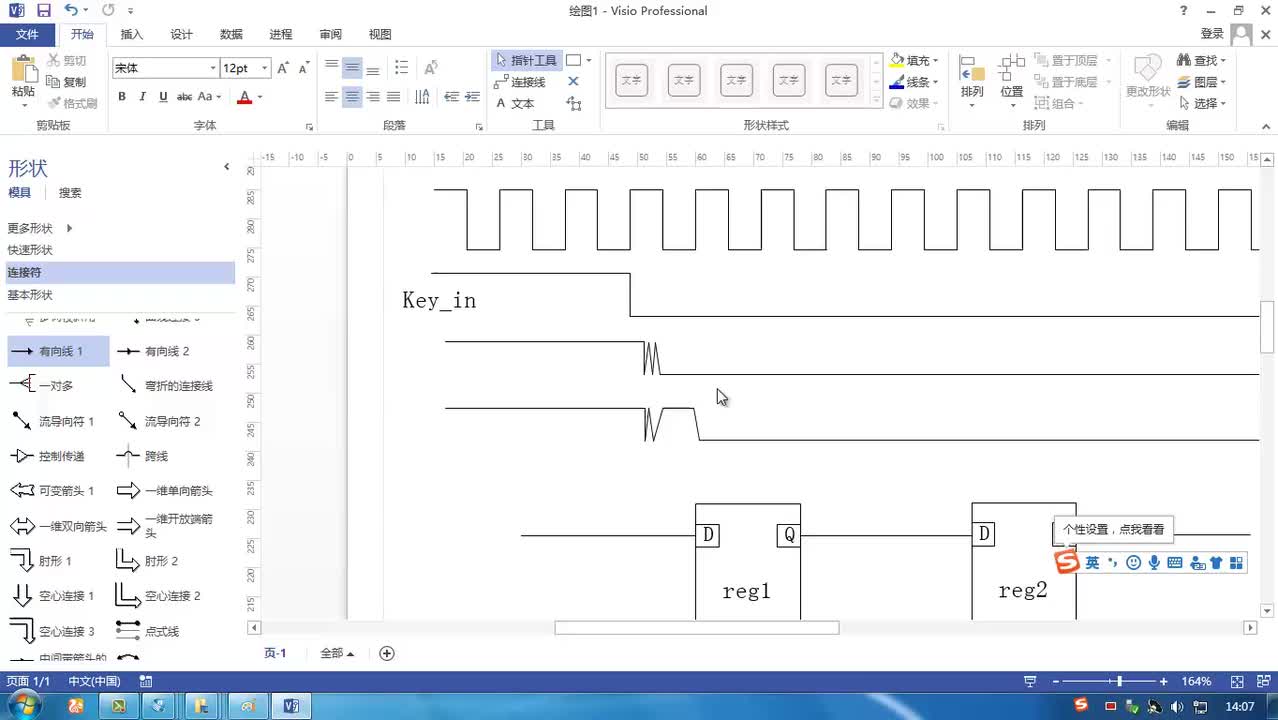

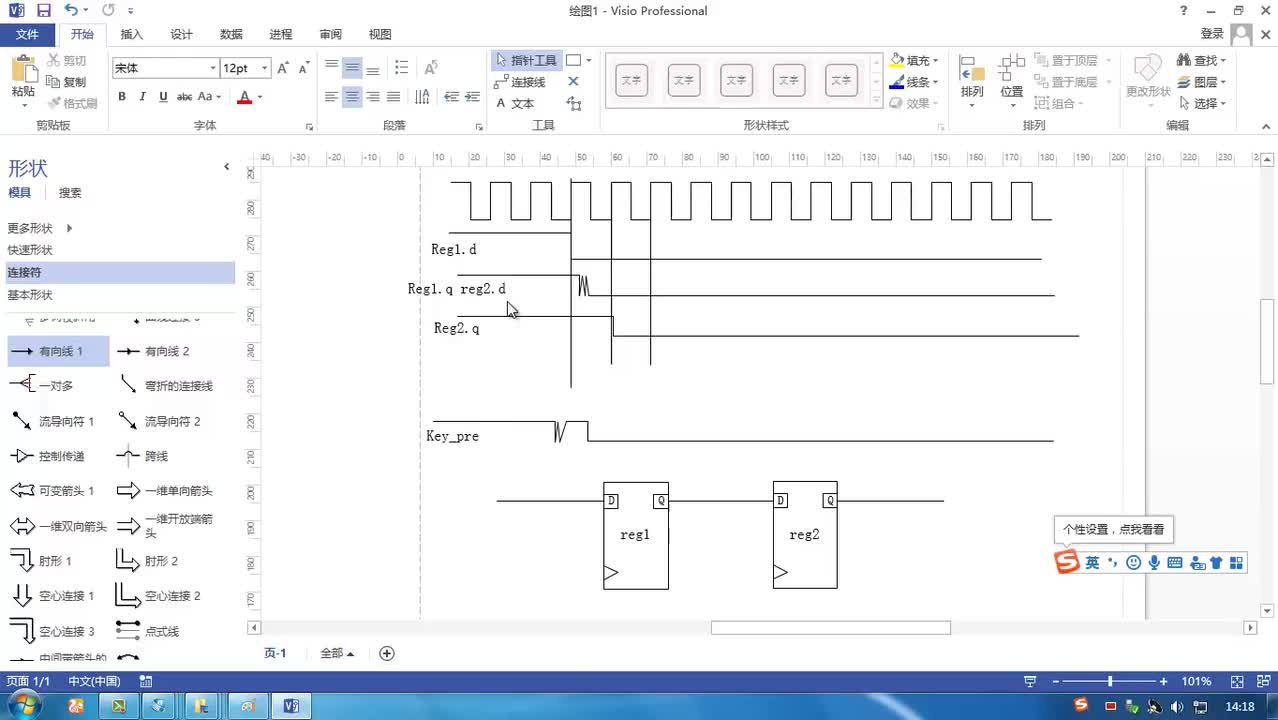

進行OCV分析時,源路徑和目標路徑被認為具有不同的延遲時間。然而對于兩者“共用”的路徑,其延遲時間是保持不變的。CPR補償了延遲差異,因此直到公用節點延遲數值變得一樣了。

為了能夠更好的理解發生了什么,請查看附件的時序分析報告。

(感謝Xilinx Tokyo的Matsuyama-san分享了他的一個示例設計的時序分析報告)

為了簡單易懂,這個報告作了一些修改。在MMCME3_ADV_X1Y2之前源時鐘和目標時鐘都共享一個公用路徑,然后源時鐘走向BUFGCE_X1Y48節點,而目標時鐘走向 BUFGCE_X1Y50節點。

讓我們明確一下公用節點前的延遲(Vivado認為MMCM的輸出作為公共節點,盡管兩種時鐘路徑的輸出管腳是不一樣的)。

讓我們看一下時序報告中源時鐘路徑:

時鐘起點是:0(時序報告的21行),到達MMCM的輸出端是-3.218(時序報告的31行)。因此公用節點前的延遲是-3.218。

對于目標時鐘路徑:

時鐘起點是:3.33(時序報告的41行),到達MMCM的輸出端是0.141(時序報告的50行),因此公用節點的延遲(目標時鐘路徑)是0.141-3.33=-3.189。目標路徑的延遲(-3.189)看起來要比源時鐘路徑延遲(-3.218)要大一些(注意負號,不要僅看到延遲的數值)。

因此目標路徑具有更高的延遲,需要進行補償。因此在目標時鐘中降低“時鐘悲觀效應”,這樣才能減少要求時間。

現在,源時鐘和目標時鐘在公用節點之前都具有了相同的延遲,也就是說用戶在公用節點(如示例中的MMCM節點)前沒有任何損失也沒有額外獲得什么。

這種相反效應的現象在MMCM節點中是存在的,相對UltraScale系列器件,這種情況在7系列器件中更是普遍存在的。

賽靈思公司工具與方法學應用專家,1993年畢業于印度理工學院電子工程專業,一直從事 VLSI 和 EDA 相關領域的工作。2011年加入賽靈思公司,專攻庫特性描述與建模,HDL,仿真與綜合,靜態時序分析以及跨時鐘域(CDC)與同步相關內容。

-

FPGA

+關注

關注

1630文章

21781瀏覽量

604936 -

時序分析

+關注

關注

2文章

127瀏覽量

22580

發布評論請先 登錄

相關推薦

用于Xilinx和Altera_FPGA的電源管理解決方案

AnDAPT為Xilinx Zynq平臺FPGA和SoC設備推出完整電源解決方案

Xilinx Virtex Ultrascale FPGA MGT電源解決方案

Xilinx 400GE解決方案的展示

MIPI和Xilinx MIPI解決方案的介紹

設計解決方案41-基于Xilinx FPGA系統的雙輸出DC/DC轉換器解決方案

Xilinx目前工具/解決方案的看法和技巧

Xilinx目前工具/解決方案的看法和技巧

評論