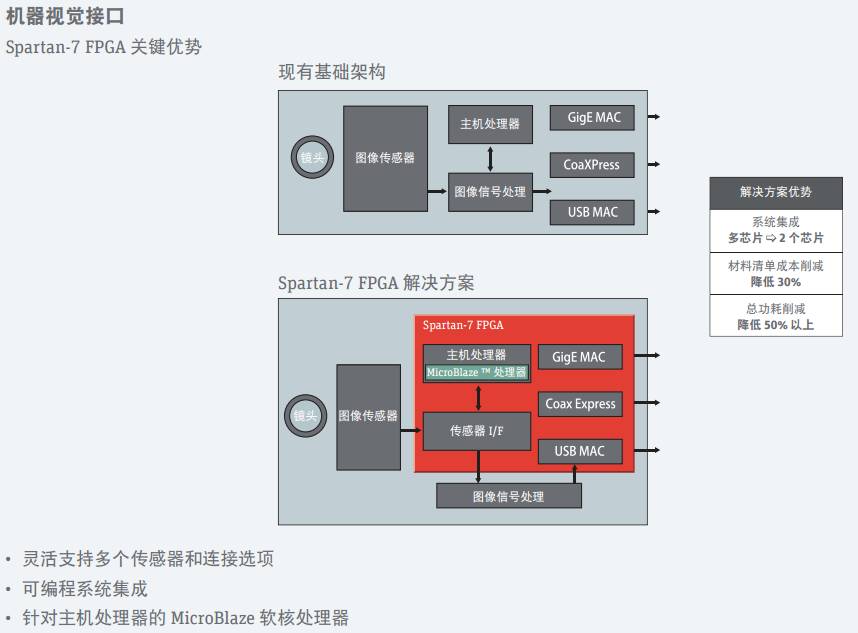

XilinxSpartan-7器件采用小型封裝并提供業界最高的性能功耗比,可滿足最苛刻的要求。這些器件采用 28nm 技術構建,是工業、消費類應用以及汽車應用的理想選擇,其中包括任意連接、傳感器融合以及嵌入式視覺等應用。

本白皮書(WP483)將詳細地向您介紹 Spartan-7 FPGA 的技術細節和架構優勢,從而讓需要滿足一些成本敏感型的市場的設計人員多一些選擇與可能。

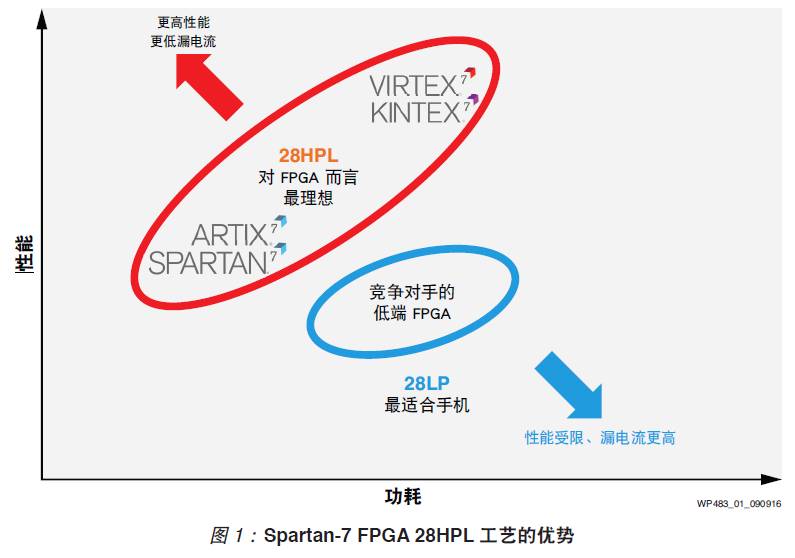

最佳工藝的選擇

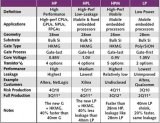

Spartan-7 FPGA 采用與成熟的 7 系列相同的 28HPL 工藝,以及眾多底層架構元件,從而使其成為結構緊湊的成本優化型 FPGA 系列器件。該產品系列具備很高的邏輯和 I/O 性能,功耗也得到嚴格控制,可采用很小的封裝,而且價格低廉。

為成功而構建的秘訣

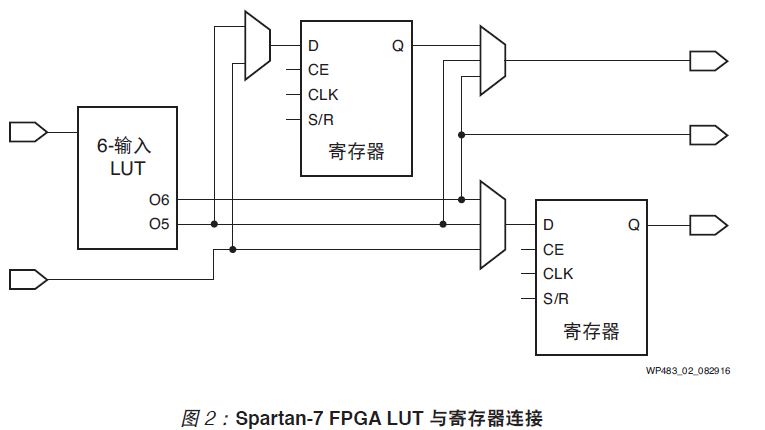

邏輯結構是所有 FPGA 架構的核心。邏輯單元是器件容量與功能的統一測量標準,設計人員要想理解用器件能做什么事情,還需要深入了解一下其中的構建模塊。

開展設計所需的工具

Vivado IDE 在提供簡單、按鈕式設計方法方面一直領跑整個行業,可提供眾多高級特性,以幫助設計人員快速構建面向 FPGA 和 SoC 的設計。可利用很多設計重用功能將針對某款器件或某個系列而構建的部分設計或 IP 打包,便于以后重復用于采用類似架構的另一款器件或系列。例如,設計人員可創建用在 Spartan-7 FPGA 中的 IP 核。隨著系統要求的不斷提高,設計人員可在 Artix-7 FPGA 中重用這一 IP 核。

Vivado Design Suite 支持 VHDL 2008、Verilog 和 System Verilog,允許用戶選擇自己最喜歡的語言來輸入 RTL 設計。創建設計后,可利用多種調試和驗證工具確保功能正確,包括一種免費的混合語言仿真工具(無代碼行限制)。

免費的 Vivado HL WebPACK Edition 支持所有量產級 Spartan-7 器件,為這些器件提供最快速、成本最低的工具。

-

FPGA

+關注

關注

1643文章

21944瀏覽量

613389 -

寄存器

+關注

關注

31文章

5412瀏覽量

123124 -

賽靈思

+關注

關注

33文章

1795瀏覽量

132086

發布評論請先 登錄

賽靈思Spartan FPGA平臺應用于香港應用科技研究院

賽靈思推出Spartan-7 FPGA系列密集型器件,能夠快速集成和實現

Xilinx Spartan-7 7S50器件性能和功耗優勢介紹

Spartan-7 FPGA產品資料簡介

賽靈思的Spartan-7 FPGA系列器件的關鍵功能介紹

評論