Robert Roe最近在Scientific Computing World網站上發表了一篇題為《OpenCL是否會為FPGAs開啟大門?》的文章,這篇文章關注了FPGA各種各樣不同的應用。他的文章包含了很多領域而不是僅僅局限于OpenCL。如果你對FPGA的印象還停留在20世紀,也就是說FPGA更適合來實現膠連邏輯,那么這篇文中的一些引用確實會讓你有所思考。以下就是來自于這篇文中的一些引述:

“FPGA剛出現的時候,它只能做一些非常基本的邏輯比如說布爾代數,那時它確實只是用來實現膠連邏輯的。但是在過去的這些年里,FPGA已經進步和進化了,它擁有了更多專用化的硬化結構。”

“在過去的這些年里,FPGA已經從實現膠連邏輯轉變為實現更加復雜的設計,比如說做了很多數字信號處理運算的radio head系統,高性能的視覺應用平臺,無線電,醫療裝備以及雷達系統。所以它們被用在高性能的計算中,一般用于特定算法的運算。”

“人們選擇用FPGA來做這些應用的理由很簡單,與利用軟件代碼實現這些應用相比,FPGA具有更低的單位功耗。”

—— Larry Getman,Xilinx戰略市場營銷計劃部副總裁

有這樣一個讓人糾結的問題。FPGA具有優越的性能和良好的功耗,但怎么樣讓那些不精通VHDL或者Verilog語言的開發者,更容易的享受到這些好處呢?

由定義可知,這些HDL(硬件描述語言)是用于描述硬件系統的語言,但系統描述不應限制于HDL這個詞,這恰好是目前流行的系統級描述語法。上世紀九十年代之前,電路圖作為一種描述語法可以被選擇。但是當數字系統變得過于復雜時,就不能用電路圖來描述,即使是分層次的電路圖也不行。同時,由于HDL編譯器變得越來越優秀,因此HDL開始被設計界接受并且保持了長達25年的統治地位。那是一個又好又長的過程,讓我們幾乎忘記了電路圖這種設計方法——一種在被HDL代替之前已經持續了差不多100年的設計方法。這一切都在緩慢地變化。

巧合的是,EEJournal的Kevin Morris最近發表了一篇題為《HLS是新的黑馬》的文章。在這篇文章中,Kevin寫道:“今天,你可以用C,C++,或者SystemC之類的語言寫一些行為性的代碼,然后把他們放在HLS工具中,然后迅速返回得到一個詳細的硬件設計,這個設計確實要比你自己花費好幾個月時間用RTL級描述法做出的設計好的多。這種方法的產出率是驚人的。一個優秀的硬件工程師如果使用HLS連續設計硬件,這跟一個沒有使用HLS的工程師相比,他的工作速度要提高5到10倍。同時,當一個使用了HLS的工程師想去做結構上修改的時候,他的工作量和做RTL級修改相比,是非常小的。”Morris幾乎可以很容易在25年前寫一篇關于HDLs的文章,一個HLS很接近的詞。

Xilinx最近發布了三個工具,統稱為SDx,目的是讓系統開發團隊使用除了Verilog和VHDL的其他描述語法和語言,來開發復雜的數字系統。Xilinx 的SDAccel 開發環境提供了類似GPU的工作環境,認可OpenCL,C和C++語言寫的代碼。這是專門為那些喜歡便利的GPU編程和追求速度,但是卻又不想在享用高性能的GPUs時,伴隨著高功耗的開發者而設計的。SDAccel應用于數據中心加速時,可以讓你系統的性能/功耗比提升25 倍。

在Scientific Computing World文章中,Getman寫道:“我們的目標就是讓FPGA像GPU一樣容易編程。以OpenCL為基礎的SDAccel,允許開發者使用OpenCL,C或者C++進行編程,而且他們可以以一個很高的層次來開發FPGA了。”

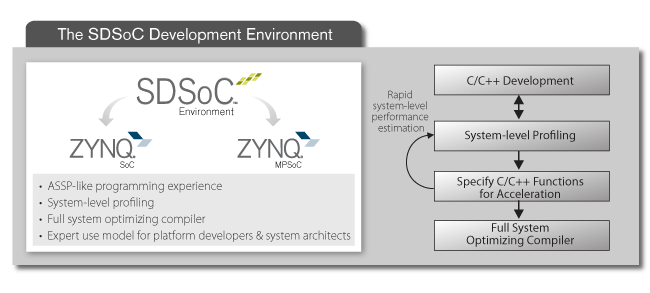

Xilinx發布的最新SDx是集成與SDSoC開發環境,SDSoC是業界第一個C/C++全系統優化編譯器。這是一個更加通用的開發平臺,提供系統級分析,可編程邏輯自動SW加速,系統連接自動生成,加速編程庫以及一個提供給客戶和第三方開發平臺開發者的設計流程。

SDx的第三個成員是更加專業化的SDNet。SDNet允許創建”軟“定義網絡,這項技術遠超今天的軟件定義網絡(SDN)架構。軟定義網絡支持SDN功能,同時也允許軟件可編程數據平臺硬件的差異,這種軟件可編程硬件平臺具有在處理包括性能,靈活性和基于內容的網絡安全挑戰方面能和控制平臺軟件動態地合作的內容智能。在與應用優化庫連接使用中SDNet系統描述是高等級規范的。SDNet將這些規范轉化成一個基于Xilinx全可編程器件的優化硬件實現。由此產生的設計實現了在最優成本,功耗和性能方面的線速處理。

SDNet也是復雜數字系統不需要從Verilog或者VHDL開始的另一有力證據。

現在如果你是硬件描述語言的發燒友,祝賀你,Verilog和VHDL將不會很快退出去。Xilinx 的 Vivado 設計套件提供了工業級的硬件描述語言編譯器,隨著每一個新的軟件版本的推出而變得更加地強大,尤其是在配合推出了Xilinx UltraScale 和UltraScale+器件時。SDx開發環境的設計不是取代硬件描述語言,而是補充它們。他們提供快捷和簡化的方式讓系統跑起來,讓它們更快地走出實驗室。請確信一點:在此之下的本質仍是真正的硬件描述語言。

-

C語言

+關注

關注

180文章

7606瀏覽量

137071 -

FPGA芯片

+關注

關注

3文章

246瀏覽量

39817 -

c語言編譯器

+關注

關注

0文章

5瀏覽量

7160

發布評論請先 登錄

相關推薦

賽靈思對OpenCL,C,和C++語言對FPGA和全SoC的作用詳解

賽靈思對OpenCL,C,和C++語言對FPGA和全SoC的作用詳解

評論