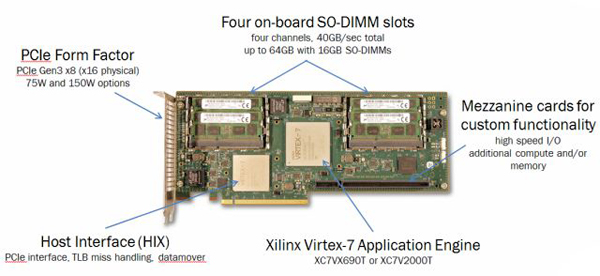

在New Orleans舉辦的超級計算機大會(SC14)上,Convey Computer公司介紹了很多關于HLL(高級語言)的標準擴展和利用FPGA實現加速的應用等內容。Convey公司制造了一整套的基于FPGA的硬件加速器板卡,支持PCIe計算接口和服務器系統包裹Wolverine(”金剛狼”),這些設計都是基于Xilinx Virtex-7系列FPGA芯片。Convey公司是目前幾個能夠提供加速器板卡商業成品的提供商之一,加速器板卡也是這次Xilinx公司推出的SDAccel開發環境的一部分。( 為OpenCL,C, C++打造類似于CPU/GPU的軟件開發環境)

基于FPGA的加速器應用Wolverine(”金剛狼”),支持PCIe系統

在SC14會議上Convey公司的展臺采用信息海報的形式,提供了大量關于使用高級語言(HLL)來加速基于FPGA的應用代碼的開發。下面我將引用海報的重點部分,以防你錯過了Convey公司的展臺,或者不能親自來New Orleans參加SC14會議:

以前加速器應用設計主要使用硬件描述語言(HDL)例如Verilog來進行程序設計。這就需要專門的技能和工具軟件,這就限制了這個器件不能被更多的人所接觸到。

最近,加速器編程標準已經推出,主要為便攜式應用的設計提供支持,這個標準主要面對不同提供商的加速器。這里我們介紹一下由Convey Computer公司開發的OpenMP編譯器原型和由Xilinx公司開發的OpenCL編譯器.(也就是Xilinx公司推出SDAccel開發工具軟件)

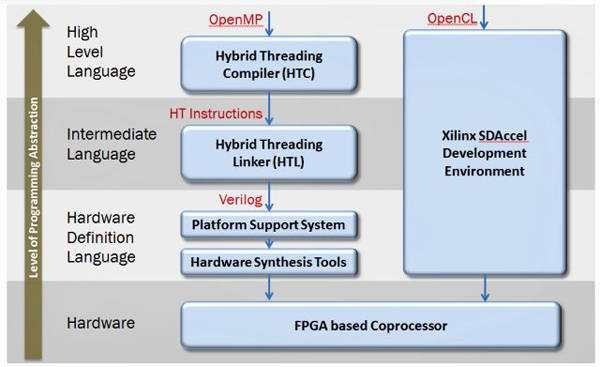

FPGA是一塊可編程的集成電路,通過編程可以實現不同的電路設計,這些設計是通過硬件描述語言(HDL)例如Verilog具體實現的,通過硬件綜合工具將硬件描述語言代碼轉換成比特流文件,下載到器件中完成對電路的配置。

Convey公司的OpenMP編譯器采用OpenMP4.0加速器指令,將它們轉換為公司的混合線程(HT)來表示。中間語言包括將基于C++和實時運行庫的高級編程指令相結合,主要是為了能夠訪問系統的底層設備。這個工具集將HT轉化為Verilog語言,很多工作都是自動完成的,包括創建復用并行單元和轉化工作順序表。生成的Verilog語言代碼和由硬件平臺提供的系統底層驅動代碼會被綜合生成比特流文件,最后將比特流文件下載到處理器中,完成配置。

Xilinx公司SDAccel開發軟件能夠實現將OpenCL應用代碼編譯成二進制文件,這些二進制文件是能夠被處理器所識別的,并執行,編譯過程采用標準的編程開發環境。下面的插圖展示了這兩種編譯器是怎么工作的:

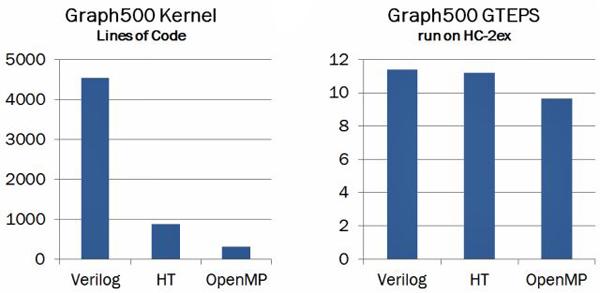

使用高級編程工具將需要更少的代碼來實現功能的描述,這就可以讓程序員將更多的精力放在算法的研究上,而不是為搭建一些底層驅動傷腦筋。

例如,手工實現的Graph500廣度優先搜索內核使用Verilog語言大概包括超過4500多行的代碼,同樣的內核實現使用混合線程(HT)中間過渡語言只需要883行代碼。使用OpneMP版本的內核只需304行C語言代碼,使用OpenMP實現的內核性能是9.7 GTEPS,使用Verilog語言的內核性能是11.4GTEPS,使用HT語言的內核性能是11.2GTEPS,相比較而言還是可以接受的。

從這個例子所顯示出的意義來看,使用OpenMP代碼實現的簡單內核性能完全可以與Verilog語言實現的內核性能相匹敵,例如Graph500,使用OpenMP實現的版本可以達到Verilog語言實現版本性能的85%,但是卻只需要更少的代碼量。

這次對高級語言標準擴展的介紹允許將基于FPGA的加速器應用的程序設計大大簡化。基于這些標準的編程工具可以生成高度并行的硬件設計,而且性能完全可以與采用底層硬件描述語言實現的設計性能相匹敵。

---> END <---

-

超級計算機

+關注

關注

2文章

472瀏覽量

42491 -

C語言

+關注

關注

180文章

7633瀏覽量

141972 -

加速器板卡

+關注

關注

0文章

2瀏覽量

2314

發布評論請先 登錄

無法導入硬件加速器

高級語言(HLL)標準擴展大大簡化基于FPGA加速器的應用程序的開發

Bitfusion支持通過云訪問基于賽靈思All Programmable器件的FPGA硬件加速功能

利用硬件加速器提高處理器的性能

賽靈思公司與SK電訊技術結合,加速FPGA加速器在AI領域的應用

基于Xilinx FPGA的Memcached硬件加速器的介紹

賽靈思公司與SK電訊宣布SKT已在其數據中心中部署賽靈思FPGA

Vitis在Alveo 板卡上加速應用案例

評論