親愛的讀者,我能問你們一個私人問題嗎?這樣才公平,你們知道這么多關于我的事情,所以我也需要了解一下你們…為什么你們仍然在手工編寫FPGA設計?(當然,你們不會再去手工編寫一些接口,比如PCIe、SRIO、DDR、GbE、JESD204B、HMC......)是這樣嗎?好的,那么為什么你們還在對世界上最好的、最了不起的Xilinx的FPGA的內核進行手工編碼?是的,我確實說的是世界上最好的FPGA,在DSP、IO、SoC以及IP等方面都是最好的…那么你打算如何使用Xilinx Kintex-115器件中5520個DSP所提供的8 TMACS計算能力呢?這是FPGA領域中帶寬最大和速度最快的。

我們變得很安逸,不是嗎?工程師們都不喜歡冒險和失去控制。我之前曾經說過這個,但我自2011年以來就一直都沒有用C/C++手工編寫過一個DSP的功能。讓我們來看看Xilinx Virtex-II Pro器件中的232個DSP,我們都會為之喝彩,“這就是我們想要的,不可能寫出比它更好的了”!

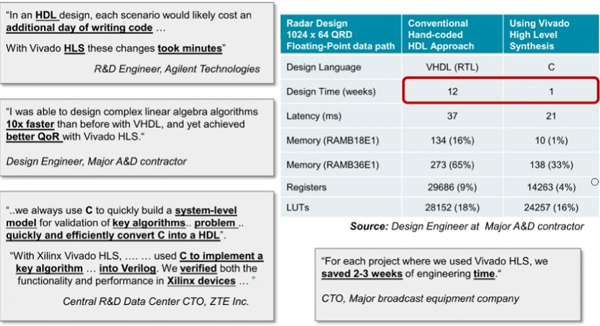

一個有著8塊電路板,每塊板上有3個Virtex-II Pro FPGA器件的VME,現在只需要幾個UltraScale FPGA器件就能實現了,我想我們都同意這個說法。這是令人震驚的事,但是,是誰在做固件設計呢?這就是問題所在。因為FPGA Blob持續地對周邊的功能造成影響,所以如何去設計一個這樣的系統并把它集成到FPGA中,對設計人員來說,這就是一個非常艱巨的任務。當我還是一個RADAR/EW工程師時,碰到的通常都是數學并行計算的問題。FIR濾波器、FFT算法、DFT算法、復數乘法、QR分解、CFAR等等等等…VHDL或者Verilog編碼會讓你按時地、在預算之內完成任務嗎?我并不想破壞你的美夢,但這很可能做不到;而如果你的競爭對手正在使用Xilinx的Vivado HLS(高層次綜合),那你的美夢就更會變成噩夢了。

Vivado HLS可以處理定點或浮點數據類型,所以你需要去核定那個自適應波束成形器怎么實現嗎?你可以很容易地在幾個小時內設計出一個QR分解內核,可以處理實數和復數。從設計RADAR的角度看,這意味著你可以在一片Xilinx UltraScale FPGA中采用定點或者浮點設計出整個波束成形器、脈沖壓縮器以及多普勒頻率濾波器。這個想法可以應用到你所渴望的任何功能實現上。

上面的結果都是真實的案例,他們都體驗到了Xilinx Vivado HLS的強大,體會到HLS是戰勝競爭對手的關鍵。因為仿真是采用編譯好的C/C++可執行文件,而不是RTL仿真,因此整個設計時間大大縮短了。設計中的數學計算、延遲、器件使用情況和時鐘頻率都可以在幾分鐘內驗證完畢。對RADAR系統中的一個多普勒頻率濾波器卡進行RTL仿真,要花去幾天的時間,然后要花幾周時間去找出缺陷,修復設計。如果采用C/C++,仿真時間則是以秒來計算的。HLS設計也可以進行修改,并且非常方便。用在Xilinx FPGA的可編程邏輯上的代碼可以很容易就編譯到Zynq的ARM內核上,時間上的變化很象是以前從匯編語言移植到編譯器那樣。

現在是時候開始使用Vivado HLS了,它是Xilinx FPGA設計人員工具箱中最有價值的工具。打敗你的競爭對手的秘訣,可能就在這個“武器”里面。

-

FPGA

+關注

關注

1629文章

21751瀏覽量

604115 -

電路板

+關注

關注

140文章

4965瀏覽量

98126 -

DFT

+關注

關注

2文章

231瀏覽量

22756

發布評論請先 登錄

相關推薦

matlab的其他工具箱及SIMULINK

***工具箱下載5.8最新版

matlab的其他工具箱及SIMULINK

matlab常用的工具箱

FPGA設計中的HLS 工具應用

怎樣改善塑料工具箱的鉸鏈

普查工具箱有哪些以及植保儀器工具箱系列的匯總

MATLAB自動駕駛工具箱使用

Vivado HLS--Xilinx FPGA設計人員工具箱中最有價值的工具

Vivado HLS--Xilinx FPGA設計人員工具箱中最有價值的工具

評論