摩爾定律象一盞明燈推動(dòng)半導(dǎo)體業(yè)進(jìn)步,特征尺寸縮小立下汗馬功勞。然而現(xiàn)階段尺寸縮小已近極限。從技術(shù)路徑,自22nm及以下開始由平面晶體管進(jìn)入三維finFET結(jié)構(gòu),之后finFET技術(shù)成為主導(dǎo),有可能一直能推進(jìn)至近3nm,屆時(shí)晶體管的架構(gòu)可能要改變,由finFET轉(zhuǎn)向環(huán)柵(GAA),納米片(nanosheet)等架構(gòu)。時(shí)至今日5nm技術(shù)已經(jīng)在手,將于2020年開始試產(chǎn),然而對(duì)于3nm技術(shù),目前仍處于研發(fā)之中,一切尚待觀察。

不容置疑,全球代工業(yè)在進(jìn)入邏輯制程7nm之后已經(jīng)開始生變,由于研發(fā)費(fèi)用及成本高聳等因素,2018年格羅方德與聯(lián)電聲言止步,因此導(dǎo)致全球代工業(yè)中只剩下臺(tái)積電,三星,英特爾及中芯國(guó)際四家在列,而其中的英特爾在商業(yè)代工業(yè)中是個(gè)“小角色”,以及中芯國(guó)際尚未明確它的時(shí)間表,所以全球只剩下臺(tái)積電及三星兩家在代工中爭(zhēng)霸。

5納米是個(gè)坎

眾所周知,7nm是長(zhǎng)壽命工藝節(jié)點(diǎn)之一,目前臺(tái)積電及三星均稱已經(jīng)量產(chǎn),而臺(tái)積電宣稱它拿到全球幾乎100%的7nm訂單。

臺(tái)積電的5nm finFET計(jì)劃已經(jīng)明朗,它計(jì)劃2020年上半年開始試生產(chǎn),估計(jì)真正的5nm量產(chǎn)要在2021年,或者之后。臺(tái)積電的5nm技術(shù)相比7nm,它的速度快15%,及功耗低30%。TSMC計(jì)劃它的5nm的第二個(gè)版本也將于2020年中期推出,預(yù)期它的速度能再快7%。

根據(jù)ICKnowledge及TEL的數(shù)據(jù),基于FinFET技術(shù),對(duì)于7nm的代工工藝,它的柵間距在56nm到57nm及金屬連線間距在40nm。

與此同時(shí),三星最近也高調(diào)推出了5nm,預(yù)計(jì)將于2020年上半年量產(chǎn)。與它的7nm相比,三星的5nm finfet技術(shù),與7nm相比它的速度有25%的增長(zhǎng),功耗降低20%,性能提高10%。

預(yù)計(jì)到2020年時(shí),蘋果、海思和高通等都將采用5納米的產(chǎn)品設(shè)計(jì),推動(dòng)臺(tái)積電加速向5nm技術(shù)過渡,”國(guó)際商業(yè)戰(zhàn)略(IBS)首席執(zhí)行官漢德爾?瓊斯(Handel Jones)表示。“到2020年第四季度時(shí),TSMC 的5nm晶圓產(chǎn)能將達(dá)到每月40,000至60,000片。”

然而估計(jì)臺(tái)積電5nm的訂單會(huì)低于7nm。因?yàn)榕c7nm相比,5nm完全是一個(gè)全新的工藝節(jié)點(diǎn),它需要新的EDA工具和IP等支持。這樣導(dǎo)致5nm的成本會(huì)更高。根據(jù)Gartner的數(shù)據(jù),一般來說,5nm產(chǎn)品的設(shè)計(jì)費(fèi)用約2.1億美元到6.8億美元。

臺(tái)積電首席執(zhí)行官魏哲家在近期的一次電話會(huì)議上說:N6和N5的數(shù)字看起來很接近,但是仍有很大的差別。與N7相比,N5的邏輯密度增加了80%。而N6與N7相比僅為增加18%。因此,N5芯片的總功耗較低。如果愿意跟進(jìn)N5,它有很多好處,而且是一個(gè)完整的工藝節(jié)點(diǎn),但是客戶需要時(shí)間來重新設(shè)計(jì)新的產(chǎn)品。而N6的美妙之處在于,如果他們已經(jīng)用過N7的設(shè)計(jì),那么只需花費(fèi)很少的精力,就可以很快進(jìn)入N6并獲得一些好處。所以根據(jù)他們的產(chǎn)品特點(diǎn)和市場(chǎng)情況,(客戶)將作出選擇。

3納米技術(shù)復(fù)雜尚不確定

IMEC的邏輯工程主管Naoto Horiguchi說:“5nm仍然是finFET。“”然后,假設(shè)進(jìn)入到N3時(shí),可能會(huì)從finFET過度到其他的器件架構(gòu),我們相信它是一種納米片nanosheet。”

在 5nm之后,下一個(gè)完整技術(shù)節(jié)點(diǎn)為3nm,但是導(dǎo)入3nm是十分困難的。據(jù)IBS宣稱,設(shè)計(jì)3nm產(chǎn)品的費(fèi)用約5億美元到15億美元,及它的工藝開發(fā)費(fèi)用約40億美元到50億美元,而如果要興建一條生產(chǎn)線的運(yùn)營(yíng)成本約150億美元到200億美元。IBS的瓊斯說:“基于相同的成熟度,3nm的晶體管成本預(yù)計(jì)將比5nm高出20%到25%。“與5nm finFET相比,預(yù)期性能提高15%,功耗降低25%。

三星是迄今為止唯一宣布其3nm計(jì)劃的公司。對(duì)于這個(gè)技術(shù)節(jié)點(diǎn),代工將采用一種新的環(huán)柵(GAA)技術(shù),或稱為納米片(nanosheet)。由于臺(tái)積電尚未披露其計(jì)劃,一些人認(rèn)為它可能落后于三星。“在3nm,三星在2021年有很大的可能性開始大規(guī)模生產(chǎn),”IBS的瓊斯說。“臺(tái)積電正在加速推進(jìn),試圖縮小與三星的差距。”

而臺(tái)積電此次3納米的制程技術(shù)顯得有些穩(wěn)重,它僅宣稱進(jìn)入實(shí)驗(yàn)階段。據(jù)報(bào)道為迎接它的3納米廠研發(fā)及先期量產(chǎn),中國(guó)***地區(qū)環(huán)保署于6月11日初審?fù)ㄟ^竹科寶山用地?cái)U(kuò)建計(jì)劃。另外臺(tái)積電也首度透露,預(yù)計(jì)把5年后(2024年)的2納米廠研發(fā)及量產(chǎn)都落腳在竹科,以避免研發(fā)人才散落或外流的風(fēng)險(xiǎn)。

張忠謀先前曾表示,3納米制程將在2年內(nèi)開發(fā)成功,即使有“摩爾定律”失效挑戰(zhàn),2納米仍可能在2025年前問世。

環(huán)柵極(GAA)的結(jié)構(gòu),顧名思義,是FinFET中的柵極被三面環(huán)繞的溝道包圍,而在GAA中柵極將是被四面溝道包圍,預(yù)期這樣的結(jié)構(gòu)將達(dá)到更好的供電與開關(guān)特性。只要靜電控制能力增加,則柵極的長(zhǎng)度微縮就能持續(xù)進(jìn)行下去,摩爾定律重新獲得延續(xù)的動(dòng)力。

據(jù)報(bào)道,在納米片的制程中,第一步是在襯底上交替的沉積薄的硅鍺層和硅層的生長(zhǎng)。在這種情況下,有硅,硅鍺和硅堆,我們稱之為超晶格結(jié)構(gòu),應(yīng)用材料工程管理高級(jí)總監(jiān)金南成(Namsung Kim)在最近的一次采訪中說。因?yàn)橛墟N的含量,需要有一個(gè)良好的屏蔽襯層。”

這樣每一個(gè)Stack由三層SiGe和三層硅組成。然后,在stack上設(shè)計(jì)微小的片狀結(jié)構(gòu),緊接著再形成淺溝隔離結(jié)構(gòu),以及形成內(nèi)間隔區(qū)(inner spacers)。

然后,在超晶格結(jié)構(gòu)中去除硅鍺層,在它們之間留下帶間隔區(qū)的硅層。每一個(gè)硅層構(gòu)成器件中的納米片或者溝道的基礎(chǔ)。下一步是為沉積高K材料作為柵極。在納米片之間,有最小的間隔區(qū)。挑戰(zhàn)在于如何沉積有功函數(shù)的金屬厚度。

產(chǎn)業(yè)多年來一直在攻克環(huán)柵結(jié)構(gòu),仍存在一些挑戰(zhàn),最主要的挑戰(zhàn)是什么,有兩個(gè)。一個(gè)是間隔層,然后是底部的隔離。

業(yè)內(nèi)人士進(jìn)一步表示,臺(tái)積電已經(jīng)做出環(huán)柵極的結(jié)構(gòu),外型就像個(gè)園形鼓,因?yàn)槌叽绫惹耙淮s小30%,它必須導(dǎo)入新材料InAsGe nanowire 或者 Silicon nanowire,因此制程技術(shù)上相當(dāng)困難,尤其在蝕刻部分是個(gè)大挑戰(zhàn),不過以優(yōu)勢(shì)來說,環(huán)柵極的結(jié)構(gòu)將可以改善ESD靜電放電、且優(yōu)化尖端放電的問題,材料廠的高管也認(rèn)為,環(huán)柵極的結(jié)構(gòu)可以繼續(xù)微縮柵長(zhǎng)尺寸。

什么時(shí)候過渡到環(huán)柵或納米片?估計(jì)納米片技術(shù)能再延伸2-3個(gè)工藝節(jié)點(diǎn)。

從研發(fā)角度,產(chǎn)業(yè)界正走一條在先進(jìn)工藝節(jié)點(diǎn)時(shí)延伸環(huán)柵及finFET結(jié)構(gòu)。因?yàn)榄h(huán)柵結(jié)構(gòu)與finFET相比性能方面僅是適當(dāng)?shù)奶岣撸鏘MEC開初的納米片工藝,柵間距42nm及金屬線間距為21nm。相比5nmfinFET工藝時(shí)柵間距為48nm及金屬線間距為28nm。

在實(shí)驗(yàn)室中IMEC已經(jīng)開發(fā)出用鍺作溝道的P型,雙堆壘環(huán)柵的器件。幾乎釆用同樣的結(jié)構(gòu)IMEC開發(fā)一個(gè)柵長(zhǎng)近25nm的納米線。它可以變成納米片,如同之前的版本它的線寬為9nm。

在5nm以下鍺可以起到延伸finFET的功能,IMEC證明Ge n FinFET達(dá)到創(chuàng)記錄的高Gmsat/SSsat及PBTI可靠性。它是通過改變柵的高k材料工藝來實(shí)現(xiàn)。

然而,仍有待觀察的是finfet技術(shù)能否會(huì)擴(kuò)展到3nm,同樣還不能預(yù)言納米片是否會(huì)準(zhǔn)時(shí)出現(xiàn)。事實(shí)上,在不斷變化的環(huán)境中,存在許多未知和不確定性。

本文來自求是緣半導(dǎo)體,本文作為轉(zhuǎn)載分享。

-

三星電子

+關(guān)注

關(guān)注

34文章

15860瀏覽量

180990 -

臺(tái)積電

+關(guān)注

關(guān)注

44文章

5632瀏覽量

166416 -

FinFET技術(shù)

+關(guān)注

關(guān)注

1文章

11瀏覽量

7728 -

5納米

+關(guān)注

關(guān)注

0文章

27瀏覽量

4863 -

莫大康

+關(guān)注

關(guān)注

0文章

53瀏覽量

5203

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

臺(tái)積電2025年繼續(xù)漲價(jià),5/3納米制程產(chǎn)品預(yù)計(jì)漲幅3~8%

HV-CMOS工藝制程技術(shù)簡(jiǎn)介

BCD工藝制程技術(shù)簡(jiǎn)介

PMOS工藝制程技術(shù)簡(jiǎn)介

臺(tái)積電3/5納米制程技術(shù)漲價(jià)計(jì)劃:引領(lǐng)半導(dǎo)體行業(yè)新趨勢(shì)

臺(tái)積電回應(yīng)先進(jìn)制程漲價(jià)傳聞:定價(jià)以策略為導(dǎo)向

淺談半導(dǎo)體制造的前段制程與后段制程

釋放前所未有的能效:瑞薩先進(jìn)的110納米制程技術(shù)

英特爾宣布推進(jìn)1.4納米制程

臺(tái)積電領(lǐng)跑半導(dǎo)體市場(chǎng):2納米制程領(lǐng)先行業(yè),3納米產(chǎn)能飆升

三星啟動(dòng)二代3納米制程試制,瞄準(zhǔn)60%良率

江蘇路芯半導(dǎo)體建設(shè)130nm-28nm制程半導(dǎo)體掩膜版

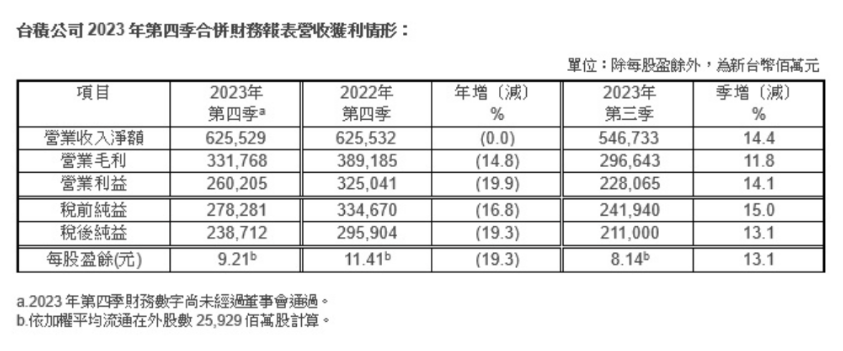

臺(tái)積電2023年Q4營(yíng)收穩(wěn)健,先進(jìn)制程營(yíng)收占比高達(dá)67%

5納米制程是個(gè)坎,半導(dǎo)體先進(jìn)工藝制程路漫漫

5納米制程是個(gè)坎,半導(dǎo)體先進(jìn)工藝制程路漫漫

評(píng)論