跟李凡老師學FPGA擴頻通信D01:串行通信基礎(課堂筆記)

用笨筆頭整理課堂筆記,用以備忘,溫故而知新。

整理文稿的細節處未能一一體現李凡老師講課精髓和獨特風采,有待下一步補充完善。

感謝李凡老師博大精深的學識、孜孜不倦的教誨,并敬請李凡老師原諒本人拙劣的課堂筆記。

近期精彩課程安排如下圖。

實際執行可能會有所調整,謹供參考。

從今天開始呢,我們進入通信的課程。

FPGA的應用,其中有很大一個比例,是用在通信上。

據說DSP的一些架構,就是跟FPGA的Altera的通信的用戶有關。

所以說呢,FPGA非常重要的一個應用方向,和通信密不可分。

通過這門課程的討論,我們來了解通信的一個基本的規則,基本的方法,工具,還有通信里面一個一個的技術。

我們通過像WiFi、藍牙,以及我們的移動通信里面普遍應用的擴頻,我們做個討論。

我們雖然說的是通信,communication,但實際上呢,它的含義,不僅僅是跟信息的傳輸、收發直接關聯,像移動通信、遠程的數據通信、互聯網的通信,像巡航導彈,設備和設備之間的通信。

這些通信呢,我們可以用communication來概括,沒有問題。

但是呢,它也有更廣義的含義。它不僅僅指的是數據收發端的通信,也指的是邏輯和邏輯之間,芯片和芯片之間,信息的交互。

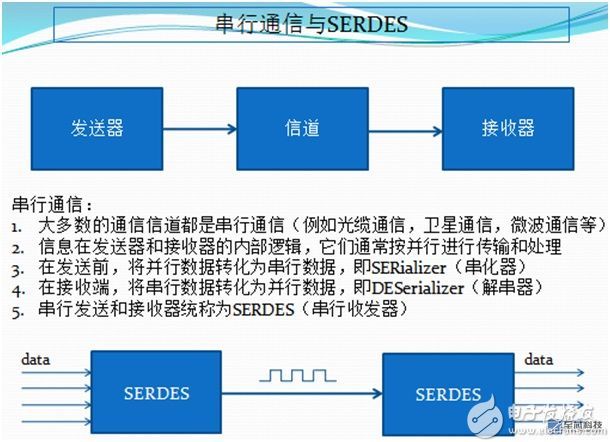

我們今天要說的通信,指的是串行通信。

什么是串行的?

什么是并行的呢?

我們用過并行打印機,我們知道,一端通過并行電纜接到電腦上。

它可以在同一個時鐘節拍發送總線信號。

我們現在介紹的是串行通信。

所謂串行,就是在單位時間內,只有一個比特信息的傳輸。

而并行呢,是在指定的時刻,會有若干個比特被發送。

我們現在的通信,大多數都是建立在串行通信的基礎上。

比方說,像光纖通信。

衛星也是,微波也是。

為什么我們在真實的通信系統里面,大多都用串行通信?

其實理由很簡單,一,有一個成本的問題。并行打印機,如果就在我們邊上,我們用一個并行電纜就行了。

但是光纜不同了,像海底光纜,一走幾百公里,它一個信道就是一個成本。

這是一個理由。

還有,像衛星通信,在指定的頻道上,特定的時刻,只有一個比特的加載。

如果要想同時加載多個比特的話,你會用多個頻道來傳輸,這樣的話,衛星的收發器的成本就要提升。

限于成本,衛星的收發器限制在單一的頻道上發送數據,那么指定的時刻,只可能是一個比特。

所以說衛星通信只可能是串行通信。

微波通信也是如此。

這些通信都涉及到,在單位時間,只有一個比特的加載,就是串行通信。

另外呢,我們說有第二個理由,更重要的理由,因為現在通信的速度是越來越高,越來越快。

并行通信看起來很快,一個比特可以有多個信號的加載,但是它有一個非常嚴峻的問題,就是窗口問題,當我們的并行總線有16根線的時候,在一個時鐘節拍下面,16根線都會翻轉。

必然有的翻轉快,有的翻轉慢。

這16根線必須要全部翻轉完了以后,這才得到有效的數據,下一拍也是如此。

這樣的話呢,就會形成一個窗口。

最后一個比特,構成了有效窗口的左邊界,以及窗口的第一個比特,構成了這個窗口的右邊界。

窗口的左邊界和窗口的右邊界,構成了窗口的寬度。

有效窗口的寬度,就一定會小于時鐘周期。使得并行的高速傳輸受限。

在其它一些高端課程,我們也會體驗到窗口效應。

正是由于這些原因,大多數的通信都是串行通信。

說到通信,我們就不可避免地要提到一個人。

現代通信,都是數字通信。在沒有電子設備之前,人類的通信主要靠喊。

還有信鴿、烽火、狼煙等等。

但是有了電子管以后,馬可尼的第一次跨洋通信,電報通信。

用摩爾斯碼來傳送。

它仍然是模擬的。

再后來,愛迪生發明了電話之后,仍然是用模擬的方法來傳輸。

是模擬的信道。

這類通信仍然是稱之為模擬通信。

到了二戰快結束的時候,美國貝爾實驗室的通信也得到了長足的發展。

格雷碼的發明就是在跟日本人的島嶼之爭的時候,用于通信的加密。

它是做成一個像示波器的加密體系。

一個示波管里面就是一個加密的芯片。

格雷碼的示波管發明出來以后,被日本人俘虜之前,趕緊把示波管給摘了。

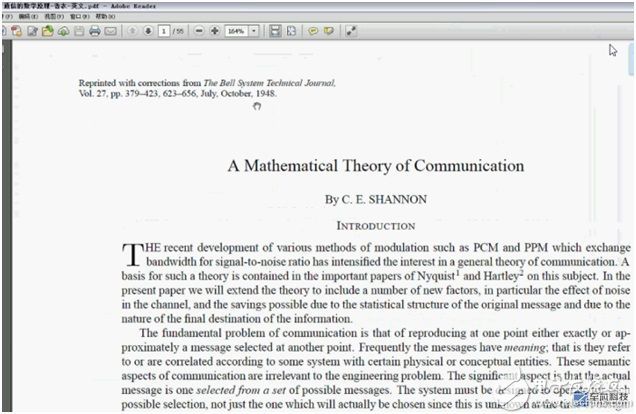

這個呢,我們就必須要說到,數據通信的創始人、奠基人,就是美國貝爾實驗室的工作者,其中最著名的就是香農。

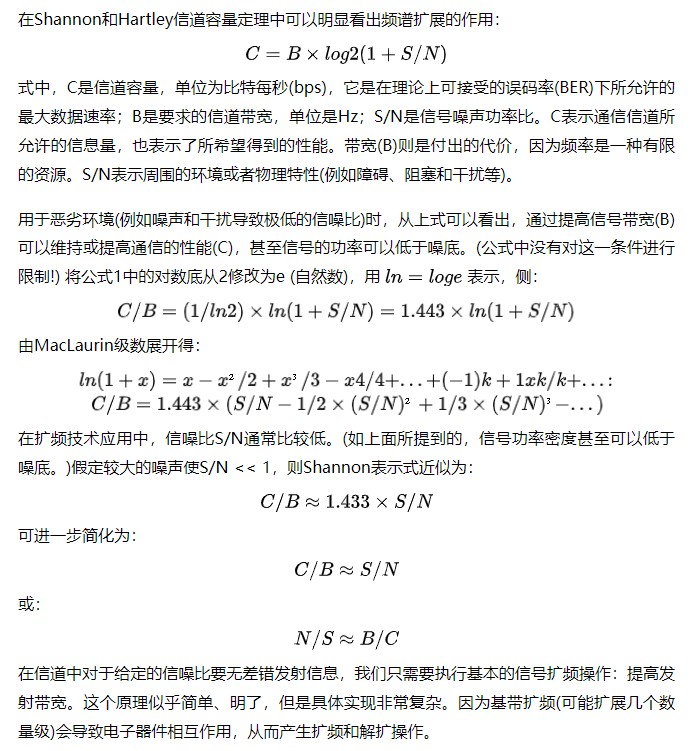

大家都知道香農定理。

打開文檔。

這是原文。

這是1948年發表的,在貝爾實驗室。

它仍然有它的意義。

這篇論文里面,香農第一次用數學的方法來解釋了數據通信。

標題是通信的數學原理。

其中提到著名的香農定理。

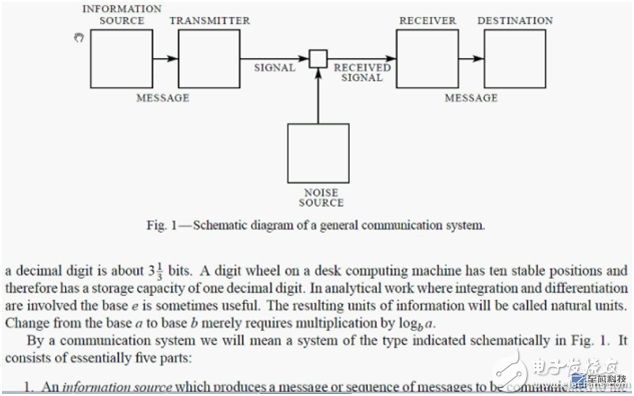

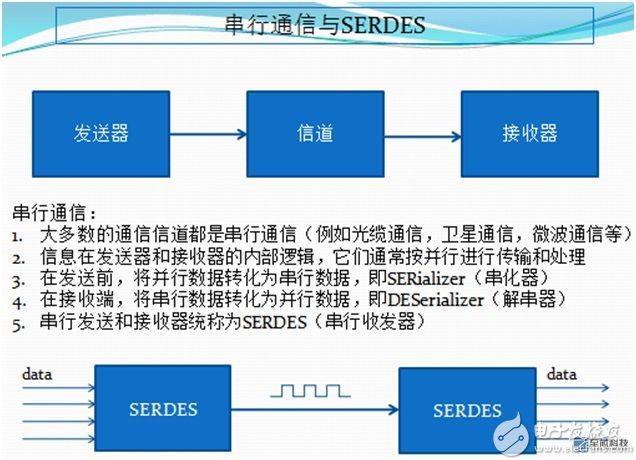

一般通信系統的架構圖。

它有一個信息源,然后變為消息,變成了電信號了,就是把原始的信息變成數字信號了。

然后通過一個發送器,變成了signal,物理的信號。

或者是高電平,或者是低電平。

中間小框是信道,channel。

信道必然會受到噪聲源的干擾,變成接收端的signal。

接收端的signal,和發送端的signal相比,就是有加噪。

接收器要將被噪聲干擾的信號,還原成原始的message,message就是已經變成數字量了。

回到最終的目標。

這個架構到今天還在用。

還有一些相關的文檔,都很經典。

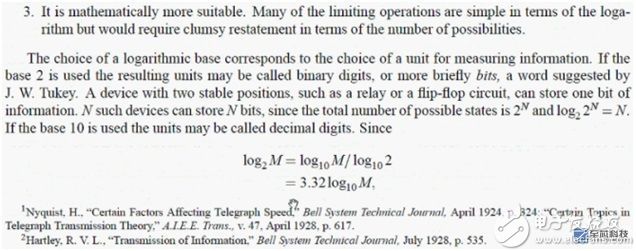

用數學模型來解釋信道的速度,信道的特征,信道的帶寬。

我們的通信課程分為兩個部分,第一是基本的原理。第二部分是擴頻。

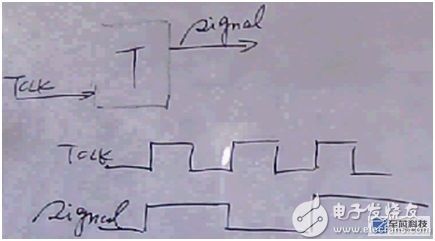

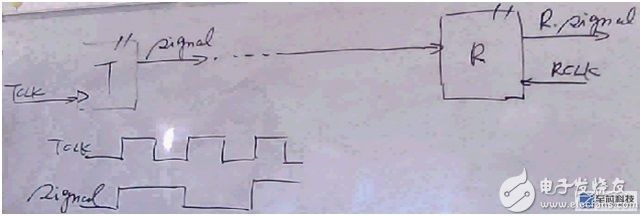

發送器的內部,和接收器的內部,它們不必要串行,它們可以并行。

在發送前,將并行數據轉化成串行數據,稱之為串化器。

對接收器而言,把串行數據組裝成并行數據的過程,稱之為并化器。

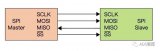

串化器和并化器是現代高速通信的核心,或者說IP、專利。

縮寫為SERDES,串行收發器。

現代的通信,可以做到好幾個G。

我們現在內核的邏輯,在cyclone IV下面可以到400、500、600M。

但是它高速通信的時候,可以到1個G以上,2、3個G。

這種程度怎么實現的呢?

內核邏輯能夠跑到500M、600M,就是通過這個SERDES,跑到1個G以上。

串行收發器,這是專用電路。

我們給大家解釋串行通信的基本規律。

第一,在串行通道上,必然有串化器、并化器。

第二,如果是一個并行的數據,沒有問題。

我們是通過物理的位置來組織。

哪個比特高,哪個比特低。

可是這是一個串行的。

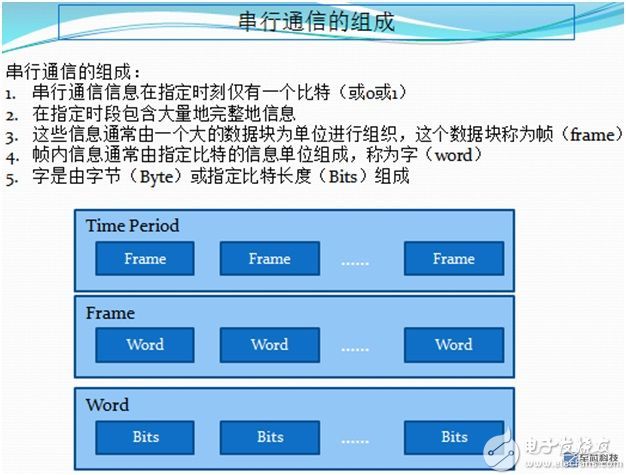

一個串行的過程在信道上,一定是一個比特連著一個比特。

并轉串和串轉并的時候,都有這個問題。

現在我們要把B0、B1、B2、B3,轉成串行。

依次是D0、D1、D-1,按順序發過來的。

串行通信就必然會有這個問題。

如果我們看一些手冊,大量的IP核,它的一些篇幅都是用于對齊的。

單位時間在指定時刻只有一個比特被加載。

看起來就像一個冰糖葫蘆串。

我們要知道比特的邊界。

還有一個更嚴峻的問題。

我們知道,串行通信有兩個特點。

第一個,串行通信要有串化器,要有解串器。

第二個,邊界的問題。

有找邊界,稱之為對齊的問題。

這個問題更嚴峻,或者說更現代化。

在發送端,串行信息是以串行的形式發出來的。

那么,必然會有時鐘驅動。發送端會有發送端的時鐘。

這是發送的時鐘。

我們學過同步電路,知道這個signal一定會踩著沿翻轉。

到接收端。

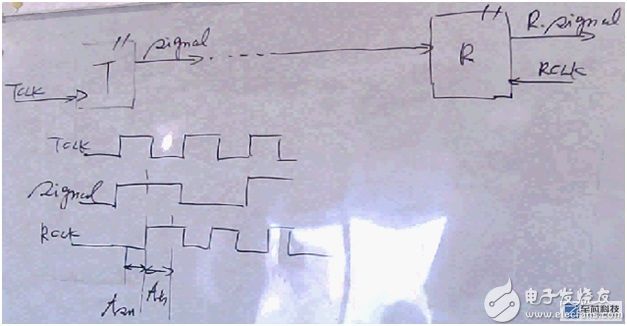

發送和接收都是同步電路。

Tclk和Rclk可能是相同時鐘,可能是相關時鐘。

但是對一個正常的通信系統而言,它做不到。

如果是衛星通信,一個在天上,一個在地上。

如果是遠洋通信,一個在亞洲,一個在歐洲。

怎么可能再做一條時鐘線呢?

一般來說,如果是無線通信,我們的手機,跟基站之間不會有時鐘的連線。

都是無線的。那么Tclk和Rclk存在各種各樣的關系。

無論是什么關系,對接收器而言,時鐘都要能有效地捕獲signal。

怎樣捕獲呢?

如果在上升沿之前和上升沿之后,所需要的穩定時間段得不到保證的話,就會發生亞穩態,就有可能導致這次傳輸的失敗。

一定要保證,在接收端的時候,在時鐘上升沿,建立時間之前,保持時間之后,這個signal沒有反轉。

時鐘的頻率要一致。

不一致,這個signal就沒法還原了。

所以說,兩個頻率要相同。

還要保證接收端的時鐘能夠正確地捕獲signal。

這就帶來一個問題,這兩個時鐘怎么做?

比方說,像我們RS232的通信。

那個通信,并沒有給出時鐘信號,通信的時候,在發送端和接收端之間并不需要發送時鐘的通道。

它只是用一個單端信號發送。

它只要約定時鐘即可,我約定時鐘9600,接收時鐘9600。

我們記不記得,使用16倍的波特率,在捕獲的時候,這個中心點偏差1/16,問題不大。

這是在低速情況之下。所以說在低速的情況之下,發送和接收時鐘,這兩者是用的約定的方式來進行時鐘的捕獲。

由于內容較多,接下來的分享會在評論區更新,謝謝。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603795

發布評論請先 登錄

相關推薦

無線擴頻系統由什么組成

安信可LoRa模組Ra-01,超長距離擴頻通信,抗干擾性強

高速串行通信協議詳解

美國FCC發布KDB 364244 D01標準,推動57-71 GHz頻段雷達設備認證

lora技術實現遠距離通信的原因有哪些?

FPGA與LoRa模塊的串口通信問題

串行通信中的異步、同步與并行通信機制解析

調制技術在通信領域有哪些具體應用?

串行通信與并行通信各種通信協議的區別

跟李凡老師學FPGA擴頻通信D01:串行通信基礎(課堂筆記)

跟李凡老師學FPGA擴頻通信D01:串行通信基礎(課堂筆記)

評論