何時使用鎖相環

鎖相在無線系統和需要在電路板上實現精確時鐘和信號同步的系統中,環路具有許多重要功能。使用PLL可能是比重復調整PCB中走線長度以補償承載并行或串行數據的通道中的偏差更好的選擇。通過與壓控振蕩器(VCO)同步,鎖相環也可用于消除參考信號的相位噪聲。

在低速/低頻時,給定驅動器中的相位噪聲為通常足夠低,您不需要利用鎖相環來補償它。除非電路板占用非常大的區域,否則上升時間已經比相位噪聲引起的延遲/抖動更長。此時,只有最長的走線組需要長度匹配,以便承載數據的走線中的信號上升時間與相位噪聲極限內的參考信號匹配。

因此,鎖相環對于高速信號的同步更有用。如果數據遍歷其源和目的地之間的許多組件(這不是許多設備和拓撲中的典型情況),則邏輯電路中的傳播延遲可能累積以產生顯著的延遲。此外,噪聲源 - 包括相位噪聲 - 正交增加,隨著數據穿越多個器件而增加抖動。當沒有穿過相同組件的時鐘信號時,這兩個因素都會導致數據和系統時鐘之間的顯著延遲。

除了將數字數據與系統時鐘同步之外,鎖相環還有許多用途。或其他參考信號。模擬或數字鎖相環也可用于比某些參考更高或更低頻率的頻率合成。就數字合成而言,鎖相環可用于降低或增加數字脈沖流的重復率。在這兩種情況下,振蕩/重復頻率都可以通過商用和實驗鎖相環達到10 GHz,從而可以支持5G系統和許多RF應用。

作為無線系統和其他需要頻率合成的設備的一部分,鎖相環在PCB設計中發揮著重要作用。那么什么時候應該在系統中使用鎖相環?與PCB設計中的許多答案一樣,這一切都取決于您的設備要求和應用。

VCO在鎖相環中的作用

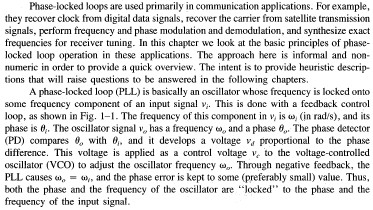

鎖相環使用模擬應用中VCO的負反饋,或數字應用中的數控振蕩器(NCO)。在模擬應用中,VCO或NCO的輸出頻率分別取決于其輸入電壓或數字輸入。在任何一種情況下,PLL的輸出都將與參考輸入信號之間的相位差成比例。當相位差(以及輸出)不隨時間變化時,則兩個信號被鎖定在相同的頻率。

在RF系統中,模擬VCO的輸出取決于輸入電壓,使其對調制參考時鐘信號很有用。在鎖相環內,VCO通過使用環路濾波器有效地鎖定到特定參考。在模擬鎖相環中,環路濾波器需要一些時間來鎖定所需的參考信號(達到~100 ns)。

環路濾波器的輸出在鎖相中也有一個特殊的位置環。當VCO用于鎖定期望的載波信號時,頻率或相位調制信號通常將以比鎖相環的鎖定時間快得多的速率進行調制。在這種情況下,環路濾波器將輸出一個誤差信號,該信號與參考信號和VCO信號之間的瞬時相位差成比例。當調制參考信號作為載波輸入到鎖相環時,該誤差信號實際上是解調信號。

玩過合成器嗎?您正在使用VCO

VCO布局作為鎖相環的一部分

可以使用鎖相環達到低幾十GHz的市場,但這些頻率仍然太低,無法容納5G系統或高頻RF系統所需的高階頻率。在這種情況下,您可能需要設計自己的VCO以用于鎖相環。

鎖相環已經在RF系統的發送部分中占有一席之地。來自VCO的輸出可用于將調制應用于載波信號,然后可將載波信號發送到發射天線。這可以通過T部分來完成,該部分使用三個電阻將天線阻抗與VCO的輸出阻抗相匹配。

VCO的帶寬將影響其對電源噪聲的敏感度及其自身相位噪聲。更寬的帶寬電壓VCO可能會增加對電源噪聲的敏感度,因此建議使用具有超低噪聲的功率調節器,以最大限度地降低VCO輸出上的相位噪聲。使用窄帶VCO只能適應更窄的頻率范圍,在設計時應考慮這一點。

電源噪聲問題需要精確去耦,并且去耦網絡應非常靠近用于設計VCO的任何IC的電源引腳。這將為這些IC提供穩定的直流電壓,并在電路板上其他位置的數字IC切換時抑制電源總線或電源層中的振鈴。任何去耦/旁路電容都應使用自己的過孔連接回地平面。

最好使用一種替代的高速層壓板,具有較低的損耗角正切板,包括鎖相環和VCO,用于WiFi頻率以上。應使用Rogers 4350或其他高速/高頻兼容材料代替FR4。在這些電路板上傳輸RF信號的跡線應盡可能短,以防止傳輸線行為和輻射。

考慮到具有鎖相環的RF器件的電源完整性,信號完整性和混合信號設計要求,設計人員需要正確的布局,布線和仿真工具,以確保其設計符合基本設計規則和行業標準。 Altium Designer將這些功能集成到一個程序中,允許您為任何應用程序設計最高質量的設備。

現在您可以下載Altium Designer的免費試用版并了解有關其設計套件的更多信息工具。您還可以在一個程序中訪問業界最佳的設計,模擬和驗證功能。立即與Altium專家交流以了解更多信息。

-

鎖相環

+關注

關注

35文章

584瀏覽量

87769 -

電路設計

+關注

關注

6675文章

2453瀏覽量

204366 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43045

發布評論請先 登錄

相關推薦

電路設計中,何時使用鎖相環?

電路設計中,何時使用鎖相環?

評論