我的第一塊PCB遠離高速數(shù)字設備。它只是單層PCB上的放大器電路,控制阻抗甚至不是事后的想法。一旦我開始研究需要高采樣率的電光系統(tǒng),控制阻抗始終是一個關鍵的設計問題。電路板上的受控阻抗是PCB布局問題,我在處理PCB一段時間后感覺不太舒服。

一旦開始處理高速或高頻信號,你就會'將發(fā)現(xiàn)跡線的阻抗和源和負載的不匹配會對信號完整性產(chǎn)生重大影響。在RF范圍內(nèi)及以后,控制信號遇到的阻抗將確保您的設備按設計運行。有一些簡單的設計策略可以幫助確保信號在運行期間不會失真。

阻抗控制與受控電介質(zhì)

阻抗控制和阻抗管理是兩個可松散互換的術語,指的是設置PCB中信號所見阻抗的不同方法。顯然,沒有任何制造工藝是完美的,任何從生產(chǎn)線上下來的PCB都會有一些跟蹤阻抗的變化。基本思想是將信號遇到的阻抗設置為特定值,理想情況下將任何阻抗不匹配限制為較小的值。

這可以通過兩種方式完成。首先,簡單地選擇用于形成跡線的幾何形狀,布置和材料將影響它們的阻抗。周圍的電介質(zhì)也會影響阻抗。這種情況對應于在具有無限厚度的電介質(zhì)上布線的單個跡線。大多數(shù)簡單的阻抗計算器都假設這種情況顯然,這種近似僅在少數(shù)特殊情況下有效。

您可能會想“等一下,為什么基板的介電常數(shù)會有所不同?”這有很多原因。首先,相鄰走線之間以及走線和接地平面之間的電介質(zhì)形成電容器,介電常數(shù)決定雜散電容。

由于走線與基板之間的界面不是完美的反射器,電場實際上進入電介質(zhì)并保持與跡線中的場耦合。簡而言之,信號部分地在電介質(zhì)中傳播,并且不完全限制在跡線中。

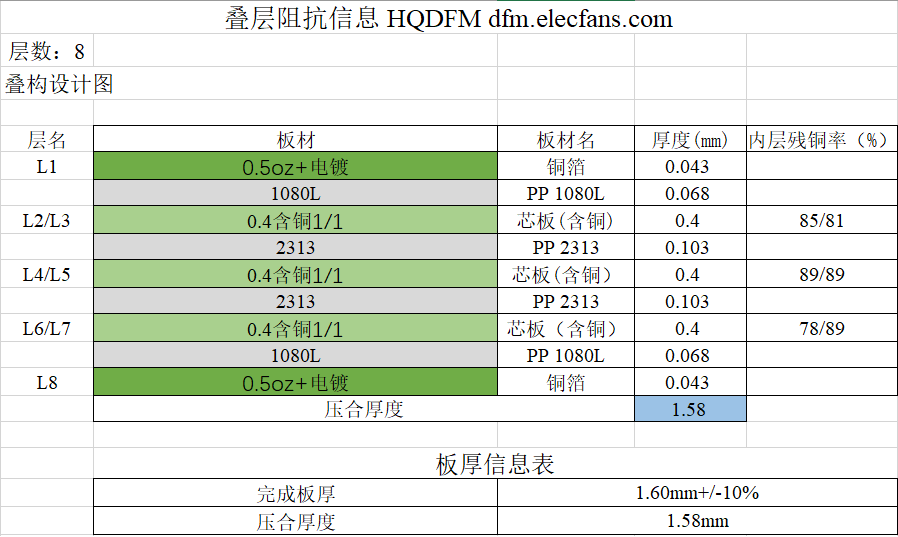

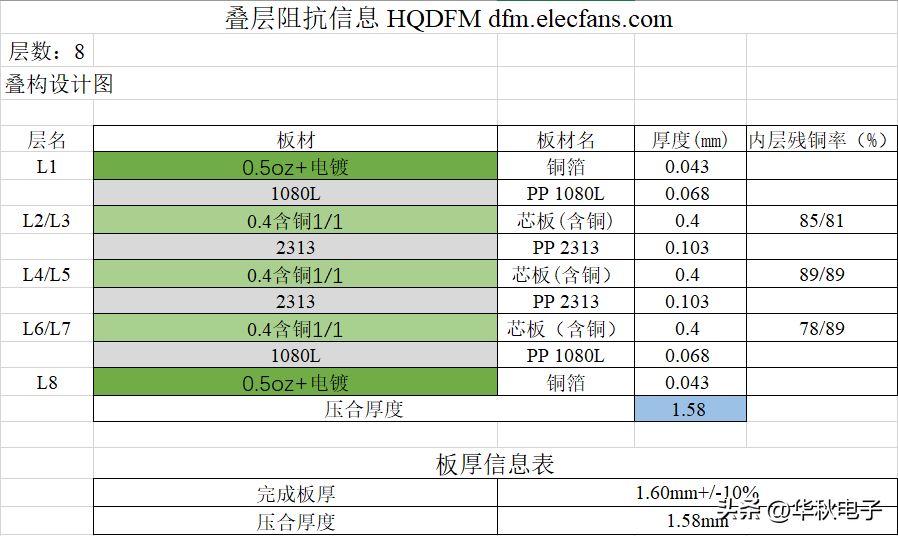

這兩個事實都意味著多層PCB中的層疊會影響跡線中信號所見的阻抗。實際上,修改層疊層允許調(diào)整整體走線阻抗。調(diào)整層疊會改變信號所見的有效介電常數(shù),允許在許多應用中進行阻抗控制。

<小> PCB組件之間有走線

阻抗控制設計

大多數(shù)設計人員可能熟悉阻抗控制,其中走線布置,尺寸,同時考慮地平面布置。攜帶高速信號的走線應在實心接地層上布線,以便為電流提供可靠的返回路徑,從而最大限度地減小環(huán)路面積,從而最大限度地減少因EMI引起的任何感應電流。

路由高速信號由于串聯(lián)電感增加,信號降級以及與其他信號的干擾,分裂平面會導致信號傳播延遲。如果必須將高速阻抗控制的走線穿過接地層中的間隙,則可以使用縫合電容來提供電流返回路徑。這也最小化了環(huán)路以及當跡線穿過地平面中的間隙時產(chǎn)生的任何阻抗不連續(xù)性。

一些制造商提供阻抗計算器,可幫助您選擇給定跡線/接地平面布置所需的適當走線尺寸和所需的阻抗值。或者,如果您的走線尺寸受到限制,您可以使用這些計算器之一確定PCB中源,走線和負載之間的阻抗不匹配水平。

在制造多層板時,您的制造商可以通過改變PCB走線中兩個橫截面尺寸中的一個來幫助您獲得所需的阻抗值。它們通常構(gòu)建測試板(稱為“試樣”)并修改跡線尺寸和布置,以便在一定的容差水平(通常為+/- 10%)內(nèi)達到所需的阻抗值。使用差分對時,跡線間距是另一個可用于調(diào)整阻抗的參數(shù)。

如果設計者指定必須修復跡線的高度,那么它們將改變寬度,并且反之亦然,以獲得恰當?shù)淖杩怪怠_@也使制造商有機會調(diào)整他們的過程并確保您在生產(chǎn)運行中獲得更高的產(chǎn)量。

主板上的高密度跡線

受控電介質(zhì)設計

與阻抗控制設計相比,層疊通常保持恒定,受控電介質(zhì)設計通過修改層疊層達到特定的跡線阻抗值。重新排列層堆疊布置,層厚度,甚至交換不同材料的電介質(zhì)都是設計人員可以采取的措施來管理多層PCB中的阻抗。

阻抗控制設計通常還使用受控介電板,但反過來不一定是真的。修改層疊布置,電介質(zhì)厚度,預浸料坯厚度和層壓板厚度都會改變電路板上信號所看到的阻抗。對于給定的跡線幾何圖形,修改這些電路板參數(shù)可以讓您微調(diào)電路板的阻抗。

確定電路板行為的最佳方法是使用3D電磁仿真軟件包。不幸的是,許多人沒有這個軟件,你將不得不求助于使用一些基本的阻抗計算器和你的直覺來了解修改電路板將如何影響阻抗。

特別是在工作時通過信號完整性問題或印刷電路板的布局問題,您選擇的軟件應該能夠跟上過孔,布局,電源平面或其他平面管理和PCB疊加。當您使用具有強大設計軟件的電路板時,使用跡線寬度管理PCB布局將成為過去。

如果您正在尋找一個PCB設計軟件平臺,可以讓您完全控制您的阻抗PCB,您需要嘗試AltiumDesigner?。 Altium Designer為您提供最新,最好的CAD工具,組件庫和仿真工具。

-

集成電路

+關注

關注

5389文章

11573瀏覽量

362260 -

pcb

+關注

關注

4322文章

23124瀏覽量

398514 -

封裝

+關注

關注

127文章

7941瀏覽量

143093 -

可制造性設計

+關注

關注

10文章

2065瀏覽量

15625 -

華秋DFM

+關注

關注

20文章

3494瀏覽量

4587

發(fā)布評論請先 登錄

相關推薦

淺談PCB疊層設計原則及阻抗設計

一文輕松搞定PCB疊層和阻抗設計

如何利用平面的PCB疊層設計實現(xiàn)阻抗管理

如何利用平面的PCB疊層設計實現(xiàn)阻抗管理

評論