阻抗控制線是否會增加PCB板的成本?是的,會增加PCB的制造成本設(shè)計(jì)。但是,有3個主要元素可以控制PCB制造成本:

1、配置

首先,考慮PCB尺寸。當(dāng)PCB尺寸過大時(shí),印刷線路較長,阻抗增大,抗噪聲能力降低,成本也增加;如果尺寸太小,則散熱不好,相鄰的線路容易受到干擾。確定PCB尺寸后,確定特殊組件的位置。最后,根據(jù)電路的功能單元,電路的所有組件都布置好了。

2、接線

接線原理如下:

(1)應(yīng)盡可能避免輸入和輸出端子使用的導(dǎo)線。最好在導(dǎo)線之間添加接地線以避免反饋。

(2)最小電路寬度主要取決于導(dǎo)線與絕緣基座之間的粘接強(qiáng)度和流經(jīng)它們的電流

(3)印刷導(dǎo)體的彎角通常呈圓弧形,直角或角度影響高頻電路的電氣性能。另外,盡量避免使用大面積的銅箔,否則很容易導(dǎo)致銅箔在長時(shí)間加熱時(shí)膨脹和脫落。當(dāng)使用大面積的銅箔時(shí),優(yōu)選使用網(wǎng)格形狀。這有利于消除由銅箔和基板之間的粘合劑的熱量產(chǎn)生的揮發(fā)性氣體。

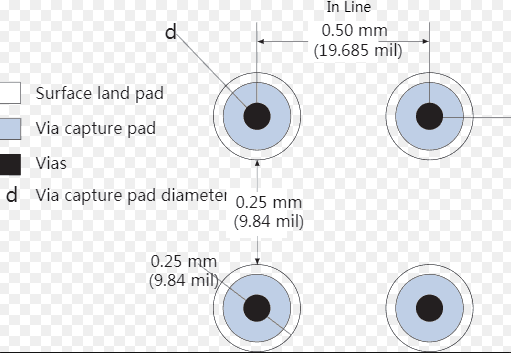

3、墊

墊中心孔(直插式設(shè)備)略大于器件引線直徑。焊盤太大而不能形成焊點(diǎn)。墊外徑D通常不小于(d + 1.2)mm,其中d是引導(dǎo)孔。對于高密度數(shù)字電路,最小焊盤直徑可以是(d + 1.0)mm。

-

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4691瀏覽量

85855 -

控制線

+關(guān)注

關(guān)注

0文章

16瀏覽量

4360 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43088

發(fā)布評論請先 登錄

相關(guān)推薦

PCB板的特性阻抗與特性阻抗控制

PCB設(shè)計(jì)走線的阻抗控制簡介

高頻高速PCB設(shè)計(jì)中的阻抗匹配,你了解多少?

阻抗板是否高可靠,華秋有話說

基于PCB設(shè)計(jì)的阻抗控制實(shí)現(xiàn)

什么是阻抗控制如何對PCB進(jìn)行阻抗控制

如何控制PCB走線的阻抗

如何利用EDA軟件對PCB進(jìn)行阻抗控制

PCB的結(jié)構(gòu)和加工流程線路阻抗控制線路阻抗計(jì)算的詳細(xì)資料簡介

分析詳解PCB板工藝的阻抗控制

阻抗控制線是否會增加PCB板的成本? PCB打印

阻抗控制線是否會增加PCB板的成本? PCB打印

評論