如果數(shù)字邏輯電路的頻率達到或超過45 MHz至50 MHz,并且在此頻率以上工作的電路已經(jīng)占整個電子系統(tǒng)的一定量(例如,1/3),它通常被稱為高頻電路。高頻PCB設(shè)計是一個非常復(fù)雜的設(shè)計過程,其布線對整體設(shè)計至關(guān)重要!

開始步驟的多層板布線

高頻電路往往具有高集成度和高布線密度。多層電路板的使用既是布線所必需的,也是減少干擾的有效手段。在PCB布局階段,合理選擇一定數(shù)量的印刷電路板尺寸可以充分利用中間層來設(shè)置屏蔽,更好地實現(xiàn)近接地,有效降低寄生電感,縮短傳輸長度通過減少信號的串?dāng)_等,所有這些方法都有利于高頻電路的可靠性。根據(jù)數(shù)據(jù),四層板比雙板的噪音低20dB。但是,也存在問題。 PCB半層數(shù)越高,制造工藝越復(fù)雜,單位成本越高。這要求我們?yōu)镻CB布局選擇適當(dāng)數(shù)量的PCB板。正確的組件布局規(guī)劃和正確的布線規(guī)則,以完成設(shè)計。

第二:高速電子設(shè)備引腳彎曲越小越好。

高頻電路布線的引線優(yōu)選為全線,需要轉(zhuǎn)動,并且可以以45度線或圓弧折疊。該要求僅用于提高低頻電路中銅箔的固定強度,并且在高頻電路中,滿足內(nèi)容。一個要求是減少高頻信號的外部傳輸和互耦。

第三:高頻電路設(shè)備引腳之間的引線越短越好。

信號的輻射強度與信號線的跡線長度成比例。高頻信號引線越長,耦合到靠近它的元件越容易,因此對于信號時鐘,晶體,DDR,高頻信號線(如LVDS線,USB線和HDMI線)等數(shù)據(jù)要求盡可能短。

第四:高頻電路器件引腳之間引線層之間的過渡越少越好。

所謂“引線層之間的最小交替更好”意味著組件連接過程中使用的通孔(Via)越少越好。根據(jù)這一方面,通孔可以帶來約0.5pF的分布電容,減少通孔數(shù)可以顯著提高速度并降低數(shù)據(jù)錯誤的可能性。

第五:注意并行線路引入的“串?dāng)_”信號線。

高頻電路布線應(yīng)注意信號線平行線引入的“串?dāng)_”。串?dāng)_是指未直接連接的信號線之間的耦合現(xiàn)象。由于高頻信號以電磁波的形式沿著傳輸線傳輸,信號線充當(dāng)天線,并且電磁場的能量在傳輸線周圍發(fā)射,并且由相互產(chǎn)生的不期望的噪聲信號信號之間的電磁場耦合稱為串?dāng)_。 PCB層的參數(shù),信號線的間距,驅(qū)動器和接收器的電特性以及信號線的終端都對串?dāng)_產(chǎn)生一定的影響。因此,為了減少高頻信號的串?dāng)_,需要在布線過程中盡可能做到以下幾點:

在兩個接地之間插入接地或接地層具有嚴(yán)重串?dāng)_的線路可以在布線空間允許的條件下進行隔離并減少串?dāng)_。

當(dāng)信號線周圍的空間存在時變電磁場時,如果無法避免并聯(lián)分布,可以在并聯(lián)信號線的反面放置一個大面積的“接地”,以大大減少干擾。

在接線的前提下空間允許,增加相鄰信號線之間的間距,減小信號線的平行長度,時鐘線應(yīng)垂直于關(guān)鍵信號線而不是平行。

如果同一層中的平行跡線幾乎是不可避免的,則在相鄰的兩層中,跡線的方向必須彼此垂直。

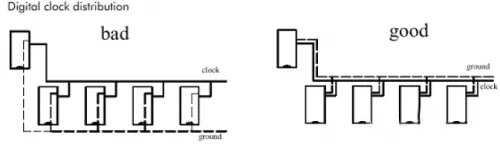

在數(shù)字電路中,通常的時鐘信號是邊沿變化快的信號,外部串?dāng)_很大。因此,在設(shè)計中,時鐘線應(yīng)該被地線和更多的接地孔包圍,以減少分布電容,從而減少串?dāng)_。

用于高頻信號時鐘,嘗試使用低壓差分時鐘信號并覆蓋地面。您需要注意包裝的完整性。

請勿將未使用的輸入端子接地,而是將其接地或連接到電源(電源也在高頻信號回路中接地)。因為懸掛線可以等同于發(fā)射天線,所以接地可以抑制發(fā)射。實踐證明,使用這種方法消除串?dāng)_有時可以立即生效。

第六:集成電路模塊的電源引腳增加高頻解鎖電容

高頻解捻電容添加到每個集成電路塊的電源引腳。增加電源引腳的高頻去耦電容可以有效抑制電源引腳上的高頻諧波,形成干擾。

當(dāng)模擬地線,數(shù)字地線等連接到公共地線時,應(yīng)使用高頻湍流磁珠連接或直接隔離選擇適合單點互連的地方。高頻數(shù)字信號的地的地電位通常是不一致的,并且兩者之間通常存在一定的電壓差。而且,高頻數(shù)字信號的地線通常具有非常豐富的高頻信號的諧波分量。當(dāng)數(shù)字信號地和模擬信號地直接連接時,高頻信號的諧波通過地線耦合干擾模擬信號。因此,通常,要隔離高頻數(shù)字信號的接地和模擬信號的接地,并且在適當(dāng)位置的單點互連方法或高頻湍流磁珠的互連可以是通過。

第八:避免由痕跡形成的循環(huán)

不要形成循環(huán)所有類型的高頻信號走線都盡可能多。如果不可避免,請使循環(huán)區(qū)域盡可能小。

第九:必須確保良好的信號阻抗匹配

在信號傳輸期間,當(dāng)阻抗不匹配時,信號將反射在傳輸通道中,反射將超過復(fù)合信號,導(dǎo)致信號在邏輯閾值附近波動。

消除反射的基本方法是使發(fā)射信號的阻抗匹配良好。由于負(fù)載阻抗和傳輸線的特征阻抗之間的差異較大,因此反射也較大。因此,信號傳輸線的特征阻抗應(yīng)盡可能地等于負(fù)載阻抗。同時,應(yīng)注意PCB上的傳輸線不應(yīng)突然或轉(zhuǎn)角,盡量保持傳輸線各點的阻抗連續(xù),否則傳輸線段之間會有反射。這需要在執(zhí)行高速PCB布線時遵循以下布線規(guī)則:

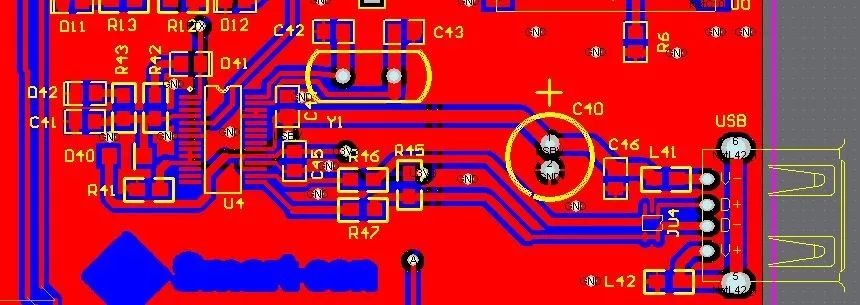

USB布線規(guī)則。需要USB信號差分路由。線寬為10密耳,線間距為6密耳,地線和信號線相距6密耳。

HDMI接線規(guī)則。需要HDMI信號差分布線,線寬為10密耳,線間距為6密耳。每對HDMI差分信號對之間的間距超過20密耳。

LVDS接線規(guī)則。需要LVDS信號差分走線,線寬7mil,線間距6mil,目的是將HDMI的差分信號阻抗控制在100 + -15%歐姆

DDR接線規(guī)則。 DDR1布線要求信號不應(yīng)盡可能地穿過孔。信號線的寬度相等,線與線等距。該線路必須符合2W原則,以減少信號之間的串?dāng)_。對于DDR2及以上版本的高速設(shè)備,需要高頻數(shù)據(jù)。這些線的長度相等,以確保信號的阻抗匹配。

第十:保持信號傳輸?shù)耐暾?/strong>

保持信號傳輸?shù)耐暾苑乐褂傻孛娣指钜鸬摹暗孛娣磸棥薄?/p>

-

高頻PCB

+關(guān)注

關(guān)注

1文章

17瀏覽量

13299 -

PCB布局

+關(guān)注

關(guān)注

9文章

183瀏覽量

27849 -

華強pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43075

發(fā)布評論請先 登錄

相關(guān)推薦

PCB布局的建議

PCB布局布線技巧100條

MT2492的PCB布局設(shè)計建議

PW2162的PCB布局設(shè)計的建議是什么

PCB布線與設(shè)計制造的10條黃金法則

PCB設(shè)計中元器件布局的10條規(guī)則,布線的規(guī)則是什么?

元器件布局的10條規(guī)則

PCB布局布線的規(guī)則

GaN FET 半橋的電路設(shè)計和PCB布局建議-AN90006

高頻PCB布局的10條建議

高頻PCB布局的10條建議

評論