在學習嵌入式系統的過程中,定時器有關內容的學習是必不可少的一個環節。定時器定時功能的實現,最主要的還是靠其內部的計數器。那么,計數器是如何實現計數功能的呢?接下來就來簡單介紹一下計數器的實現電路。

2023-09-25 14:18:48 238

238

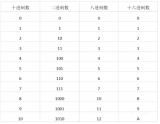

什么是進位計數制

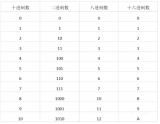

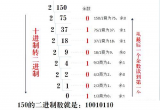

數制也稱計數制,是指用一組固定的符號和統一的規則來表示數值的方法。按進位的原

則進行計數的方法,稱為進位計數制。比如,在十進位計數制中,是按照“逢十進一”的原則進行計數的。

2023-08-20 09:32:57 171

171

數制也稱計數制,是指用一組固定的符號和統一的規則來表示數值的方法。按進位的原則進行計數的方法,稱為進位計數制。

2023-08-12 09:17:12 705

705 數制也稱計數制,是指用一組固定的符號和統一的規則來表示數值的方法。按進位的原則進行計數的方法,稱為進位計數制。比如,在十進位計數制中,是按照“逢十進一”的原則進行計數的。

2023-07-04 11:06:26 273

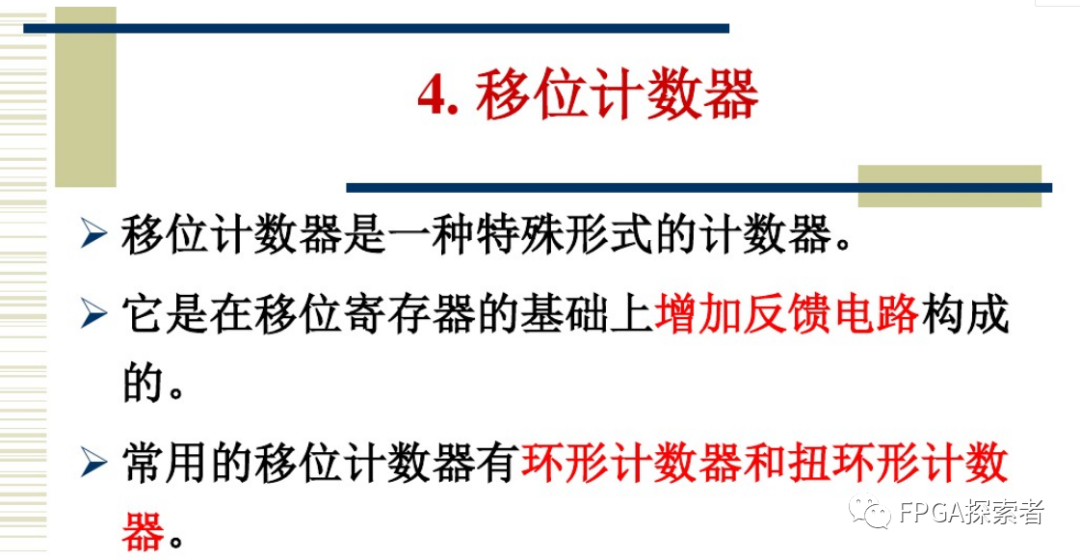

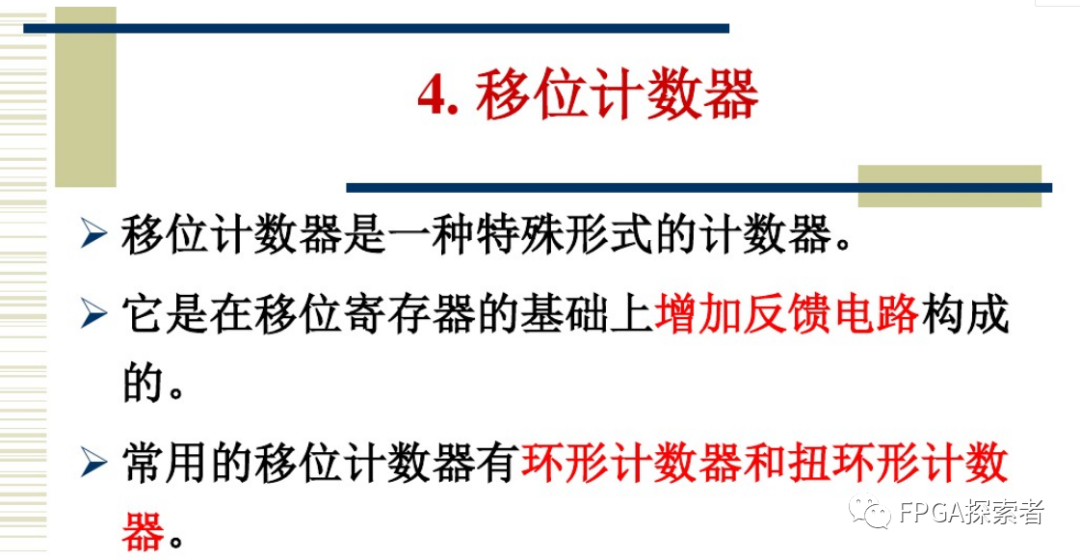

273 扭環形計數器,每次狀態變化時僅有一個觸發器發生翻轉,譯碼不存在競爭冒險,在n(n≥3)位計數器中,使用2n個狀態,有2^n-2n個狀態未使用;

2023-06-27 10:18:23 297

297

數制也稱計數制,是指用一組固定的符號和統一的規則來表示數值的方法。它按進位的原則進行計數的方法,稱為進位計數制。

2023-04-27 11:32:59 1340

1340

進制也就是進位計數制,是人為定義的帶進位的計數方法。對于任何一種進制---N進制,就表示每一位置上的數運算時都是逢N進一位。

2023-02-27 15:08:01 332

332 14 級紋波進位二進制計數器/除法器和振蕩器-HEF4060B

2023-02-15 18:54:07 0

0 14 級紋波進位二進制計數器/除法器和振蕩器-HEF4060B_Q100

2023-02-15 18:53:56 0

0 FX2N系列PLC的32位加減雙向計數器(設定值-2147483648~2147483647)

? 通用加/減雙向計數器:C200~C219(20點);

? 停電保持加/減雙向計數器:C220~C234(15點);

2023-01-29 15:20:22 1124

1124 PLC閃爍電路計數停止

2022-11-03 11:14:51 874

874 行波進位加法器和超前進位加法器都是加法器,都是在邏輯電路中用作兩個數相加的電路。我們再來回顧一下行波進位加法器。

2022-08-05 16:45:00 639

639

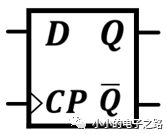

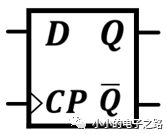

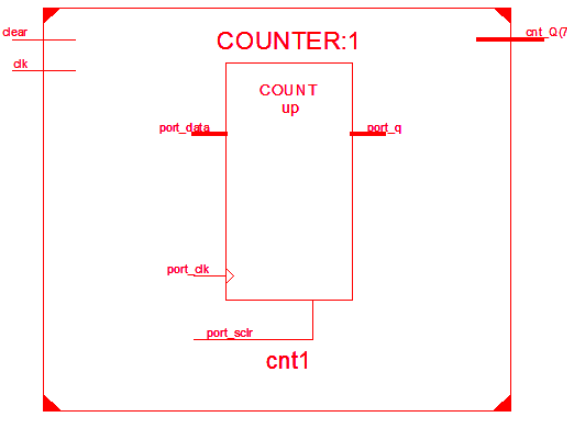

1、了解時序電路的經典設計方法(D觸發器、JK觸發器和一般邏輯門組成的時序邏輯電路)。

2、了解同步計數器,異步計數器的使用方法。

3、了解同步計數器通過清零阻塞法和預顯數法得到循環任意進制

2022-07-10 14:37:37 15

15 扭環形計數器,約翰遜計數器,每次狀態變化時僅有一個觸發器發生翻轉,譯碼不存在競爭冒險,在n(n≥3)位計數器中,使用2n個狀態,有2^n-2n個狀態未使用;

2022-06-15 09:27:57 1630

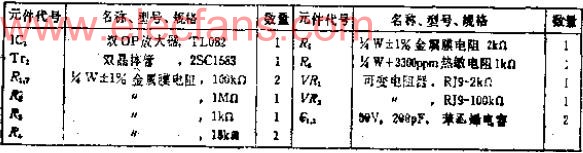

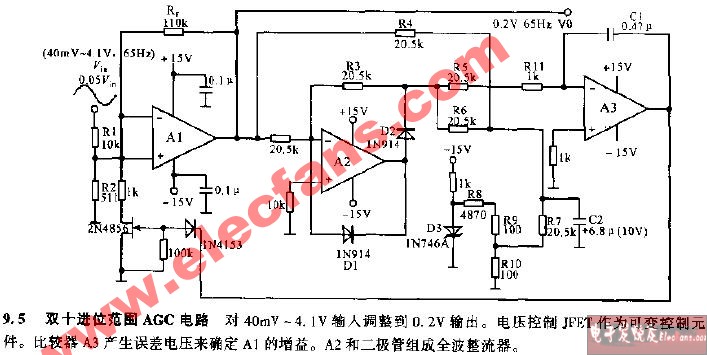

1630 雙十進位范圍AGC電路

2009-09-11 00:50:07

數字電子鐘“時”計數電路的設計與仿真

2021-12-30 13:55:15 51

51 計數器(Counter)由基本的計數單元和控制門所組成,是在數字系統中對脈沖的個數進行計數,以實現測量、計數和控制功能,且兼有分頻功能的儀器。計數器按進位制不同,分為二進制計數器和十進制計數器;按

2021-11-25 18:06:07 32

32 ADSP-2116N EZ-KIT有限公司設計數據表(修訂3.0)

2021-06-17 15:33:57 11

11 ADSP-2116N EZ-KIT有限公司設計數據表(修訂3.0)

2021-04-13 12:21:32 1

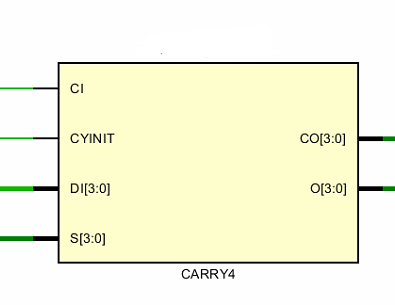

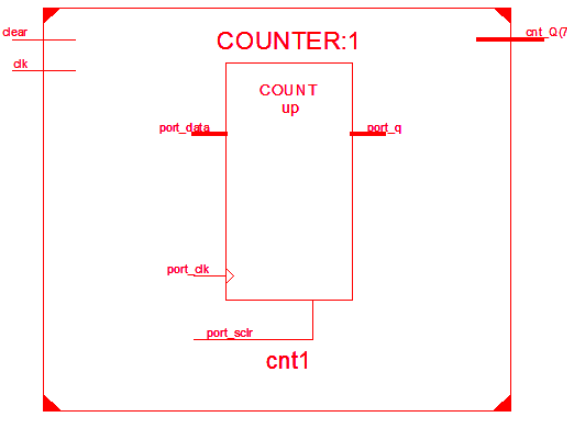

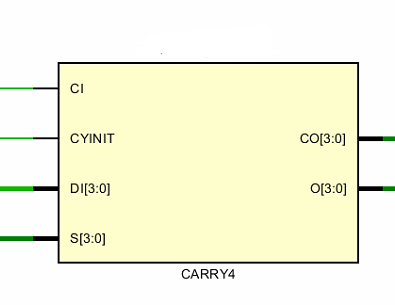

1 該計數器從0 計數到4294967295,然后回滾到0 并重新開始計數。它只需要FPGA 上一點點的資源就可以迅速完成計數,這都多虧了FPGA 中隱藏的進位鏈。讓我們來看這種計數器的幾種變體。

2020-12-11 17:26:55 12

12 在FPGA中我們寫的最大的邏輯是什么?相信對大部分朋友來說應該是計數器,從最初板卡的測試時我們會閃爍LED,到復雜的AXI總線中產生地址或者last等信號,都會用到計數器,使用計數器那必然會用到進位

2020-11-16 16:35:26 5466

5466

假設時鐘分頻是N,則設置一個計數器,計數長度是N(即從0計數到N-1),然后在計數器為計數到(N-1)/2的時候,翻轉一下分頻時鐘信號。

2020-11-06 13:59:47 9216

9216

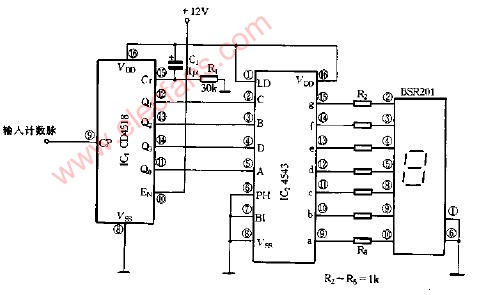

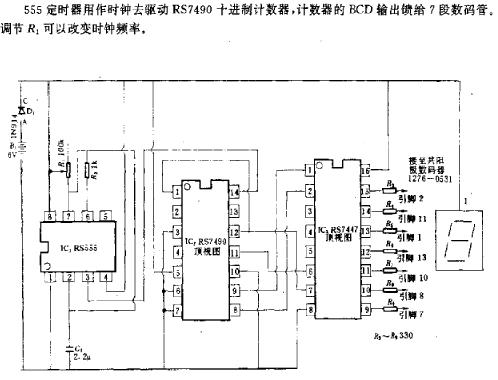

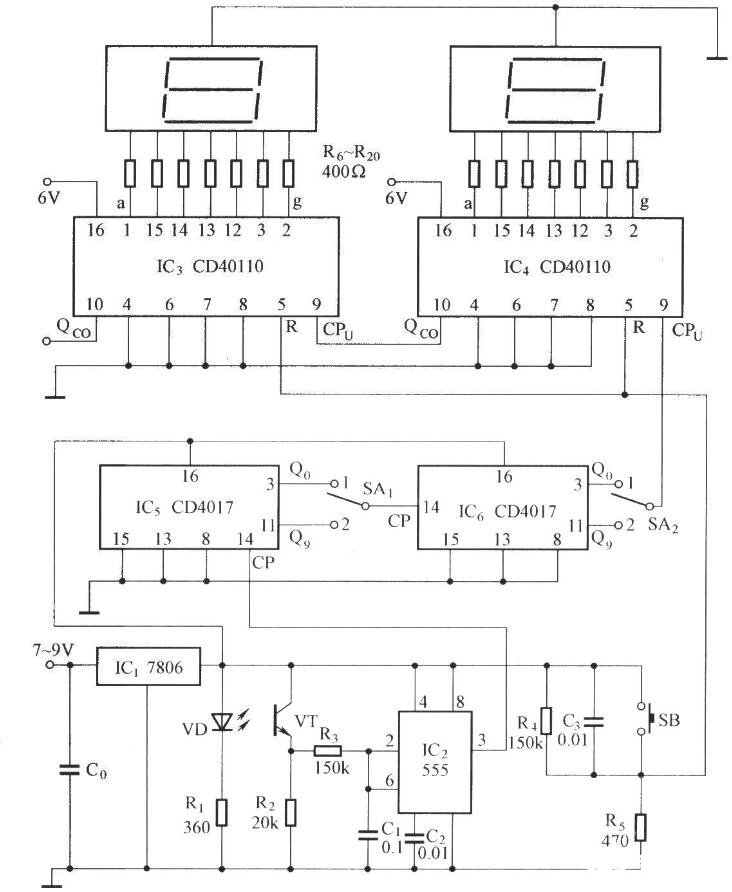

如下圖所示,圖a中采用十進制七段存儲-譯碼-驅動單元74143,此單元對所有段都有恒流輸出。在電壓為5V時每段電流約為15~22mA.七段譯碼器的BCD數據可以由腳17~20上取出。腳22用于進位,即當計數值到9后就為低電平,其余為高電平。利用這個信號可以控制上一位計數器。

2020-01-29 16:40:00 3316

3316

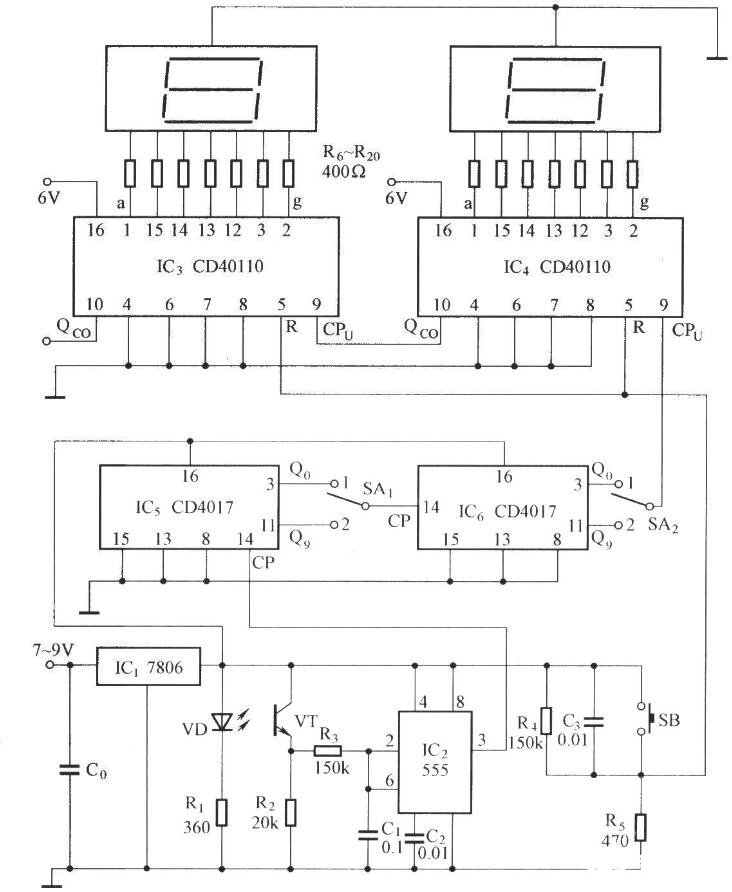

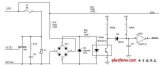

該電路由光電輸入電路(VD,VT),計數脈沖形成電路(555),倍率調節電路(IC5,IC6)和計數與顯示電路組成(CD40110)。

2020-01-14 16:01:44 2567

2567

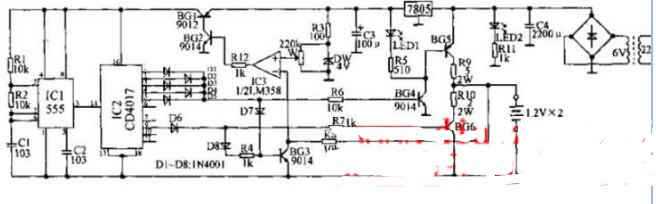

為了提高該電路的變換效率,PWM控制采用貴生動力專用研發的集成控制器件;脈沖產生電路采用了555時基電路與十進位計數器/分頻電路。

2020-01-02 15:39:54 5562

5562

數制也稱計數制,是指用一組固定的符號和統一的規則來表示數值的方法。按進位的原則進行計數的方法,稱為進位計數制。比如,在十進位計數制中,是按照“逢十進一”的原則進行計數的。

2019-05-06 16:48:36 2923

2923 數制也稱計數制,是指用一組固定的符號和統一的規則來表示數值的方法。按進位的原則進行計數的方法,稱為進位計數制。比如,在十進位計數制中,是按照“逢十進一”的原則進行計數的。

2019-02-14 09:13:52 2939

2939 數制也稱計數制,是指用一組固定的符號和統一的規則來表示數值的方法。按進位的原則進行計數的方法,稱為進位計數制。比如,在十進位計數制中,是按照“逢十進一”的原則進行計數的。

2019-01-18 17:08:52 2859

2859

數制也稱計數制,是指用一組固定的符號和統一的規則來表示數值的方法。按進位的原則進行計數的方法,稱為進位計數制。比如,在十進位計數制中,是按照“逢十進一”的原則進行計數的。

2018-10-31 11:24:42 2654

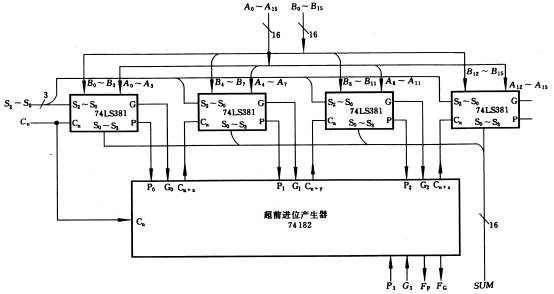

2654 最近在做基于MIPS指令集的單周期CPU設計,其中的ALU模塊需要用到加法器,但我們知道普通的加法器是串行執行的,也就是高位的運算要依賴低位的進位,所以當輸入數據的位數較多時,會造成很大的延遲

2018-07-09 10:42:00 18610

18610

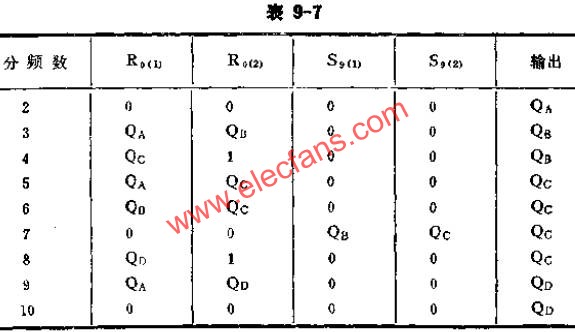

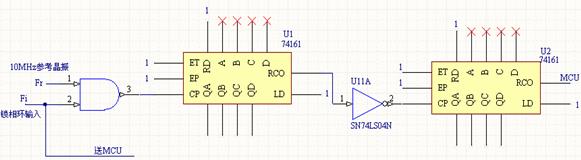

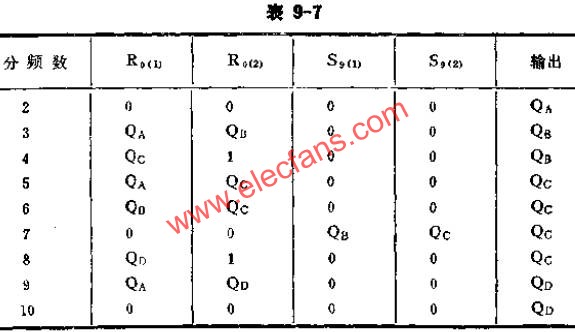

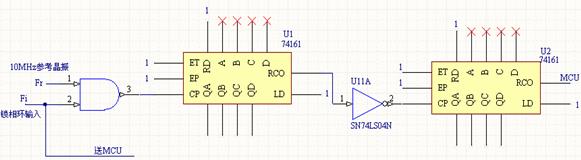

本文主要介紹了74ls161分頻電路圖大全(脈沖分頻電路\同步加法計數器)。計數器又稱為分頻器。N進制計數器的進位輸出脈沖就是計數器輸入脈沖的N分頻。N進制計數器可直接作為N分頻器。用同步加法計數

2018-05-08 14:41:38 95799

95799

功能,并且具有進位信號輸出,可串接計數使用。重點分析了構成N進制計數器、以74LS163為基礎設計一個6分頻電路等。

2018-05-08 14:27:23 51924

51924

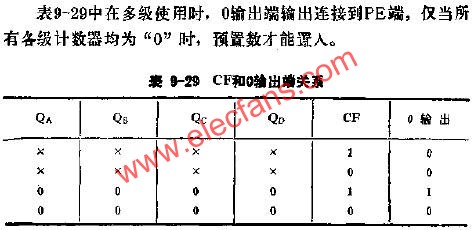

、秒計數電路。采用兩片74LS160按下圖所示連接,可以構成作60分頻計數,用于數字鐘中的秒計數器。標準秒脈沖經過控制門進入秒計數器,并顯示其計數值,當計數滿60時得到一個進位“分”脈沖,同時秒計數

2018-05-08 09:11:33 61651

61651

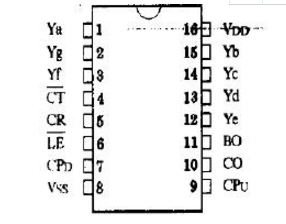

本文主要介紹了cd40110的工作原理詳細(cd40110引腳圖功能_如何計數及應用電路分享)。CD40110為十進制可逆計數器/鎖存器/譯碼器/驅動器,具有加減計數,計數器狀態鎖存,七段顯示譯碼

2018-03-04 11:34:35 96386

96386

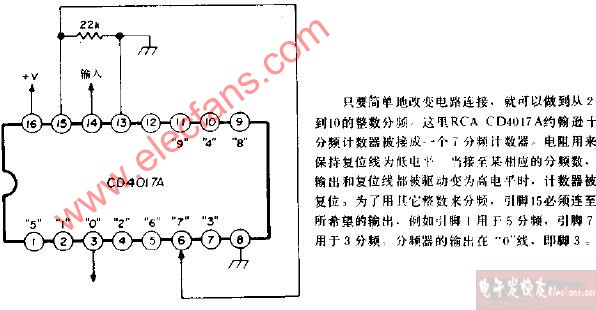

本文開始對CD4017功能與CD4017邏輯結構圖進行了介紹,其次分別介紹了用CD4017和選擇開關組成多進制計數器、CD4017組成的1/n計數器電路與用CD4017組成1~17進制計數器電路圖。

2018-01-31 13:58:06 22819

22819

器的CLK端,電路在計數脈沖的作用下按二進制自然序依次遞增1,當個位計數到9時,輸出進位信號給十位充當使能信號進位。當計數到24,這顯示器個位輸出0010(也就是4),顯示器十位輸出0010也就是2),將十位的QC、個位的QB端接一個二輸入與非門,與非門輸出一路送入十位計數器的清零端。

2018-01-18 15:43:05 145644

145644

本文主要介紹了74LS161集成計數器電路(2、3、4、6、8、10、60進制計數器)。74LS161是4位二進制同步計數器,該計數器能同步并行預置數據,具有清零置數,計數和保持功能,具有進位輸出端

2018-01-18 10:56:39 324594

324594

數制也稱計數制,是指用一組固定的符號和統一的規則來表示數值的方法。按進位的原則進行計數的方法,稱為進位計數制。比如,在十進位計數制中,是按照“逢十進一”的原則進行計數的。

2017-12-25 11:39:12 5011

5011 計的電路進行仿真實驗。仿真結果表明設計的計數器能實現所要求的N進制技術功能。最終得出采用反饋復零法可以實現進制計數器的結論。

2017-12-21 17:08:37 60783

60783

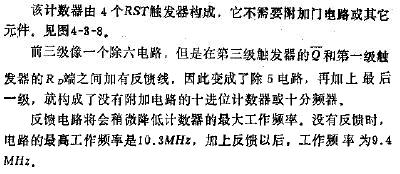

74LS160 芯片同步十進制計數器(直接清零) ·用于快速計數的內部超前進位 ·用于n 位級聯的進位輸出 ·同步可編程序 ·有置數控制線 ·二極管箝位輸入 ·直接清零 ·同步計數 本電路是由4 個

2017-12-21 16:29:13 584471

584471

數制也稱計數制,是指用一組固定的符號和統一的規則來表示數值的方法。按進位的原則進行計數的方法,稱為進位計數制。比如,在十進位計數制中,是按照“逢十進一”的原則進行計數的。

2017-11-30 15:08:36 32541

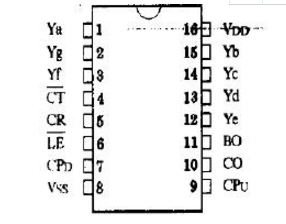

32541 CD4059A_CMOS可編程1N計數器

2016-06-24 15:33:24 1

1 集成計數器實現N進制計數集成計數器實現N進制計數集成計數器實現N進制計數

2016-06-08 14:28:43 15

15 計數器是用來累計和寄存輸入脈沖個數得時序邏輯部件,是數字系統中用途最廣泛的基本部件。計數器不僅能用于時鐘脈沖的計數,還可以用于分頻,定時,產生節拍脈沖及進位數字運算等,是數字系統、計算機系統必不可缺少的部件。

2016-05-05 17:40:59 4

4 為了縮短加法電路運行時間,提高FPGA運行效率,利用選擇進位算法和差額分組算法用硬件電路實現32位加法器,差額分組中的加法單元是利用一種改進的超前進位算法實現,選擇進位算

2013-09-18 14:32:05 33

33 下圖為:電壓頻率計數電路原理圖 圖 電壓頻率計數電路原理圖

2012-05-28 09:46:07 2692

2692

計數器是一種重要的時序邏輯電路,廣泛應用于各類數字系統中。介紹以集成計數器74LS161和74LS160為基礎,用歸零法設計N進制計數器的原理與步驟。用此方法設計了3種36進制計數器,并

2012-03-20 10:21:38 95

95 計數器是數字邏輯系統中的基本部件,它是數字系統中用得最多的時序邏輯電路,本文主要闡述了用中規模集成計數器設計任意進制同步加法計數器的設計思想,并對設計方法和步驟作

2012-02-28 11:41:43 6157

6157

異步計數器電路是指其構成的基本功能單元觸發器的時鐘輸入信號不是與觸發器在一起的,有的是外輸入的脈沖信號,有的是其他觸發器的輸出。本文給出了N進制 異步計數器 設計方案

2011-10-24 15:39:38 3245

3245

C182可預置數1/N計數器基本上是一個減法計數器,均由四個"T"型觸發器和附加控制門組成,具有級連N個計數器

2010-10-19 15:23:07 963

963

T210除了作為2-5-10進制計數器外,還可以接成9以內的N進制計數器,方法是在R0端上串接二個與非門電路,各級觸發器

2010-10-19 12:55:17 1344

1344

提出了一種適合FPGA高效運算的專用進位鏈結構。基于應用范圍方面的考慮,我們先對典型的行波進位做了一定的改進,目的是增強邏輯模塊的功能實現能力和提高運算速度。提出進

2010-07-28 17:47:54 19

19 摘要:應用CMOS電路開關級設計技術對超前進位全加器進行了設計,并用PSPICE模擬進行了功能驗證.與傳統門級設計電路相比,本文設計的超前進位電路使用了較少的MOS管,并能保持

2010-05-28 08:18:20 25

25 數字電子技術基礎(羅勇)

數制與數制轉換“數制”是指進位計數制, 即用進位的方法來計數.數制包括計數符號(數碼)和進位規則兩個方面.

2010-05-24 16:12:14 263

263 可獲得IP/十進位輸出的對數轉換電路

電路的功能

為了把大范圍的信

2010-05-08 17:26:36 666

666

Multisim 2001電路仿真軟件在計數器中的分析方法:摘 要:Multisim 2001軟件是專門用于電子電路仿真與設計的EDA 工具軟件,通過具體的實例分析Multisim 2001軟件仿真設計實現N進制計數器產

2010-04-25 10:17:15 63

63 計數/譯碼顯示電路: 計數譯碼顯示在現代科學技術中應用非常廣泛,它由計數器、譯碼器和顯示器三部分組成,包含數字電子系統的組合邏輯電路和

2009-12-20 12:36:59 128

128 數制與進位記數法

在采用進位記數的數字系統中, 如果只用r個基本符號 (例如0,1,2,…r-1) 、通過排列起來的符號串表示數值,則稱

2009-10-13 16:21:46 1527

1527 百進制計數器電路

將兩塊74LS290進行級聯,組成的百進制計數器如圖12.8所示。

2009-09-16 15:47:50 5541

5541

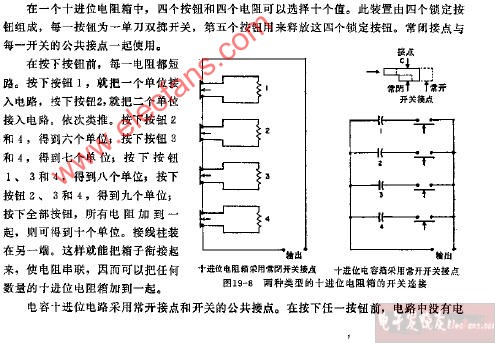

按鈕十進位箱電路圖

2009-07-03 13:33:00 393

393

圖3是可逆、可預置計數器CD4029構成的任意N分頻減法計數電路,U/D接“L”電平進行減法計數,B/D接“L”電平按BCD輸出碼進行計數,低位的Co進位到高位的CT輸

2009-06-22 07:44:38 4593

4593

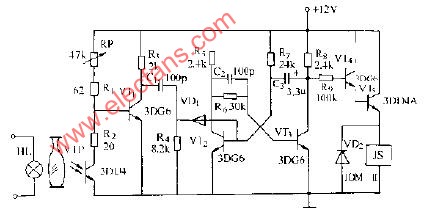

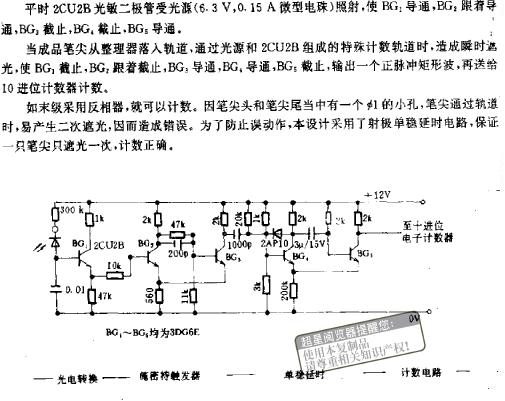

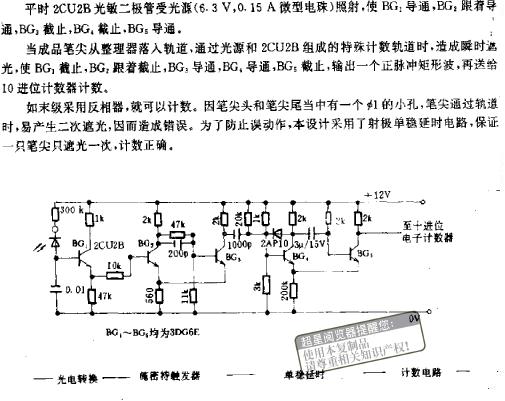

玻璃瓶計數電路圖

2009-06-03 15:46:22 627

627

脈沖計數顯示電路圖

2009-05-08 14:36:00 2439

2439

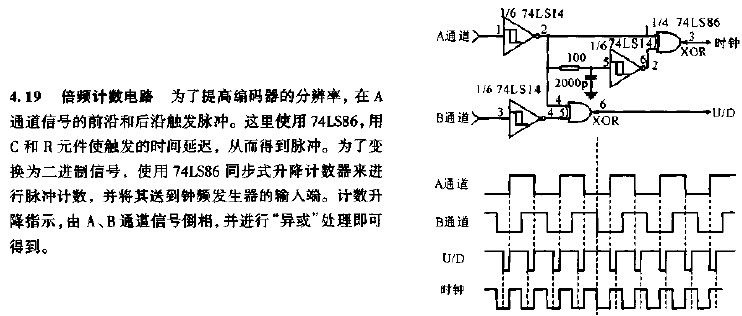

倍頻計數電路

2009-04-24 21:39:51 900

900

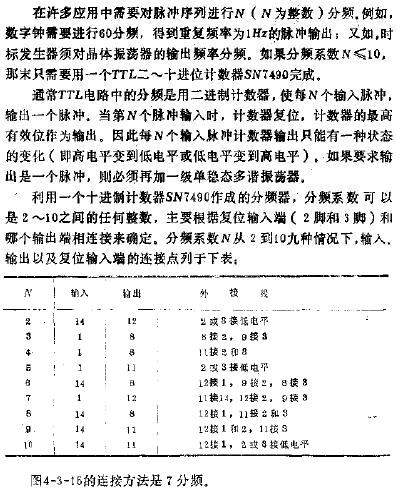

TTL十進位計數器構成的分頻器

2009-04-11 10:14:57 1067

1067

十進位計數器

2009-04-10 10:25:20 661

661

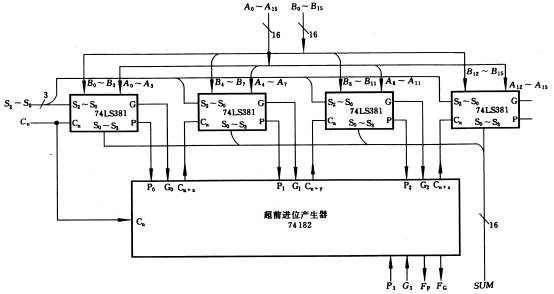

超前進位產生器74182

多位數的超前進位加法器的進位是并行產生的,大大提高了一算速度。但是隨著位數的增加,超前進位邏輯電路越來越復雜。為了解決這一矛盾,設計

2009-04-07 10:37:14 14122

14122

超前進位集成4位加法器74LS283

由于串行進位加法器的速度受到進位信號的限制,人們又設計了一種多位數超前進位

2009-04-07 10:36:35 26072

26072

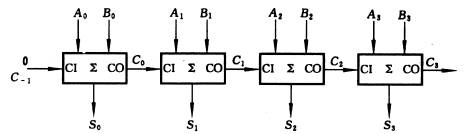

串行進位加法器

若有多位數相加,則可采用并行相加串行進位的方式來完成。例如,有兩個4位二進制數A3A2A1A0和B3B2B

2009-04-07 10:35:30 15784

15784

雙十進位范圍AGC電路圖

2009-04-01 21:39:31 557

557

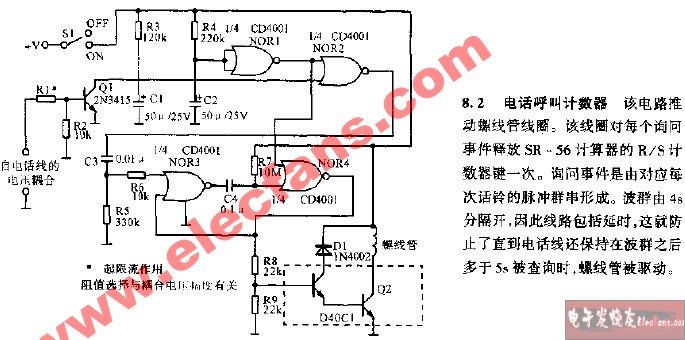

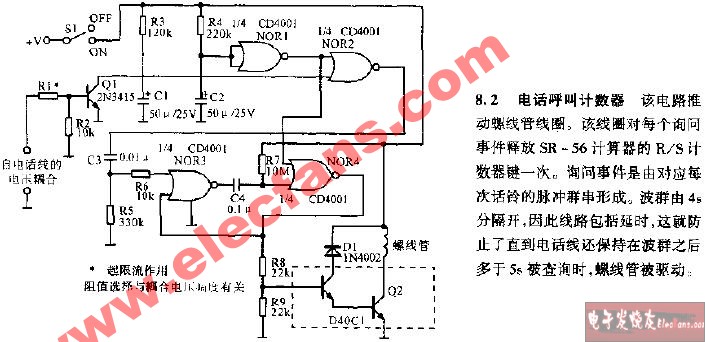

電話呼叫計數器電路

2009-03-29 18:29:30 595

595

CMOS可編程N分頻計數器電路圖

2009-03-29 09:55:36 738

738

電話呼叫計數器電路

2009-03-23 21:21:10 427

427

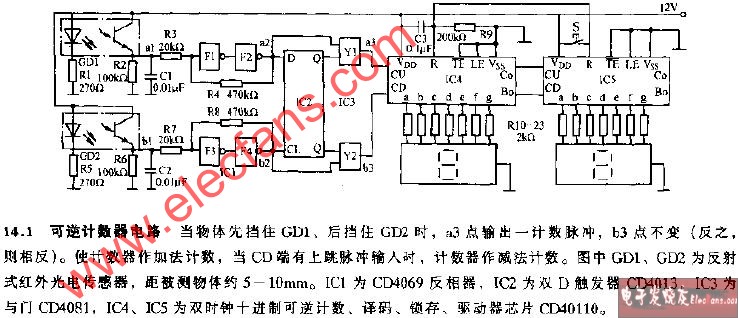

可逆計數器電路

2009-02-25 21:53:53 898

898

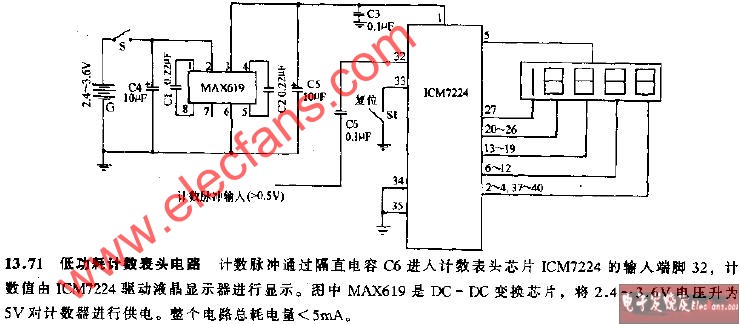

低功耗計數麥頭電路

2009-02-25 21:46:58 351

351

低功耗計數麥頭電路

2009-02-25 21:17:01 619

619

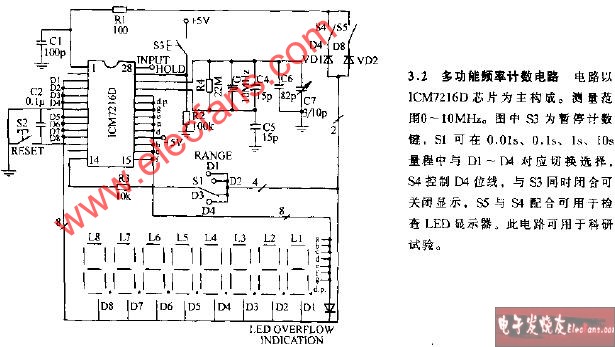

多功能頻率計數電路

多功能頻率計數

2009-02-09 16:10:13 675

675

電線自動成圈機計數電路

2009-02-06 10:14:02 589

589

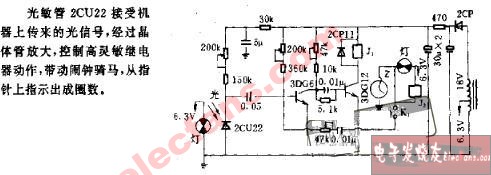

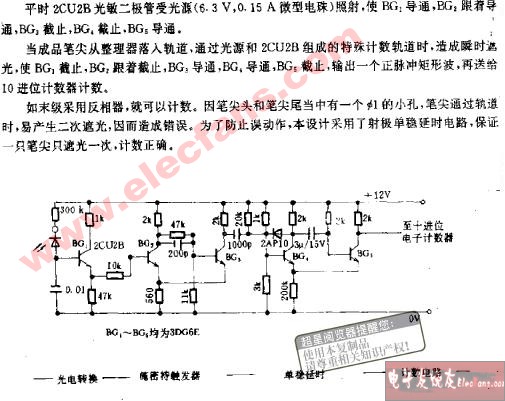

成品筆尖計數電路

2009-02-06 10:07:57 637

637

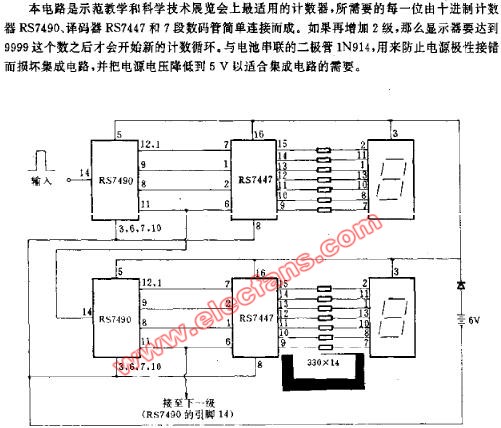

數字計數演示電路圖

成

2009-02-05 15:54:13 885

885

數字計數演示電路

2009-02-05 15:53:11 528

528

成品筆尖計數電路

2009-02-05 15:52:50 600

600

表演用的多位計數電路

2009-02-04 23:57:25 536

536

倒計時計數電路倒計時計數電路主要由計數器構成,它在整個系統設計中的作用是實現計時計數,在此我們選用減法計數器,因為本設計說明計時

2008-12-01 16:06:50 6986

6986 計數譯碼顯示在現代科學技術中應用非常廣泛,它由計數器、譯碼器和顯示器三部分組成,包含數字電子系統的組合邏輯電路和時序邏輯電路,因此本實驗是一個綜合性的實

2008-10-09 18:19:54 115

115 脈沖計數器電路圖,本計數器包括降整流電路,光控脈沖發生器,計數電路,譯碼,顯示電路。

2008-04-03 13:37:11 3295

3295

相位角測量采用硬件計數方式,而不使用單片機直接計數,因為用硬件計數可以把精度提得更高。這里我們使用兩片74HC161串聯組成256進制的串行進位計數方式。外部參考頻率選用1

2008-04-03 13:21:48 5924

5924

電子發燒友App

電子發燒友App

硬聲App

硬聲App

238

238

171

171

705

705 273

273 297

297

332

332 1124

1124 15

15 1630

1630 32

32 12

12 5466

5466

9216

9216

3316

3316

2567

2567

2923

2923 2939

2939 2859

2859

2654

2654 18610

18610

95799

95799

51924

51924

61651

61651

96386

96386

22819

22819

145644

145644

324594

324594

5011

5011 60783

60783

584471

584471

32541

32541 4

4 33

33 95

95 6157

6157

3245

3245

1344

1344

19

19 25

25 263

263 63

63 4593

4593

14122

14122

26072

26072

115

115 5924

5924

評論