???? 關(guān)鍵詞:能源組件,可編程門陣列FPGA,高速A/D轉(zhuǎn)換器件AD7825

1 引 言

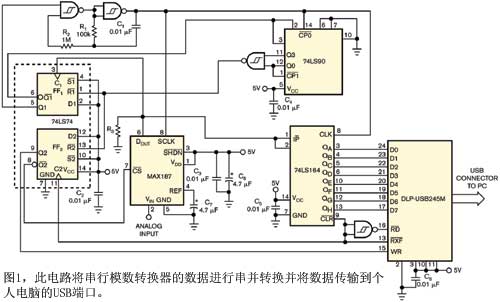

一般的數(shù)據(jù)采集系統(tǒng)通常由采樣/多路開關(guān)、A/D轉(zhuǎn)換電路、計算機(jī)I/O接口電路等組成。作為高速數(shù)據(jù)采集系統(tǒng)的設(shè)計,其主要考慮的是系統(tǒng)時序設(shè)計、放大電路的頻域特性、A/D芯片的選擇、數(shù)據(jù)緩存設(shè)計等問題。

考慮到本設(shè)計有10路數(shù)據(jù)輸入,500μs的數(shù)據(jù)采集時間,采樣速率高,須0.5μs采樣一次,因此決定不采用微處理器控制A/D變換器,而采用硬件直接處理來達(dá)到高速的目的。選用FPGA大規(guī)模可編程邏緝器件——ALTERA公司的EPM9320GC280-15提高響應(yīng)速度;選用ANALOGDEVICES公司的10MHz高速A/D轉(zhuǎn)換器AD7825來實現(xiàn)某能源組件氙燈放電電流波形的采集。

2 系統(tǒng)要求

2.1 系統(tǒng)條件

該能源組件氙燈放電電路主要包括預(yù)電離和主放電兩大部分。在預(yù)電離放電脈沖50μs后,主放電電路為氙燈提供脈寬為400μs的放電主脈沖。

2.2 技術(shù)指標(biāo)

系統(tǒng)工作電壓:23kV;主脈沖最大放電電流:15kA;峰值放電電流>4.8 kA;氙燈放電回路路數(shù):10路;放電電流脈寬:400μs±10%;放電脈沖形狀:工作在臨界阻尼狀態(tài)。

預(yù)電離電路工作電壓:23kV;預(yù)電離脈沖寬度:50μs;預(yù)電離相對主脈沖提前時間:120μs。

該能源組件氙燈放電電流波形采集系統(tǒng)必須具有強(qiáng)抗電磁干擾能力,在主脈沖放電1~2min內(nèi),對10路氙燈放電電流波形能迅速響應(yīng),將其準(zhǔn)確采集并存入主控臺數(shù)據(jù)庫。

3 芯片介紹

3.1 EPM9320GC280┐15簡介

EPM9320GC280-15內(nèi)含6 000個可用門,其引腳到引腳的最短傳輸延時為12ns,采用單+5V電源供電,可通過JTAG接口實現(xiàn)在線編程,并帶有可供168個用戶使用的I/O腳(其中5個為專用輸入腳)。該器件采用PGA封裝。其中TCK、TMS、TDI、TDO、VPP為編程腳;GCLK1、GCLK2、GCLR、GOE為專用輸入腳;VCCINT、VCCIO腳接+5V電源;GND接地;I/O為用戶可編程輸入輸出腳。在I/O腳作輸出使用時,可由用戶設(shè)定為0,1和Z三種狀態(tài)。

AD7825為高速420ns的8位A/D模數(shù)轉(zhuǎn)換器,4通道可同時取樣輸入并保持放大。另有2位的通道地址選擇口A0~A2以選擇某通道的轉(zhuǎn)換數(shù)據(jù)向外傳送。當(dāng)采用+5V單電源供電時,其模擬輸入電壓在0~2.5V間取值。具有8位A/D轉(zhuǎn)換結(jié)果并行接口輸出模式,采用DIP24形式封裝。

4 系統(tǒng)設(shè)計原理

4.1 原理框圖

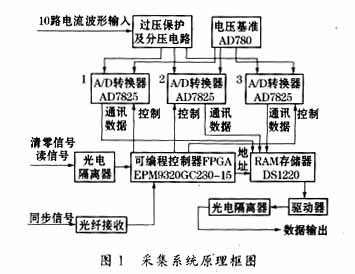

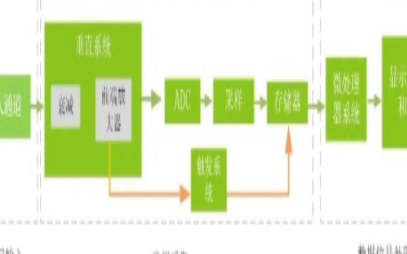

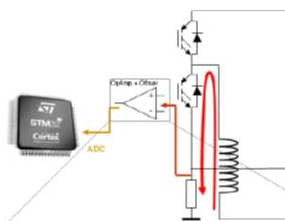

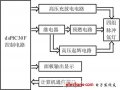

圖1為采集系統(tǒng)原理框圖,大規(guī)模可編程門陣列EPM9320GC280-15和A/D轉(zhuǎn)換器AD7825為整個系統(tǒng)的核心。AD7825所需的時序脈沖均由EPM9320GC280-15產(chǎn)生,RAM存儲器DS1220所需的地址信號、讀寫信號及片選信號也由EPM9320GC280-15依據(jù)一定時序關(guān)系送出。由于是強(qiáng)電流的工作環(huán)境,因此,雖是感應(yīng)電流且加了屏蔽,但還需考慮到線路上的各種干擾及線路特性阻抗的匹配。設(shè)計中采用穩(wěn)壓管Z1~Z10作10路波形輸入的吸收回路,以消除線路浪涌干擾。

4.2 FPGA內(nèi)部電路的設(shè)計

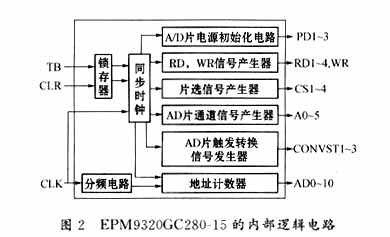

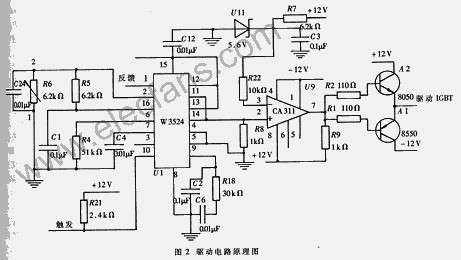

圖2為EPM9320GC280-15的內(nèi)部邏輯電路。主要依據(jù)AD7825的模數(shù)轉(zhuǎn)換等時序關(guān)系,由以下6個功能模塊組成:啟動AD7825功能,讀寫數(shù)據(jù)功能,片選產(chǎn)生功能,通道選擇功能,AD片觸發(fā)轉(zhuǎn)換信號發(fā)生和地址位碼產(chǎn)生功能。另外采取鎖存及封鎖信號等方法來清除實際運(yùn)用時所出現(xiàn)的各種干擾。

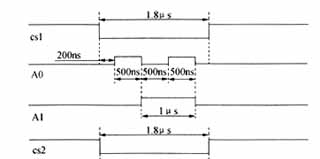

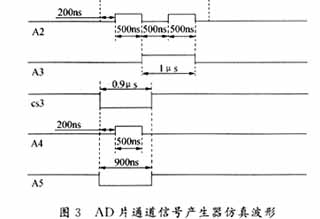

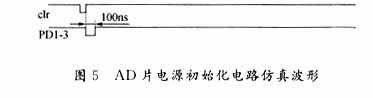

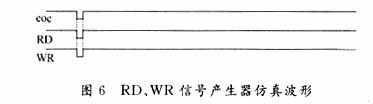

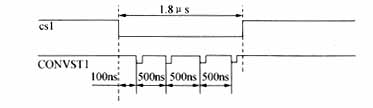

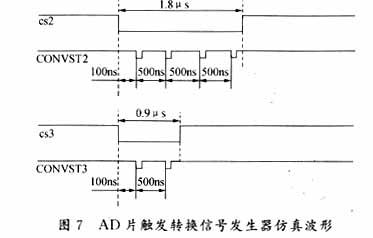

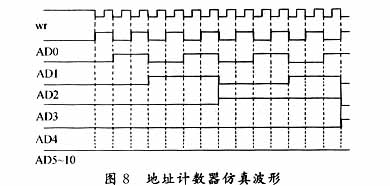

EPM9320GC280-15的內(nèi)部邏輯電路各功能塊產(chǎn)生的仿真波形見圖3~圖8。首先,清零信號CLR將3片AD7825電路初始化,外部時鐘同步,地址計數(shù)器的地址清為零地址;同步信號TB控制3片AD7825分別對10路電流波形進(jìn)行100次采集并轉(zhuǎn)換,另由AD7825內(nèi)部產(chǎn)生信號EOC(指示每次轉(zhuǎn)換已結(jié)束),控制AD7825的數(shù)據(jù)向RAM存儲器DS1220內(nèi)存儲。(凡小寫信號為控制信號,大寫信號為受控信號。)

4.4 電流放電波形

圖9為根據(jù)該采集電路采集的100個數(shù)據(jù)所繪制而成的一個電流放電波形圖。因有總共10路放電回路,所以,每放1次電(即收到1個同步脈沖),需采集10組共1000個數(shù)據(jù)。

5 結(jié)束語

在實際運(yùn)用中,本設(shè)計的實用性與穩(wěn)定性得到了驗證。引入現(xiàn)場可編程門陣列FPGA,可修改內(nèi)部程序及其邏輯功能,實時快速控制轉(zhuǎn)換,編程方便,可靠性高。另外,此控制電路采用2路供電方式:核心控制電路與外部輔助電路分別供電。核心電路EPM9320GC280-15與AD7825,由+5V電源經(jīng)DC/DC隔離后供電;外部輔助電路由+5V電源直接供電。這樣,既隔離了外部干擾,又保護(hù)了核心器件。

參考文獻(xiàn)

電子發(fā)燒友App

電子發(fā)燒友App

評論