??? 關鍵詞:Σ-△調制,小數分頻合成器,鎖相環,相位噪聲

1 引 言

在通訊技術飛速發展的今天,對信號發生器的要求越益苛刻。同時,隨著雷達技術、保密通訊、目標定位、衛星測控、精密制導及電子對抗等現代高技術在軍事領域及民用設備中的廣泛應用和普及,信號發生器必須要有極高的頻率穩定度和頻譜純度。

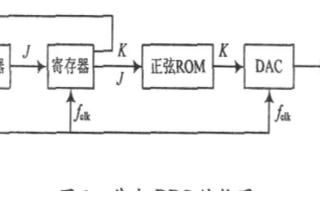

頻率合成技術是現代通訊系統的重要組成部分,它是將一個高穩定度和高準確度的基準頻率經過四則運算,產生同樣穩定度和準確度的任意頻率。頻率合成的方法可分為兩大類:直接合成法和間接合成法,其形式有:直接頻率合成器、鎖相頻率合成器和直接數字頻率合成器。目前應用較普遍的是直接數字頻率合成(DDS),其優點是分辨率高、成本低、控制靈活;其主要缺點是輸出頻率上限不能太高,另外,若設計不合理,由數字技術帶來的相位量化噪聲和D/A變換器帶來的幅度量化噪聲所形成的總輸出噪聲電平可能很高。隨著大規模集成電路的發展,利用小數分頻頻率合成技術解決了單環數字頻率合成器中高鑒相頻率和小頻率間隔之間的矛盾,但小數分頻存在嚴重的小數雜散,通常采用模擬相位內插的方法來抑制。一個理想的系統不要求任何模擬方法來抵消相位噪聲和寄生信號,因為這種抵消程度有一定的限度,優于1%的抵消是很困難的。一種完全的數字方案就是引入Σ-△調制技術,該技術是過取樣噪聲整型和數字濾波技術的結合,

小的頻率分辨率的實現依賴于電路的速度,這在當今的技術條件下已成為可能。

Σ-△調制頻率合成器是在小數分頻鎖相環的基礎上,采用全數字式Σ-△調制技術來抑制小數雜散,從而克服了模擬相位內插方法的一些缺點如:電路復雜、調試困難、價格昂貴等。它是一種新型的、先進的頻率合成器。

2 Σ-△調制技術原理分析

Σ-△調制技術源于廣泛應用于音頻范圍內的高分辨率A/D、D/A轉換器中的過取樣Σ-△轉換技術,其工作原理為:在對信號進行過取樣后,噪聲功率譜幅度降低,并通過一個對輸入呈低通對量化噪聲呈高通的噪聲整型器,將量化噪聲功率的絕大部分移到信號頻帶之外,而采用過取樣移出的噪聲不會與信號頻譜混疊,從而可通過簡單的濾波有效地抑制噪聲,比較容易用硬件電路實現。

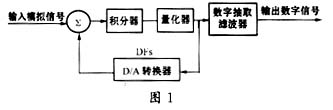

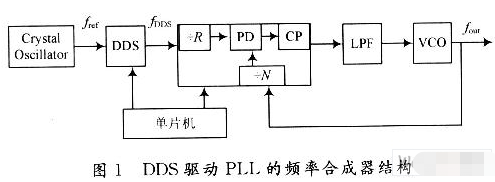

Σ-△A/D轉換器是基于將限帶輸入信號以較高的取樣頻率進行高速取樣,而對每個取樣信號量化比特數較低,經常使用一比特量化,這樣使Σ-△A/D轉換器獲得了許多優點,其原理框圖如圖1所示。其中,減法器、積分器、量化器和D/A轉換器組成反饋系統,使得積分器的電壓趨于零并使D/A轉換器的輸出逼近輸入值,所得數字輸出也逼近輸入信號而完成D/A轉換,圖中取樣頻率為DFs,Fs為 奈奎斯特取樣頻率,D遠大于一。由于采用過取樣,一方面改善了A/D轉換器的信噪比,另一方面對抗混疊濾波器的要求也降低。

Σ-△A/D轉換器是通過提高取樣頻率和噪聲整型來改善信噪比的。當輸入信號是隨機信號且輸入信號幅度大于分層電平(△)時,量化噪聲的功率譜密度在0~Fs/2頻帶內均勻分布,總噪聲能量為:

總噪聲能量只與量化級幅度有關,與其它因素無關,

而量化噪聲功率譜密度與取樣頻率Fs有關,即:

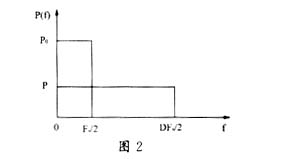

圖2為功率譜與取樣頻率的關系圖。顯然,如果量化級幅度相同,取樣頻率越高則功率譜密度越低,即在有用信號帶寬內的噪聲能量下降為原來的1/D,而有用信號功率是不變的,所以提高取樣頻率可以提高信噪比。

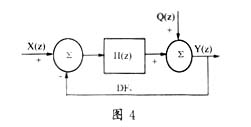

是環路內A/D轉換器所產生的量化噪聲,并設H(z)為一個單位增益離散時間積分器。對環路進行分析,可得:

由此可知,環路對輸入信號僅產生一個延遲,而對量化噪聲進行一個微分處理。將z=ejωT代入量化噪聲

的傳輸因子得:

而量化噪聲在0~DFS/2之間是均勻分布的,其功率譜密度為:

由此可知,經噪聲整型后,量化噪聲能量大部分被移向頻率高端,而需要提取的有效頻率段內的噪聲能量大大降低,使輸出信噪比得以提高。不難想象,如對量化噪聲實現多次微分即可獲得更好的噪聲整型效果。

在小數分頻頻率合成器中,所需的小數分頻比類似于D/A變換器的模擬輸出,而用于控制分頻器的數值類似于D/A變換器的數字輸入,因此,同樣可以將噪聲整型原理應用于合成器的小數分頻部分,從而可獲得更好的帶內噪聲特性。

3.1 小數分頻頻率合成器原理分析

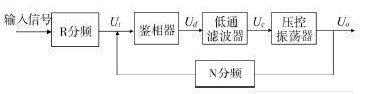

在一般的鎖相頻率合成器中,程序分頻器的分頻比為整數N,合成器輸出頻率最小間隔為鑒相頻率fr。而對合成器而言,頻率間隔應越小越好,由于合成器中鑒相頻率不可能無限制地低下去,且為實現快速鎖相,要求鑒相頻率越高越好。這樣就面臨著一對不可調和的矛盾。解決這一矛盾的方法是利用小數分頻頻率合成技術,這一方法已在當今頻率合成領域廣泛應用。

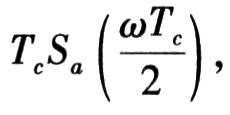

小數分頻頻率合成器是把VCO輸出頻率鎖定在參考鑒相頻率fr的N.F次諧波上。在小數分頻器中,整數分頻比周期性地從N到N+1地變化,使平均分頻比值落在N~N+1區間內。設一個平均周期內,除N的時間為TN,而除N+1的時間為TN+1,則環路鎖定后,VCO的平均輸出頻率f0為:

其中,N為分頻比的整數部分,.F為小數部分。

實際使用中可用一累加器的溢出來確定瞬間分頻比,設累加器最大容量為C-1,其輸入X=.f×C即X/C=.f,因此,當分頻器作除N操作時,到相位檢波器的VCO信號頻率為:

由于累加器求和相同的小數部分,其溢出對應于VCO相位誤差超過2π,因此,必須在一個參考循環內改變分頻比為N+1以消除VCO的相位差。周期性改變分頻比使VCO相位誤差呈鋸齒波變化,從而形成嚴重的小數雜散,必須加以濾除。而這種相位誤差是可以預測的,可以通過模擬相位內插的方法加以消除。但這種消除是有局限的,且電路相當復雜成本較高。如用Σ-△調制技術對小數雜散進行處理能得到比較理想的效果。

3.2 Σ┐△調制小數分頻頻率合成器的設計

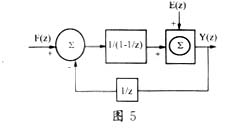

Σ-△調制小數分頻頻率合成器是對傳統的小數分頻頻率合成器中的小數分頻器加以改進,通過多級Σ-△調制器對累加器量化誤差進行再次處理從而獲得更好的相位誤差特性。圖5為累加器的數學

模型,顯然,相位累加器與一階Σ-△調制器具有相同的數學模型。雖然累加器作為數字一階Σ-△調制器對其自身量化誤差有一定的濾波作用,但其效果有限,因而傳統的小數分頻鎖相環難以獲得較低的

相位雜散。

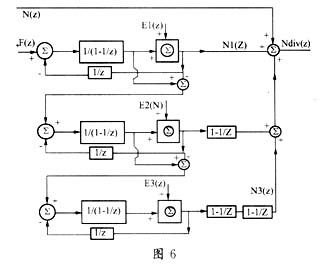

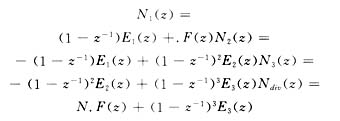

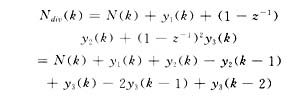

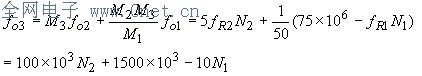

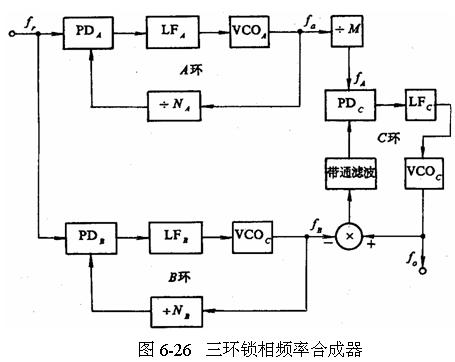

為對小數分頻器中引入的量化誤差進行有效的抑制,采用級連的高階Σ-△調制方案,由于每一級Σ-△調制均會引入量化噪聲,為實現噪聲整型同時考慮到電路穩定性的需要,對引入到下級的量化噪聲取反,并逐級增加延遲單元,使下一級Σ-△調制器輸出與上一級量化噪聲分量相抵消的信號,從而使高階Σ-△調制器輸出中只含N.F和最后一級Σ-△調制器所引入的量化噪聲。為簡化分析,現以三階Σ-△調制器為例對相位誤差函數進行分析。圖6為三階Σ-△調制Z域模型。原小數分頻器中的相位累加器作為第一級調制器。圖中N(z)為分頻比的整數部分,.F(z)為小數部分,Ei(z)(i=1,2,3)是每級Σ-△調制器引入的量化誤差,Ndiv(z)為Σ-△調制器的分頻比。由此可得:

N1(z)=

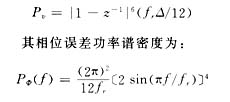

上式說明三階Σ-△調制器無失真地傳輸了輸入信號N.F(z),并只對第三階量化誤差進行三次微分。所以,這種鎖相環的實際輸出頻率為:

?![]()

由此式可知,通過三階整型輸出頻率抖動的功率譜密度為:

由于鎖相環具有較好的低通特性,從而可以消除小數分頻雜散。

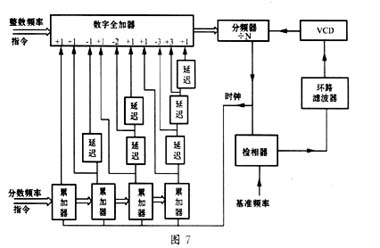

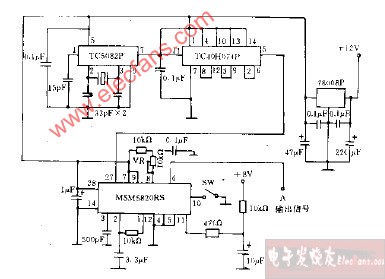

圖7為新的頻率合成器的原理框圖。圖中每個累加器的輸出和下一個累加器的輸入相接,累加器的溢出可以控制分頻比。為了減小剩余相位抖動,需合理控制分頻比,具體方法是第二個累加器的溢出必

須通過第一個微分控制分頻比,第三個累加器溢出通過第二個累加器影響的微分來控制分頻比等等。圖中輸入到程序分頻器的瞬間輸出為:

這樣,在數字電路中可用一組延遲單元和全加器來實現此等式。

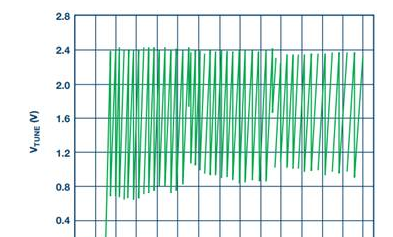

整個環路工作原理簡單描述如下:壓控振蕩器頻率預置在一個粗值上,經分頻器分頻(由于要改變分頻比來減小剩余相位抖動,此分頻器應為雙模或四模控制),分頻后的頻率與基準頻率在檢相器中比相,產生的差值信號經環路濾波器的積分和濾波,形成一直流控制信號加到VCO上微調VCO輸出頻率,使其頻率準確鎖定在預置頻率上,其頻率穩定度和準確度與基準頻率相當。

4 結束語

本設計采用全數字電路來實現Σ-△調制小數分頻器,不僅簡化了整個系統,而且使頻率合成器的性能得到了提高。利用此方法很好地解決了頻率分辨率與相位檢波器工作頻率之間的矛盾,使環路工作頻率有了很好的改善,同時大大提高了噪聲性能。與傳統的小數分頻合成器比較,在體積、成本和復雜程度等各方面都有明顯的優點。

參考文獻

2 J.C.Candy and O.J.Benjamin.The Structure ofQu-antization Noise from Sigma-Delta Modulation.IEEETrans.Commun.,vol.COM-29,pp.1316-1323,Sept.1981

電子發燒友App

電子發燒友App

評論