本文為大家帶來五款五人表決器電路設計方案。

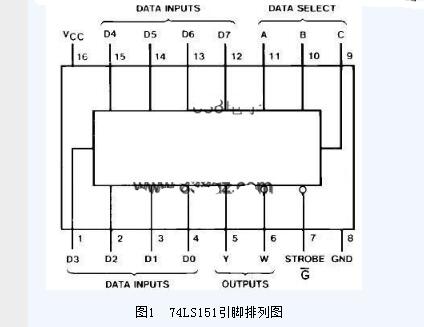

五人表決器電路設計方案一:基于74LS151設計的五人表決器電路

系統原理

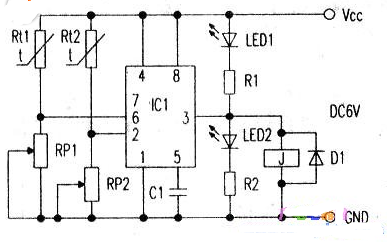

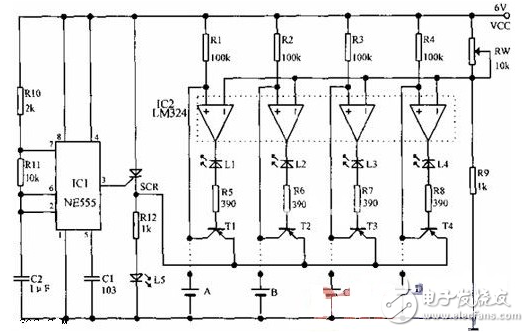

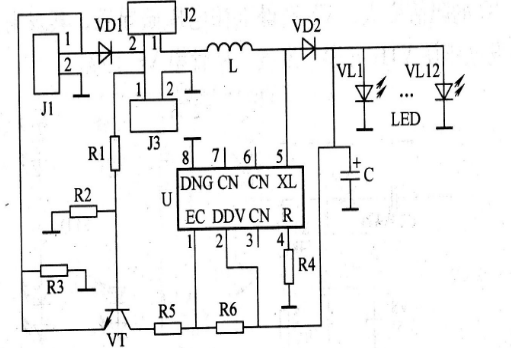

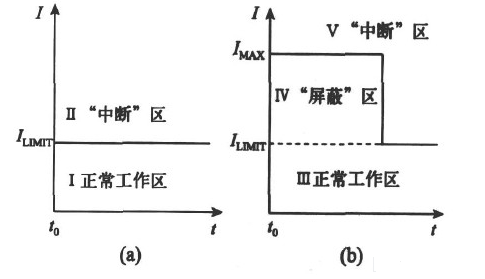

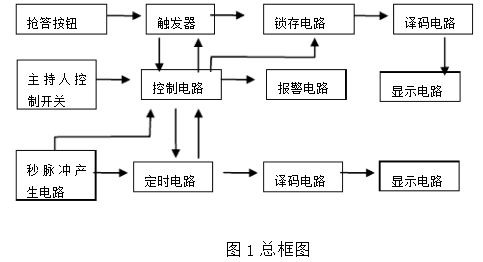

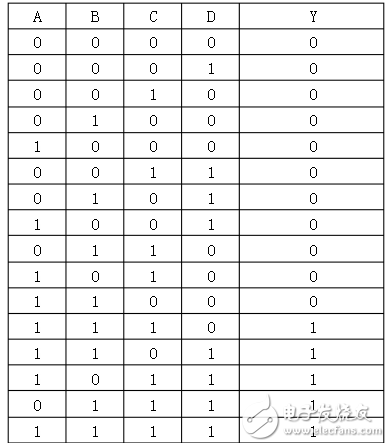

五人表決器,只要贊成人數大于或等于三,則表決通過。因此,只需將每位表決人的結果相加,判斷結果值。設五個開關A、B、C、D、E作為表決器的五個輸入變量,輸入變量為邏輯“1”時,表示表決者“贊成”,紅燈亮;輸入變量為“0”時,表示表決者“不贊成”,紅燈不亮;輸出邏輯“1”時,表示表決“通過”,綠燈亮;輸出邏輯“0”時,表示表決“不通過”,綠燈不亮;當表決器的五個輸入變量中有3個以上(含3個)為“1”時,則表決器輸出為“1”,此時綠燈就亮了。

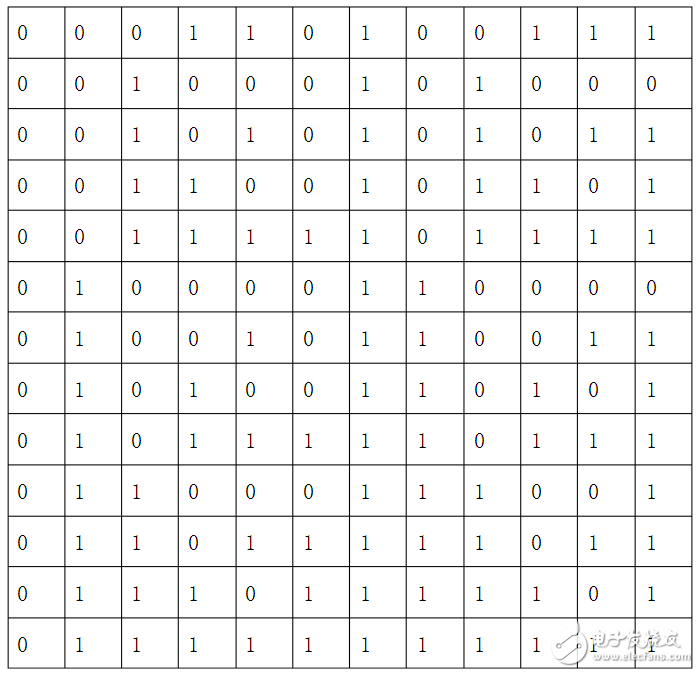

真值表

如果綠燈亮了,則表示表決通過,若綠燈不亮了,表示不通過。

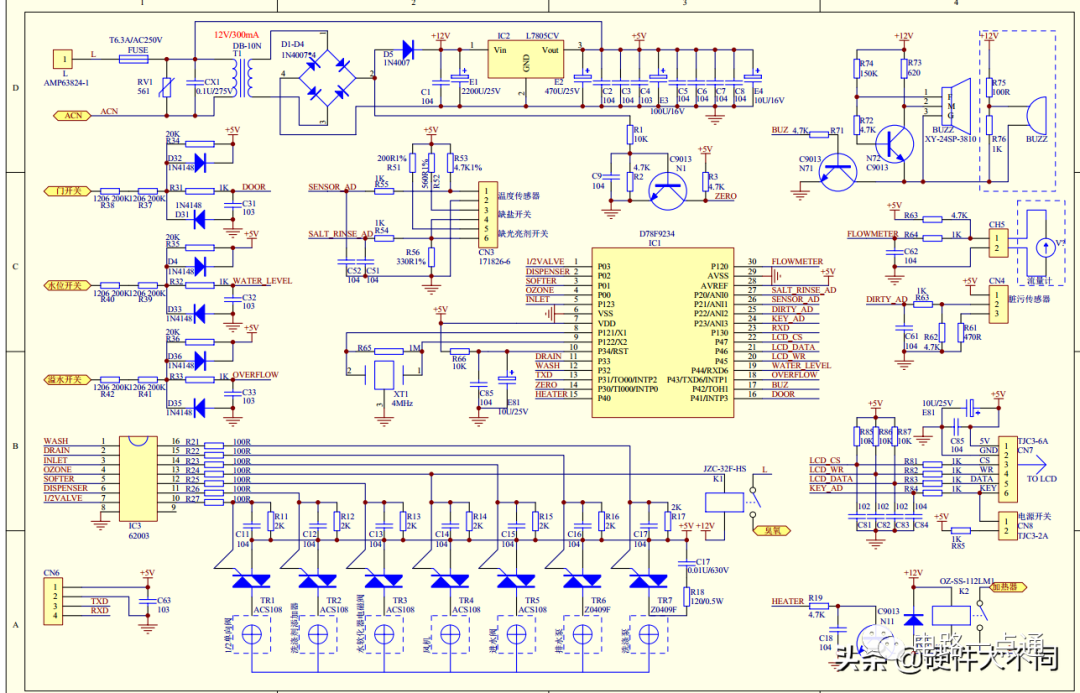

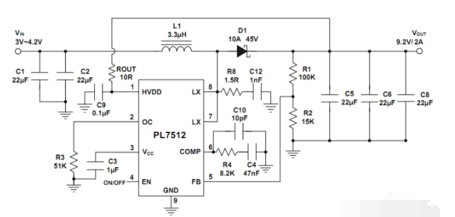

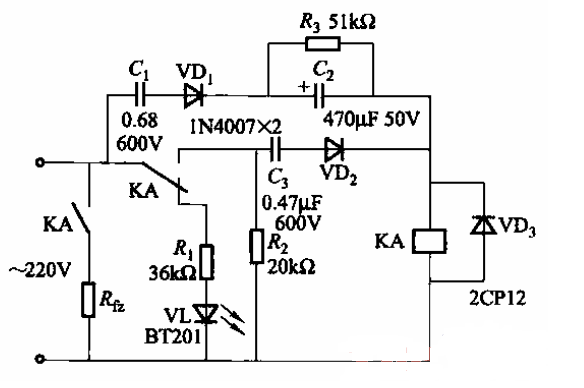

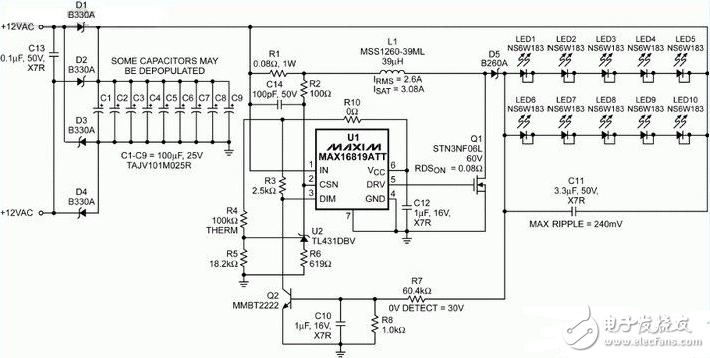

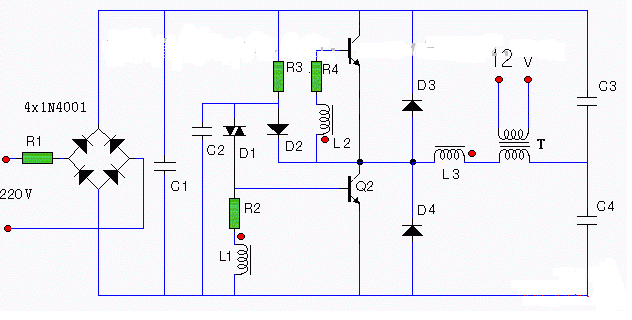

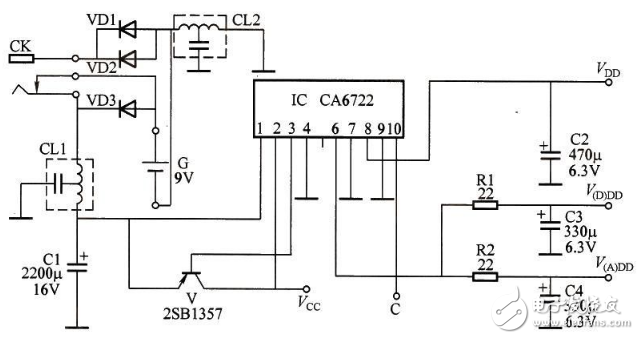

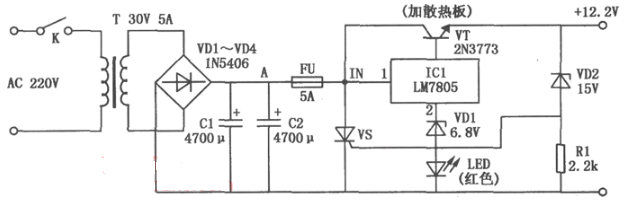

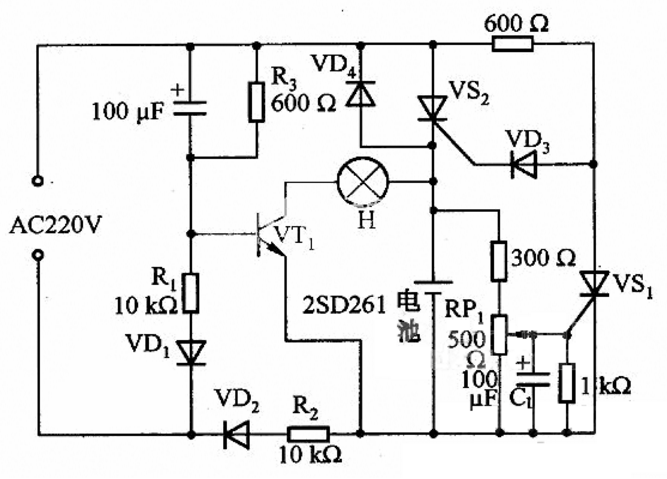

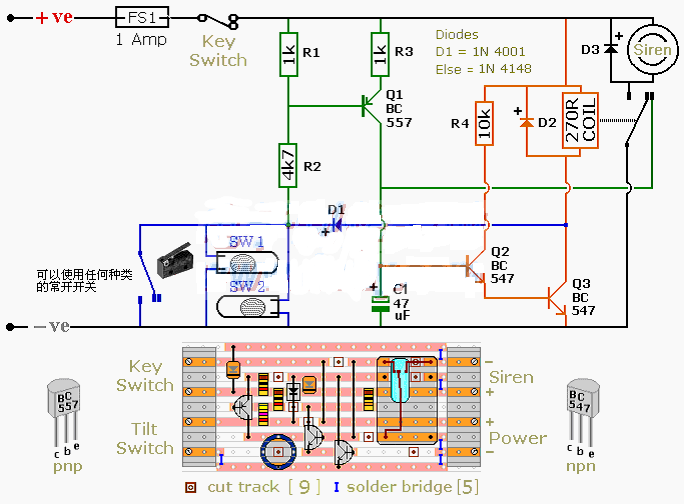

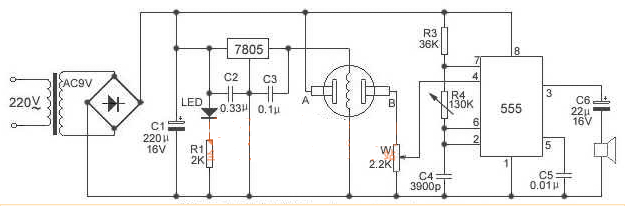

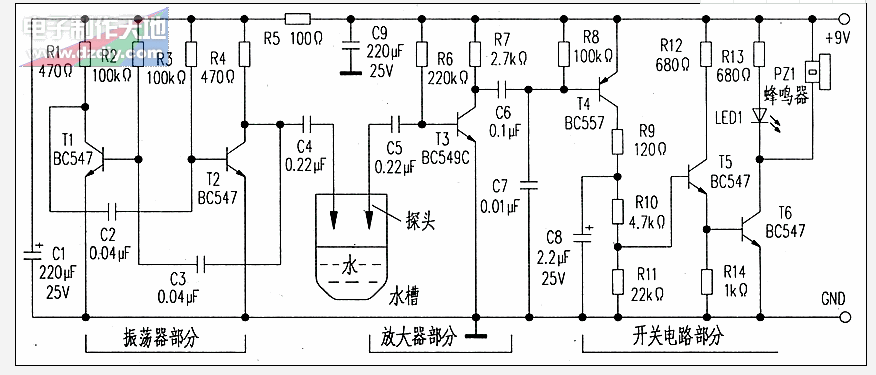

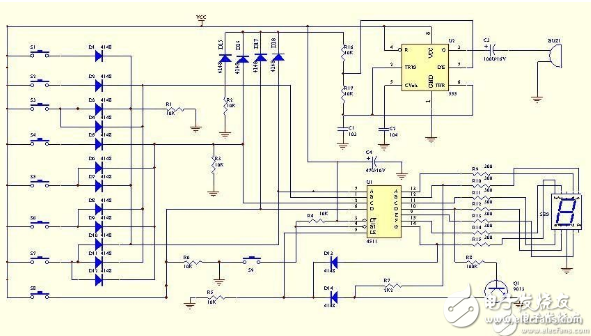

電路設計

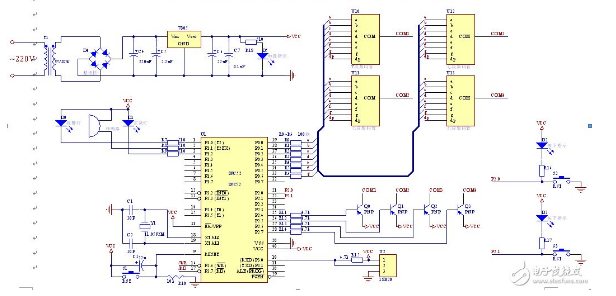

原理圖

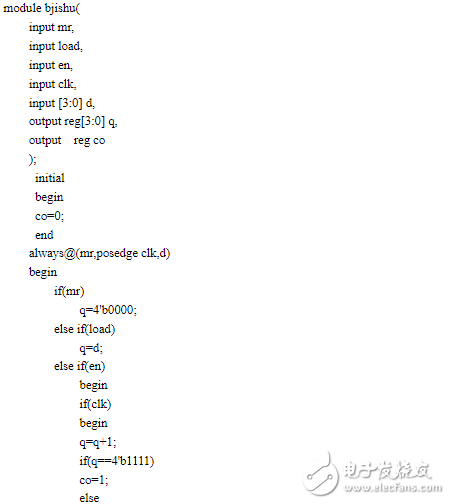

五人表決器電路設計方案二:verilog 五人表決器

程序設計

module vote5(a,b,c,d,e,f);

input a,b,c,d,e;

output f; reg f;

reg[2:0] count1;

initial count1=0;

always@(a,b,c,d,e)

begin

count1《=a+b+c+d+e;

f=count1《3?0:1;

end

endmodule

測試程序

module test;

reg a;

reg b;

reg c;

reg d;

reg e;

wire f;

vote5 uut (

.a(a),

.b(b),

.c(c),

.d(d),

.e(e),

.f(f) );

initial begin

a = 0;

b = 0;

c = 0;

d = 0;

e = 0;

#100

a = 1;

b = 0;

c = 0;

d = 0;

e = 0;

#100

a = 1;

b = 1;

c = 0;

d = 0;

e = 0;

#100

a = 1;

b = 1;

c = 1;

d = 0;

e = 0;

#100

a = 1;

b = 1;

c = 1;

d = 1;

e = 0;

#100

a = 1;

b = 1;

c = 1;

d = 1;

e = 1;

end

endmodule

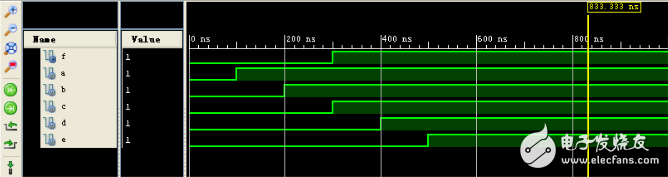

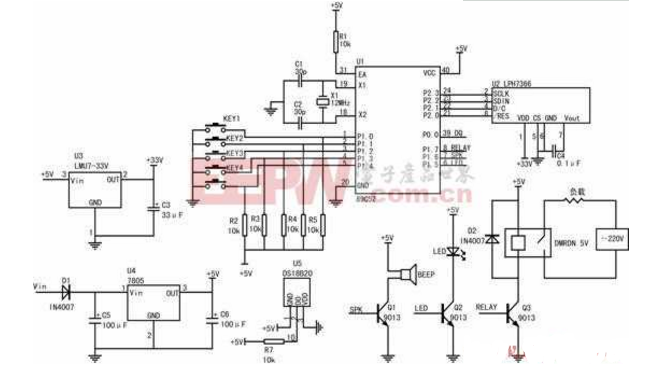

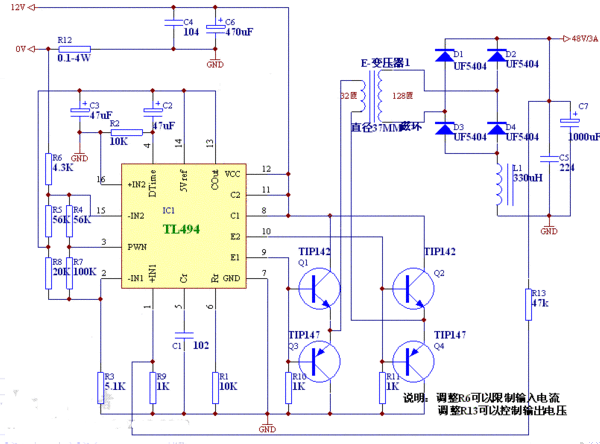

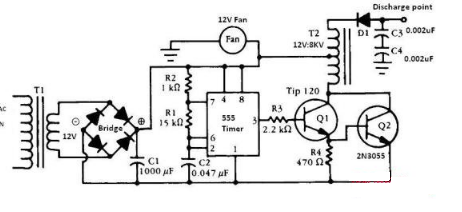

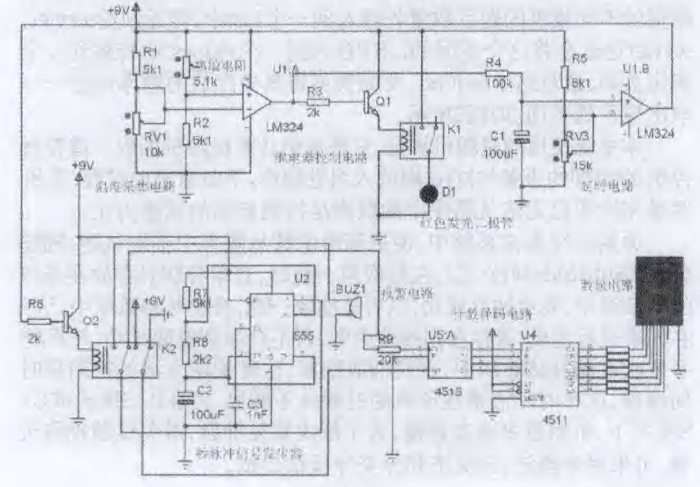

仿真圖

電子發燒友App

電子發燒友App

評論