74ls160設計數字秒表方案匯總(一)

現場可編程門陣列(簡稱 FPGA)是20 世紀 80 年代中期出現的高密度可編程邏輯器件,采用SRAM開關元件的 FPGA 是易失性的,每次重新加電,FPGA 都要重新裝入配置數據。突出優點是可反復編程,系統上電時,給 FPGA 加載不同的配置數據,即可令其完成不同的硬件功能。這種配置的改變甚至可以在系統的運行中進行,實現系統功能的動態重構。

“在系統可編程”(簡稱 ISP)是指對器件、電路或整個電子系統的邏輯功能可隨時進行修改或重構的能力,支持 ISP 技術的可編程邏輯器件稱為在系統可編程邏輯器件,它不需要專門的編程器,利用計算機接口和一根下載電纜就可以對器件編程了。

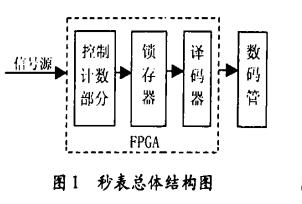

1、總體結構

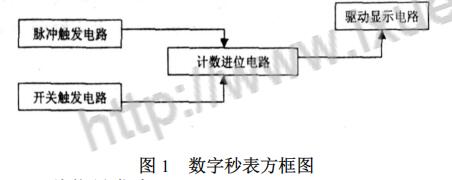

本文利用 EDA 技術中的 Max + plus Ⅱ作為開發工具,設計了一款基于 FPGA 的數字式秒表 ,并下載到在系統可編程實驗板的 EPF10K10LC84 - 4 器件中測試實現。其總體結構框架如圖1 所示。圖中的信號源是由實驗板上的時鐘信號經分頻而得到的 0. 1 秒信號;控制計數部分由一個計數模塊 ctrl 構成,用來實現計時功能,鎖存器模塊 latch 用來對數據進行鎖存 ;而譯碼器模塊 DISP 用來對計數結果進行掃描譯碼;數碼管用來顯示秒表的工作結果。

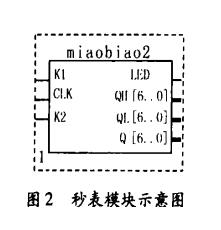

2、電路設計

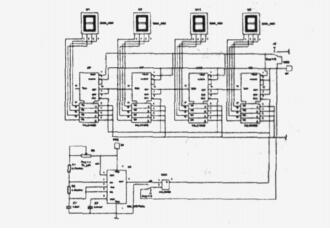

圖2為數字式秒表的模塊示意圖。輸入信號有三個,分別是 K1 , K2 和 CLK;輸出信號有四個,分別是 LED ,QH[ 6. 。 0 ] ,QL[6. 。 0 ] 及 Q[ 6. 。 0 ]。其中 K1 為“開始/ 清零鍵”,接的是控制計數部分的整體清零端,該清零信號低電平有效。要求按下 K1 時計時開始 ,再按一下,停止計時,恢復到零狀態。K2 為“固定顯示鍵”,接的是鎖存器 74373 的允許鎖存端 G,該信號是高電平有效。在計時過程中,按下 K2 時,鎖存數據 ,顯示固定 ,但計時仍繼續 ;按第二下時 ,顯示從新時間開始。CLK 為時鐘信號 ,必須是秒表計時所需的最小單位 0. 1S。

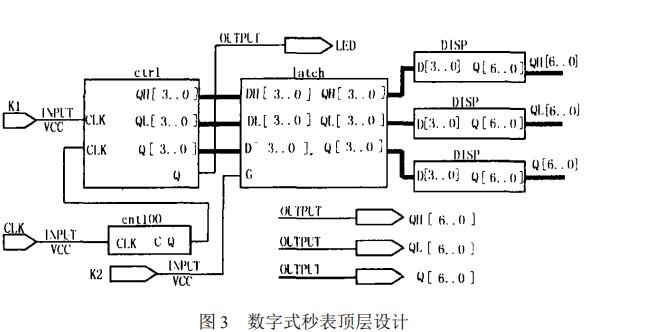

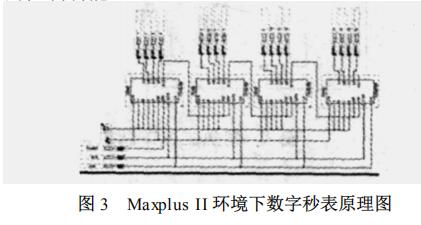

QH[6. 。 0 ] ,QL[6. 。 0 ] 及 Q[6. 。 0 ] 接三個數碼管,分別表示秒十位,秒個位和秒十分位。LED 接發光二極管用來表示秒表的分位,當秒表計時超過59. 9 秒時 LED 燈亮,且能持續表示到 1分 59. 9 秒,然后燈滅,同時數碼管重新計時顯示,即該數字式秒表的計時范圍從0 到2 分鐘。基于原理圖編輯和VHDL語言,并使用從上到下的設計方法設計的秒表,其具體的線路構成如圖3 所示。

在總體電路圖中,根據設計要求,輸入信號 K1、K2 應采用脈沖開關。由于實驗板上除了撥動開關就是瞬時的按鍵開關,且按鍵開關平時都呈高電平,按一下為低電平。故在實際測試時采用了撥動開關來模擬脈沖開關。根據設計要求將K1、K2 平時置于相應的高、低電平狀態,需要清零或固定顯示時再將它們分別置于相應的位置上即可。

3、模塊設計

在設計電路時,要遵循從上到下的設計原則。首先從系統設計入手,在頂層進行功能劃分和結構設計,頂層模塊中的每個次層模塊均可完成一個較為獨立的功能,次模塊在調試成功后可生成一個默認符號,以供上一層模塊調用。

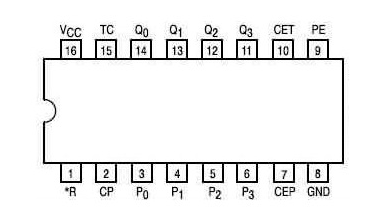

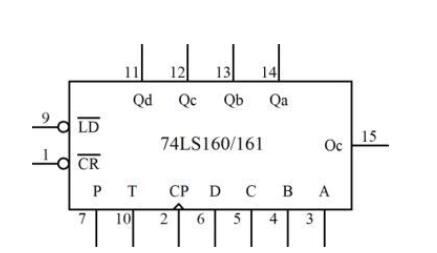

3. 1、時鐘信號模塊 cnt100

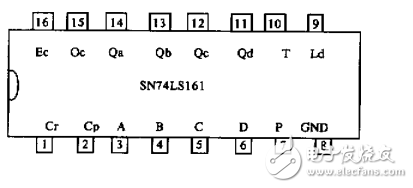

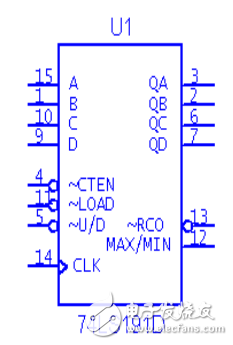

由于最終的設計結果要下載到可編程邏輯器件中測試,而承載該芯片的“在系統”可編程實驗板上最小也是1 kHz 的時鐘源,而秒表計時所需的最小單位為 0. 1s,故采用 2 片 74160,利用并行輸入方式,接成 100 進制計數器(00~99),將 1 kHz 信號變成 10 Hz (即 0. 1 s),從而達到分頻的目的。編譯通過后創建的默認符號為 cnt100,其輸入信號為 CLK,輸出信號為 CQ(即高位的進位端 RCO) 。

3. 2、控制計時模塊 ctrl

從 Maxplus2 器件庫中調用 3 片 74160,采用串行時鐘方式,連接成六百進制計數器(即 0~599),用來表示秒位。將 3 片 74160 的清零端 CLR 連接在一起,用來做秒表的整體清零端。再調用器件庫中的 J K觸發器,連接相應控制端形成 T′觸發器,將六百進制計數器的進位信號接 T′觸發器的時鐘端。平時其輸出端 Q 保持低電平,所接發光二極管不亮 ;當計時到 59. 9 秒時,由于有進位信號到來,因此時鐘端出現脈沖下降沿,觸發器翻轉,Q 由低電平變為高電平,發光二極管點亮,表示已計時到 1 分鐘。再計到 1分 59. 9 秒時,過 1 秒,燈滅,同時數碼管重新計時顯示。該控制模塊為圖 3 中 ctrl 模塊。

3. 3、鎖存器模塊 latch

因為秒表設計中要求在計時過程中能隨時固定顯示時間,而計時仍然繼續,所以要用到鎖存器。在本例中適宜采用 CD4511 芯片,因為它集合了鎖存、譯碼和驅動功能。但由于 Maxplus2 器件庫中沒有此類芯片,故以鎖存器 74373 外加譯碼器 7447 (DISP) 代替。在設計時從器件庫中調用 2 片 74373 (8 位鎖存器), 將它們的 OEN 統統接低電平,允許數據輸出。G端接一起,作為允許數據鎖存端 (高電平有效) 。鎖存器部分編譯通過后創建的默認符號見圖 3 中的 latch 模塊,輸入信號有四個,分別是 DH[ 3. 。 0 ] 、DL[3. 。 0 ] 、D[3. 。 0 ] 及 G,輸出有三個,分別是 QH[3. 。 0 ] 、QL[3. 。 0 ]及 Q[3. 。 0 ] 。

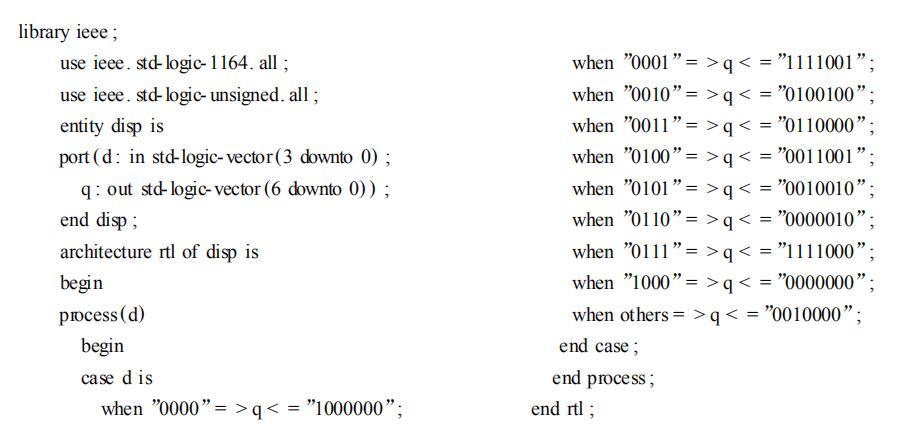

3. 4、譯碼顯示模塊 DISP

譯碼器可直接從器件庫中調用 7447 (共陽極譯碼器),將它的控制端按要求接好,形成默認符號 ;也可用 VHDL 語言編程,將 4 位 BCD 碼譯成 7 段數碼管的編碼(0~9),現采用 VHDL 語言編程,編譯無誤后創建默認文件符號 DISP 以供上層電路調用。顯示部分直接采用實驗板上的 3 個共陽極數碼管,不用將譯碼器的輸出 a~g 具體連線到實驗板上數碼管的 7 個段,只需將其輸出端口定義到可用作數碼管顯示的器件的 I/ O 引腳上即可。7 段數碼管譯碼器源程序如下

4、編程及測試

為設計項目選定 FLEX10K系列中的 EPF10K10LC84 - 4 器件,鎖定頂層設計中各端口所對應的引腳號,并編譯通過。然后對器件編程,使用 ByteBlaste 下載電纜把項目以在線配置的方式下載到 ISP 實驗板的 EPF10K10LC84 - 4 器件中,按相應的 K1、K2 鍵,觀測數碼管及發光二極管的狀態,發現顯示結果正確。該數字式秒表具有清零功能,能夠在計時過程中隨時停止計時,恢復到初始狀態。且具有鎖存/ 計時功能,能在計時過程中通過按“固定顯示鍵”,將顯示固定住,而計時仍繼續 ;再按下鍵,顯示從新時間開始。實驗證明該秒表工作正常,基本上已達到了預期的設計要求。

5、結束語

在Max + plus Ⅱ開發環境下,采用自頂向下的設計方法有利于在早期發現結構設計中的錯誤,避免不必要的重復設計。再結合基于 FPGA 的“在系統”可編程實驗板,輕輕松松就能實現各種電子產品的設計,現場觀察實驗測試結果。大大縮短了產品的設計周期和調試周期,提高了設計的可靠性和成功率,充分體現了可編程邏輯器件在數字電路設計中的優越性。

74ls160設計數字秒表方案匯總(二)

數字秒表是一種常用的計時工具,以其價格低廉、走時精確、使用方便、功能多而廣泛應用于體育比賽中。下文介紹了如何利用中小規模集成電路和半導體器件進行數字秒表的設計。本設計中數字秒表的最大計時為 99. 99s,分辨率為 0. 01s,數碼管顯示,具有清零、啟動計時、暫停及繼續計時等功能。當計時停止時,秒表保持所計時間直至被清零復位。本設計由四個 74LS160 計數器實現計數功能,一個555 定時器產生 100 Hz 脈沖,四個數碼顯像管顯示計時,再加兩個控制開關,一個控制啟動和暫停,另一個控制清零。

1、數字秒表的工作原理

電子秒表要求能夠對時間進行精確記時并顯示出來,因此要有時鐘發生器,記數及譯碼顯示,控制等模塊,系統框圖如下 :

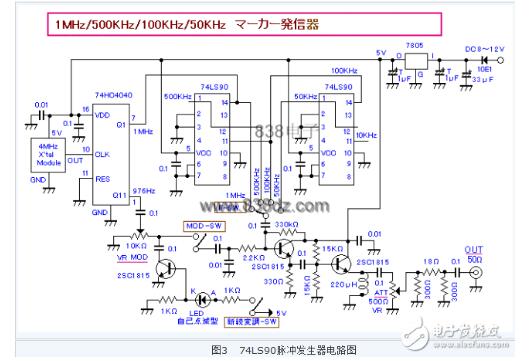

1. 1 秒信號發生器

利用 555 定時器構成的多諧振蕩器產生秒脈沖發生器。由于 555 定時器的比較器靈敏度高,輸出驅動電流大,功能靈活,再加上電路結構簡單,計算比較簡單。利用 555 定時器構成的多諧振蕩,在電路中我們選擇數據如下 : C = 1 uF, R1 = R2 。利用公式 : f = 1/ ( R1 + 2 R2) Cl n2根據 設 計 要 求, 需 要 精 確 到 0. 01s, 故 f =100Hz,帶入上式得 :R1 = R2 = 4. 8 KΩ。在 Multisim環境下的原理圖中,取 R1 = R2 = 4. 7 KΩ,并且在 R1支路串聯一個 1 KΩ的電位器,來調節脈沖信號的精度。此信號從 555 定時器的 3 引腳 OU T 端輸出,送到計數器 74LS160 的脈沖輸入端 CP,作為計時脈沖。

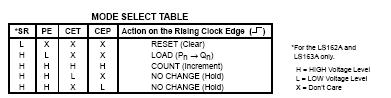

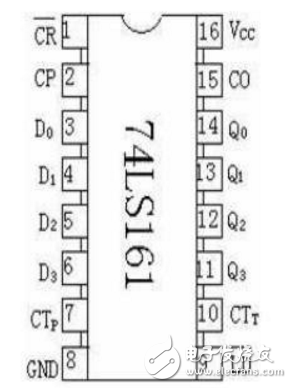

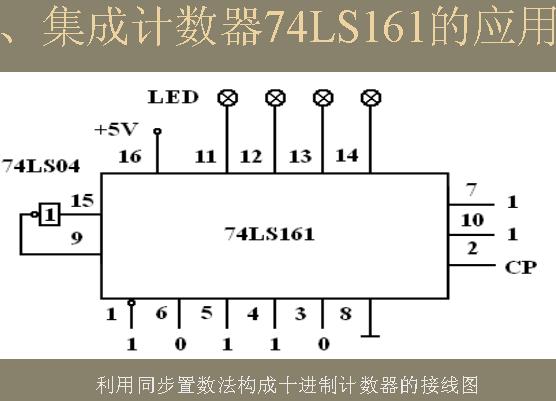

1. 2 計數進位部分

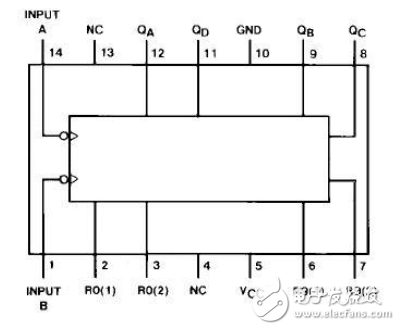

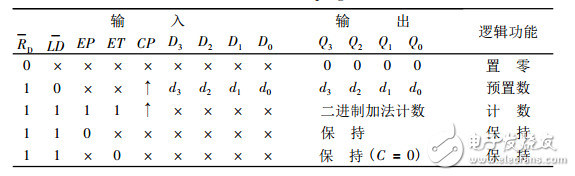

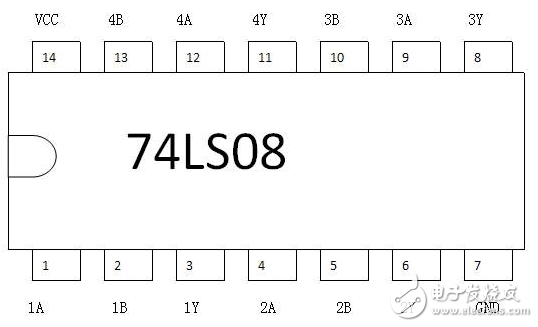

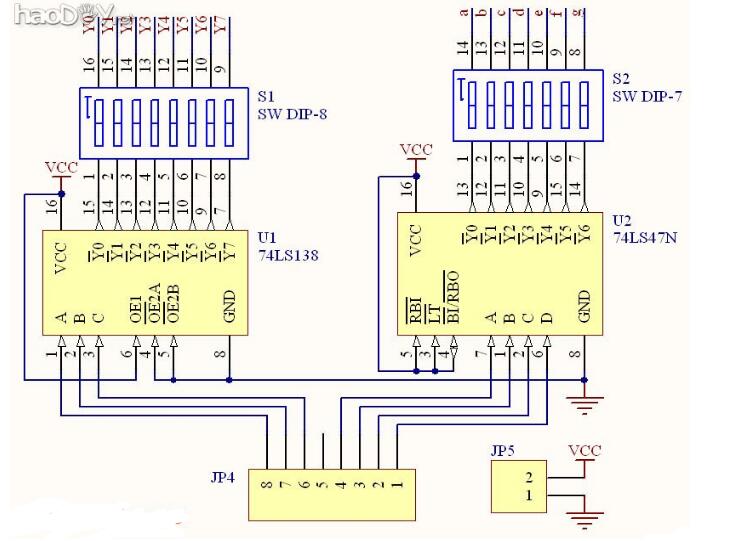

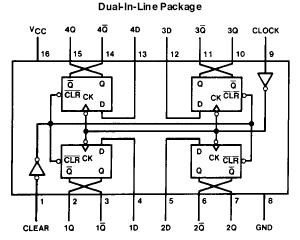

利用 74LS160 同步十進制加法計數器實現計數功能。這個計數器是十進制的,在設計時電路比較簡單。而且可以實現清零功能, EP, ET,可以實現保持功能。可以很方便的實現清零,開始,暫停和繼續這四個功能。具體電路原理如圖 2 所示。

1. 3 譯碼及顯示電路

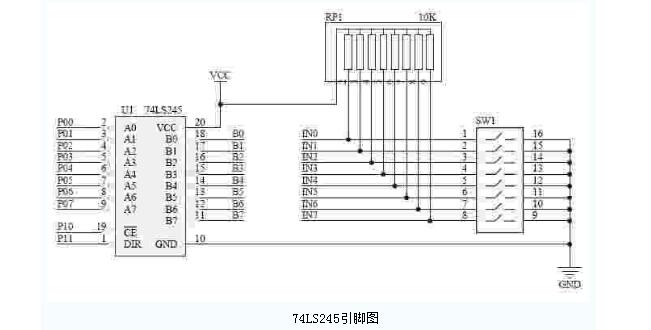

將秒計時器 74LS160 的 4 個輸出端 QD、QC、QB 和 QA 分別對應接至譯碼器 74LS48 的輸入端,譯碼后的輸出端接至共陰級 7 段數碼管的 a~g 端,則顯示器將進行 0~9 十進制數字顯示。我們在Multisim 環境下繪制原 理 圖 的 過 程 中, 選 用 將74LS48 和 7 段數碼管合二為一的 DCD -HEX。

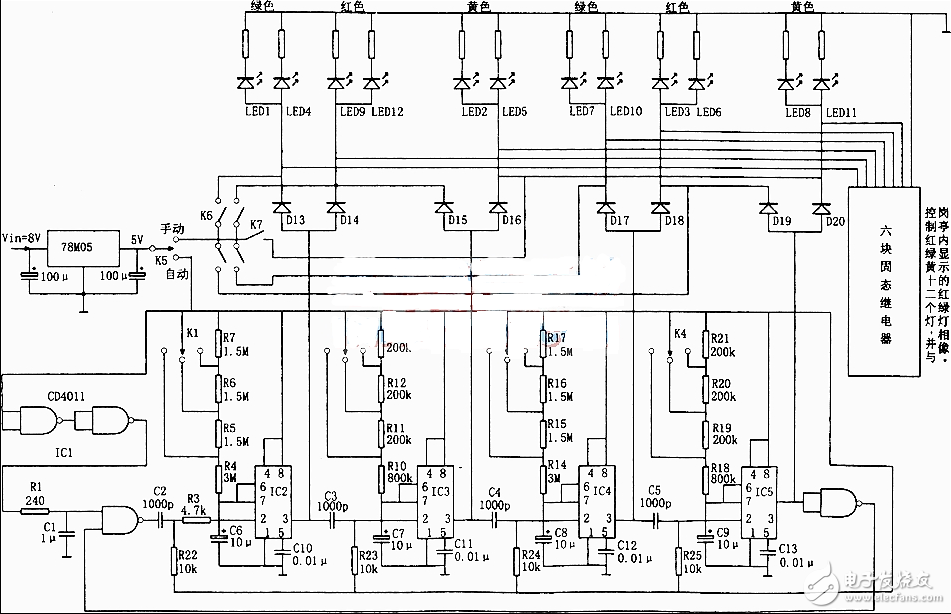

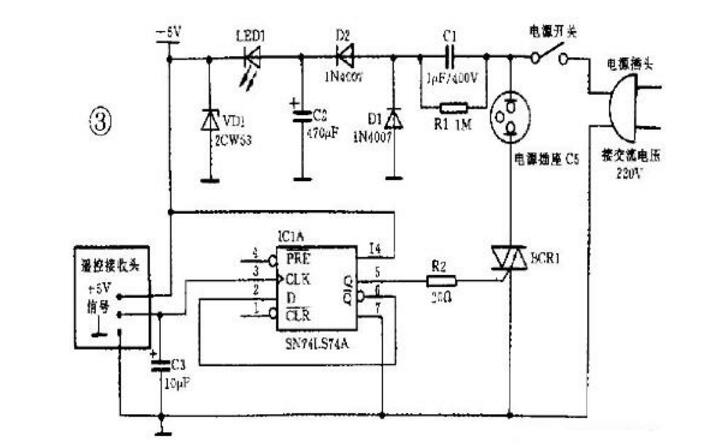

1. 4 控制電路

采用J1 和 J2 這樣 2 個開關,實現相關的控制功能。J1 接高電平時,與非門 U4A 打開,時鐘脈沖送入計數器進行計數顯示 ;J1 接低電平時,與非門U4A 被封鎖,計數器保持原來計數狀態暫停計數。J2 接高電平時,計數器正常計數 ;J2 接低電平時,所有計數器清零,實現清零復位的功能。

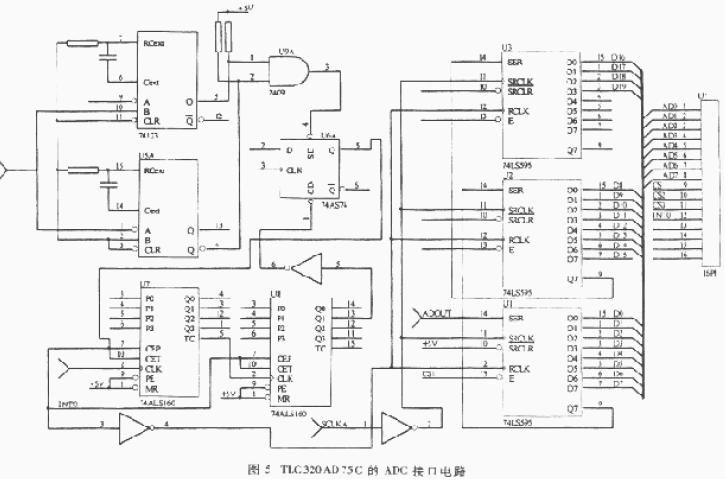

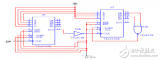

2、Multisim 環境下的原理圖與仿真

電路的四個 74LS160 計數器從右往左,分別為0. 01s,0. 1s,1s,10s 的計數器。同時四個計數器都為十進制。每個計數器均有四個接口接到后面的顯示電路的 QD、QC、QB 和 QA。74LS160 具有自啟動,避免電路進入死鎖狀態。顯示電路由四個七段譯碼顯示管組成,并由數字電子實驗箱集成。整個電路由 555 定時器產生 100Hz 時鐘信號,對電路進行時鐘控制。邏輯開關由高低電平控制電路的開始暫停以及復位清零。當開關J1 處于高電平時,電路正常計數 ;轉換為低電平時開始暫停保持 ;再次換為高電平繼續計數。開關J2 處于高電平時,電路正常工作 ;處于低電平時,電路清零復位。Multisim 環境下數字秒表總電路原理圖如圖 2。

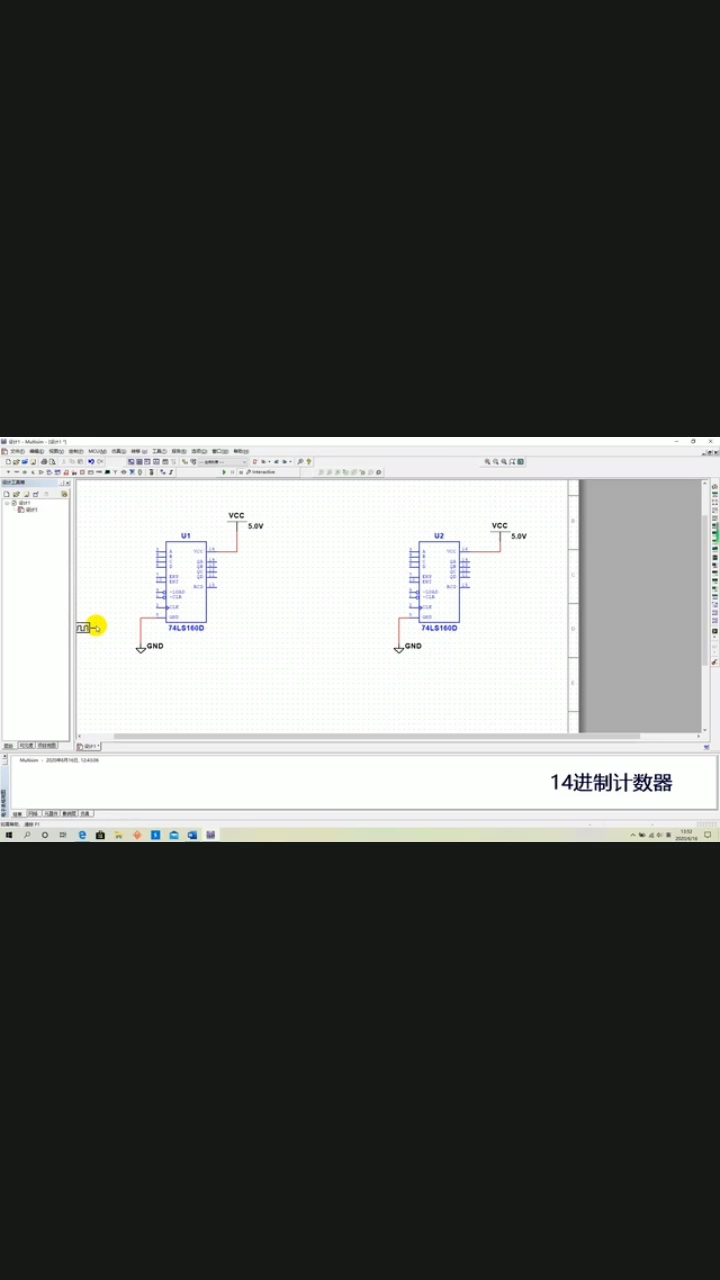

3、Maxplus II 環境下的原理圖與仿真

圖 3 為 Maxplus II 環境下的原理圖。CL K 接100Hz 的時鐘脈沖,為了方便觀察結果,實驗中設置的頻率可高于 100Hz。CLR 是清零按鈕。PAUSE是暫停繼續按鈕。74LS160 的輸出端 QD、QC、QB和 QA 從 0000 到 1001 從圖 2 可以看出在中水進水溫度相同的條件下,熱泵機組制熱量隨冷凝器出水溫度的上升有所降低,而且蒸發器側中水進水溫度的上升時,制熱量隨之上升的比較明顯。并從圖中知,在蒸發器側中水溫度從 13 ℃上升到 15 ℃時,制熱量的變化速度要小于從 15 ℃上升到 17 ℃的過程,說明蒸發器側中水進水溫度愈高對制熱量越有幫助。

圖 3 可知 :在蒸發器側中水進水溫度不變的情況下,隨著冷凝器出水溫度的上升,機組的輸入功率呈明顯上升的趨勢,結合圖 2 中表現的制熱量下降的趨勢,導致了圖 4 中制熱性能系數下降 ;在冷凝器出水溫度不變時,隨著蒸發器側中水進水溫度的上升,輸入功率呈緩慢增大的趨勢,機組的制熱量也在增大,對應制熱工況下的性能系數曲線可看出性能系數也在上升,但它的上升趨勢比較平緩。說明制熱量的變化趨勢要快于輸入功率的變化趨勢,熱泵機組能夠以較高的性能運行。

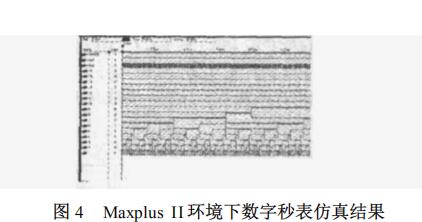

圖 4 為 Maxplus II 環境下仿真結果。仿真結果表明,所設計 99. 99 數字秒表電路可正常工作。編程下載后, 將 CL K 接固定頻率的信號, CLR 和PAUSE 分別接兩個開關。將 74LS160 的輸出端QD、QC、QB 和 QA 分別接不同的發光二極管以顯示各個計數狀態,或通過顯示譯碼器接數碼顯示。顯示結果驗證了所設計電路能夠正常計數。通過CLR 和 PAUSE 開關對電路工作狀態進行控制實驗,測試結果表明所設計控制單元電路能實現相關的控制功能。

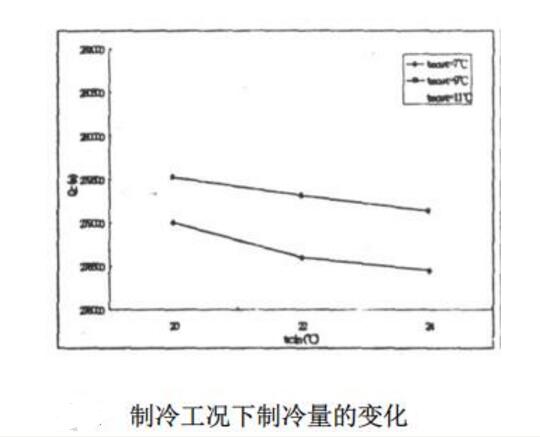

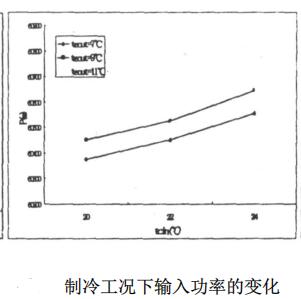

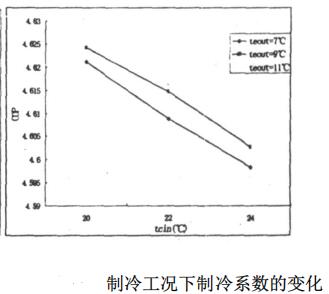

3. 2、制冷工況下 :保證中水源熱泵機組冷凝器側進

水溫度相同進行測試。圖 5、6、7 分別為制冷工況下制冷量、輸入功率和制冷性能系數的變化曲線。由圖 5 可以看出,在冷凝器進水溫度相同條件下,制冷量隨蒸發器出水溫度的上升而增大 ;在蒸發器出水溫度不變時,機組制冷量隨冷凝器進水溫度上升而減小趨勢很明顯。但機組的制冷量隨冷凝器進水溫度的變化的過程中,其變化趨勢的大小是不同的,從圖中可看出 20~22 ℃的變化趨勢要比 22~24 ℃的趨勢要快一些。可見 :中水溫度的變化對熱泵機組的制冷量產生十分重要的影響。由圖 6、7 可以看出 :在蒸發器出水溫度不變的情況下,隨著冷凝器進水溫度的上升,機組的輸入功率上升,制冷性能系數下降 ;在冷凝器進水溫度不變,蒸發器出水溫度上升時,輸入功率增大緩慢,增長幅度低于制冷量上升幅度,因此,制冷性能系數呈現逐漸增加的趨勢。

4、結論

4. 1、對于供暖期較長的內蒙古地區來說,由于中水的溫度高于同季節地表水、地下水的水溫,中水更適合作為熱泵機組的冷源。

4. 2、中水作為熱泵的冷熱源時,各種工況下熱泵機組均能在較高的性能下運行,可以達到節能減排的目的。

4. 3、該實驗研究為內蒙古地區中水源熱泵的應用提供了有價值的數據。

電子發燒友App

電子發燒友App

評論