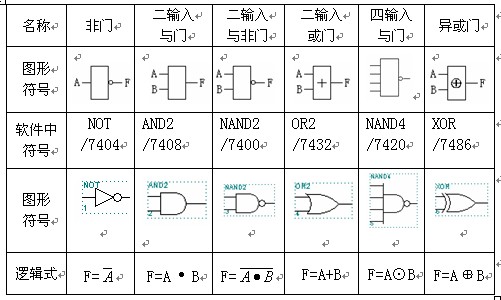

一、基本邏輯門電路

1、關于邏輯電路的幾個規定

①有關高電平,低電平的規定;

在邏輯電路中,電位的高低常用高電平,低電平來描述,單位也用“V”表示。 實際的高電平和低電平都不是一個固定的數值,因此通常規定一個電平變化范圍,如果在此范圍內,就判斷為1(或0)狀態。 例如一個供電電源為+5V的電路,高電平可在35V之間波動,低電平可在00.4之間撥動。 實際使用中,各集成邏輯門電路都規定了高電平的下限值和低電平的上限值。

②正邏輯與負邏輯

1表示高電平,0表示低電平,稱為正邏輯體系; 1表示低電平,0表示高電平,稱為負邏輯體系,一般使用正邏輯體系。

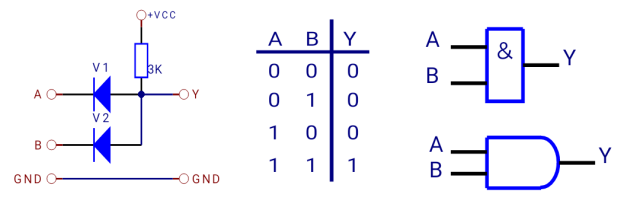

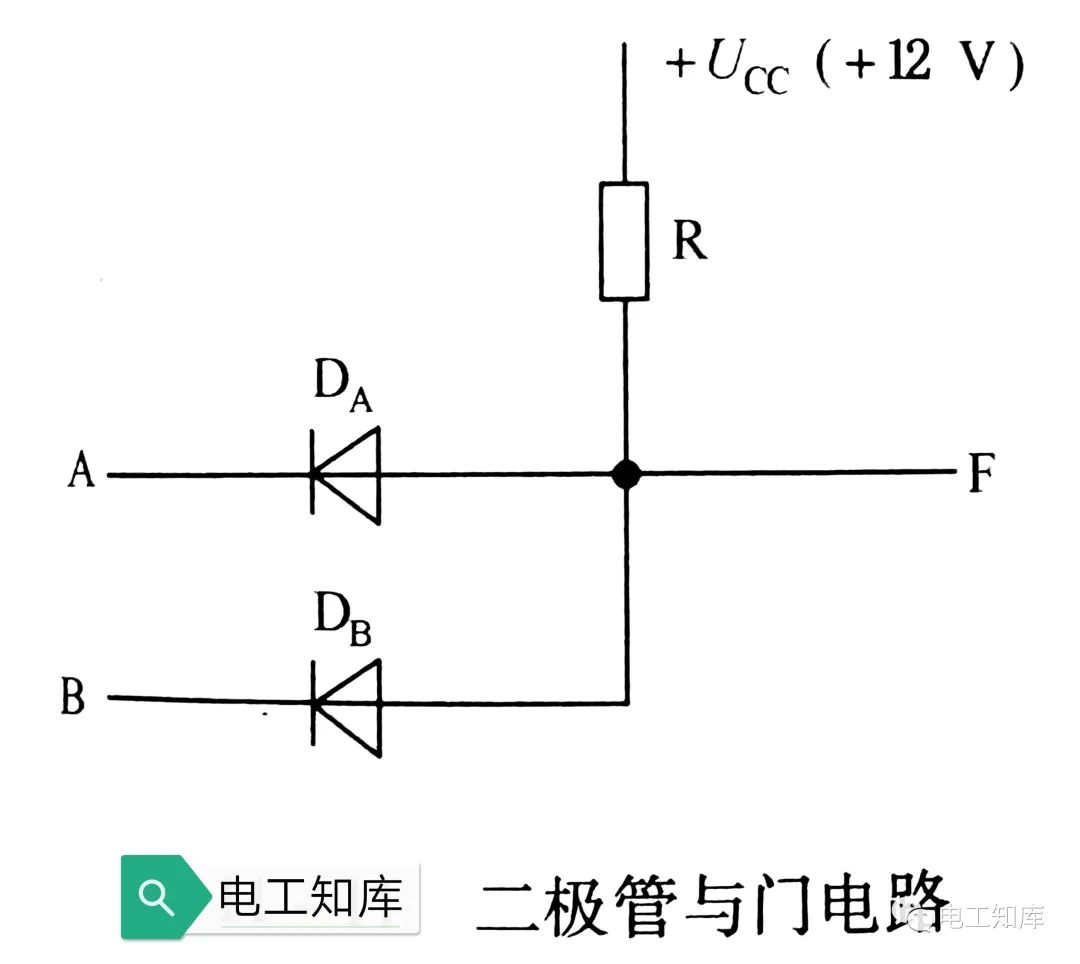

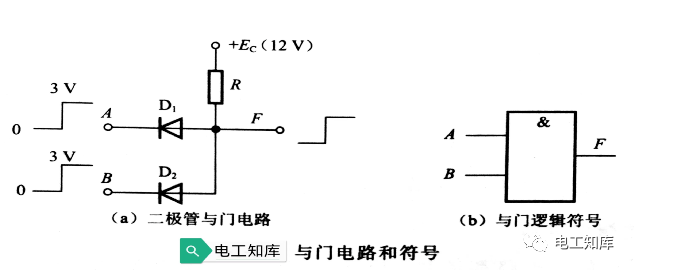

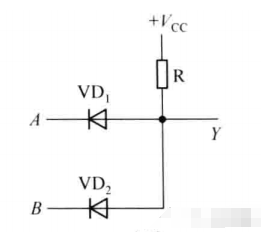

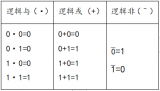

2、與門電路

①電路: ②真值表: ③邏輯符號:

④邏輯表達式:Y=A*B

⑤邏輯功能:有0出0,全1出1

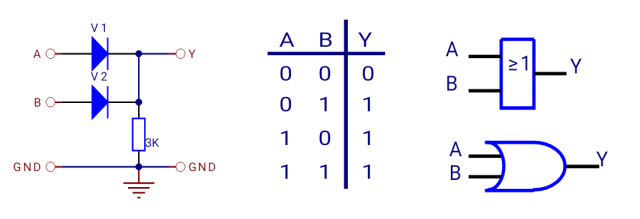

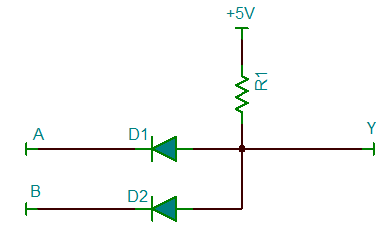

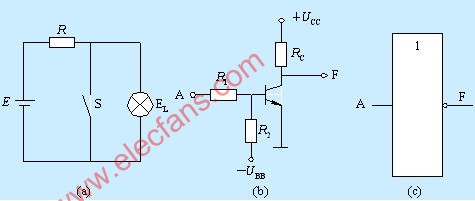

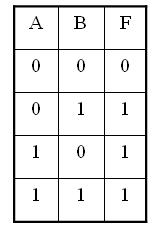

3、或門電路

①電路: ②真值表: ③邏輯符號:

④邏輯表達式:Y=A+B

⑤邏輯功能:有1出1,全0出0

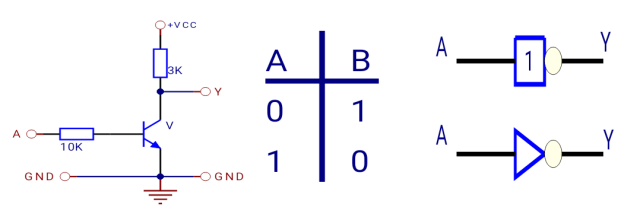

4、非門電路

①電路: ②真值表: ③邏輯符號:

④邏輯表達式:

⑤邏輯功能:有0出1,有1出0

二、組合邏輯門電路

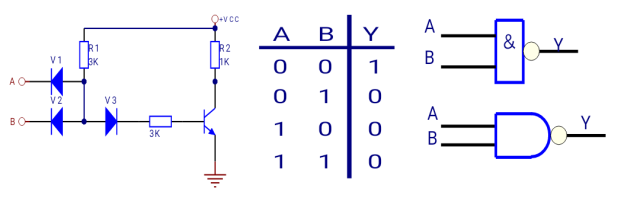

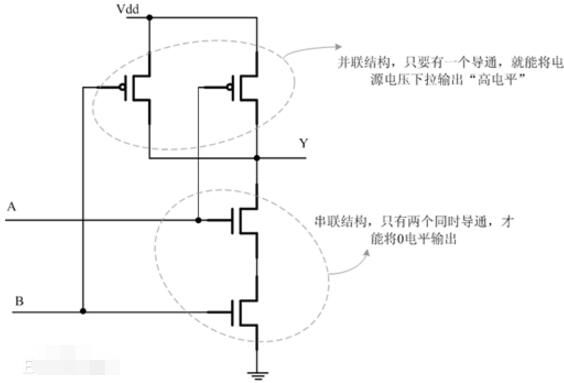

1、與非門

①電路: ②真值表: ③邏輯符號:

④邏輯表達式:Y=(A*B)

⑤邏輯功能:有0出1,全1出0

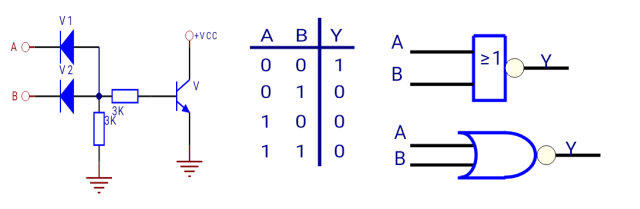

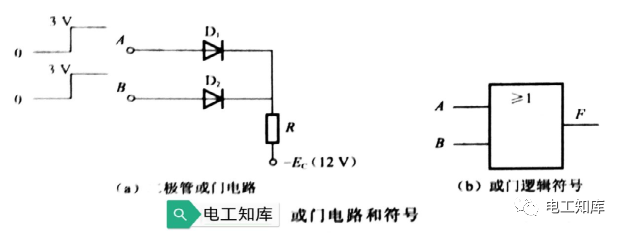

2、或非門

①電路: ②真值表: ③邏輯符號:

④邏輯表達式:(AB+CD)

⑤邏輯功能:有1出0,全0出1

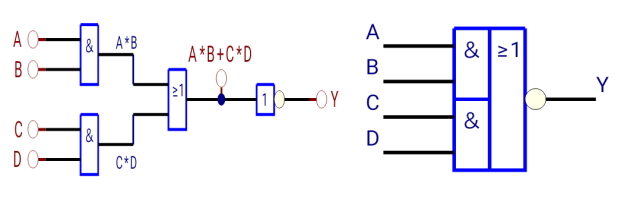

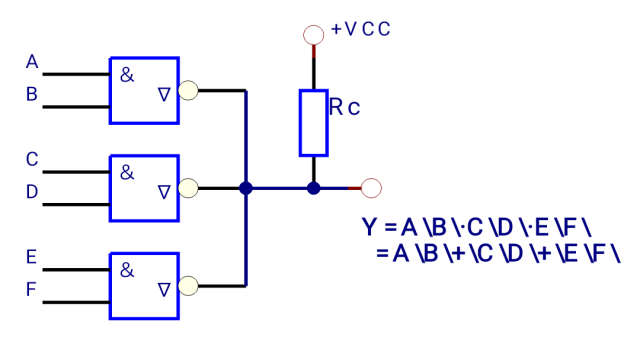

3、與或非門

①電路: ②邏輯符號:

③邏輯表達式:Y=(AB+CD)

④邏輯功能:輸入AB或CD一組全為1時,輸出為0,

輸入AB和CD各組至少有一個為0時,輸出才能為1。

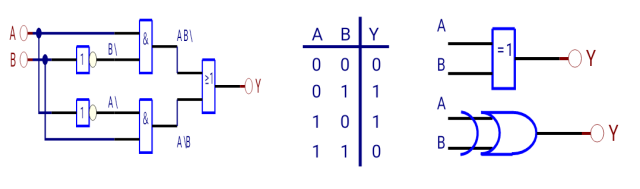

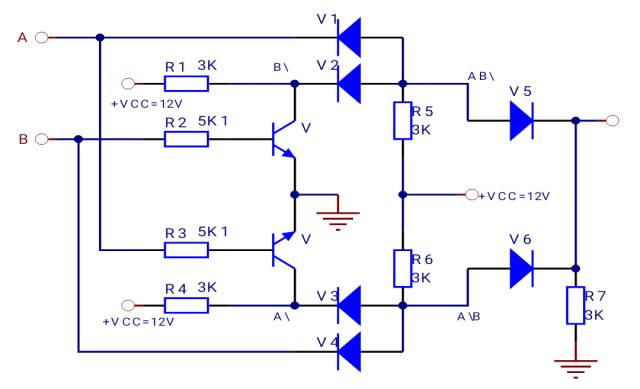

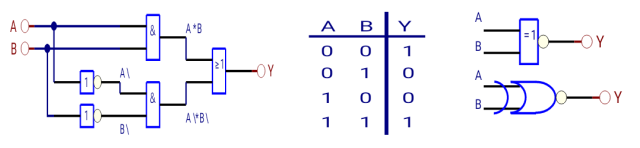

4、異或門

①電路: ②真值表: ③邏輯符號:

④邏輯表達式:Y=A*B+A*B=A⊕B

⑤邏輯功能:輸入不同出1,輸入相同出0。

⑥分立元件的電路設計

5、同或門

①電路: ②真值表: ③邏輯符號:

④邏輯表達式:Y=A*B+A*B=A⊙B

⑤邏輯功能:輸入相同出1,輸入不同出0

⑥分立元件的電路設計(仿異或門自行設計,并畫出電路圖)

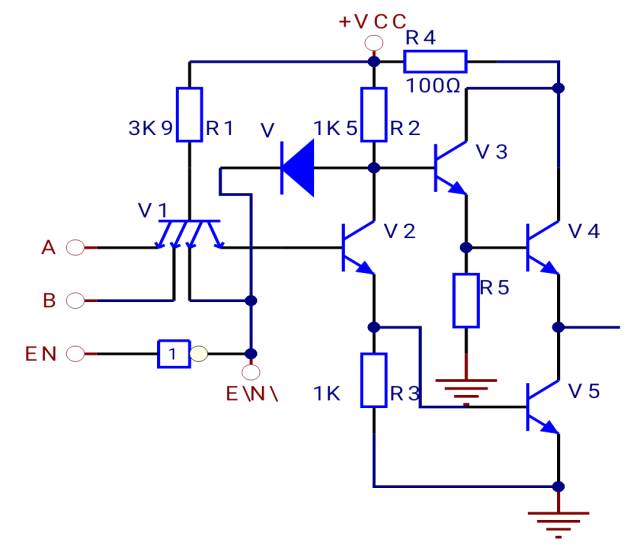

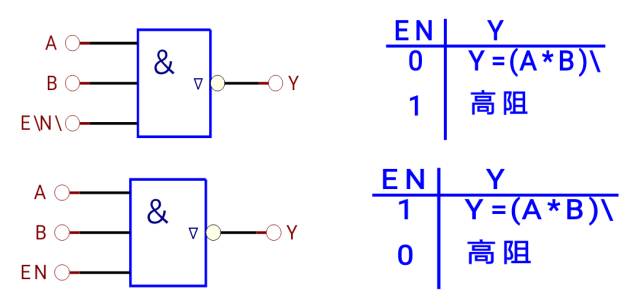

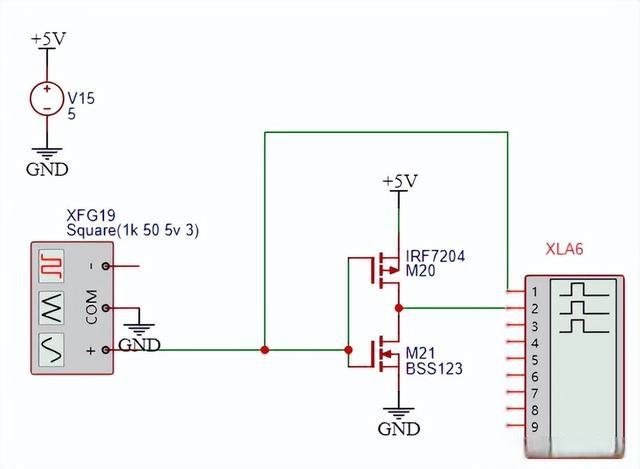

6、三態門(輸出端狀態:高電平,低電平和高阻)

三態門輸出“與非”門又稱為三態電路,三態門。 它與TTL“與非門”的不同之處是:它的輸出端除可以具有高電平和低電平兩種輸出狀態外,還能出現第三種輸出狀態——高阻輸出狀態。

如圖所示為一個三態門電路,

當EN=0,經反相器后,EN=1,此時二極管V反偏,此時的狀態由AB本身決定(Y=A*B的工作原理可自行分析)。

當EN=1時,經反相器后,EN=0,此時二極管V正向偏置,使三極管的V3基極降至低電平,導致V3、V4、V5都截止,輸出端Y呈現高阻狀態。

上述這種只用當控制端為低電平時,電路才能處于工作狀態,稱為低有效三態門,若在上圖中的EN端再加一級非門,當控制端EN為高電平時,電路處于工作狀態,稱為高有效三態門。

三態門常用于實現同一根線輪流傳送幾個不同的信號或數據,即構成總線傳送。

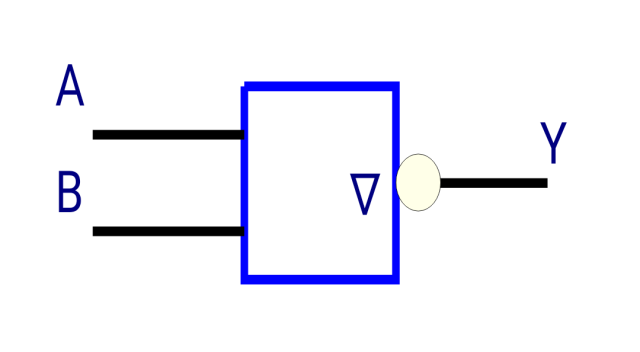

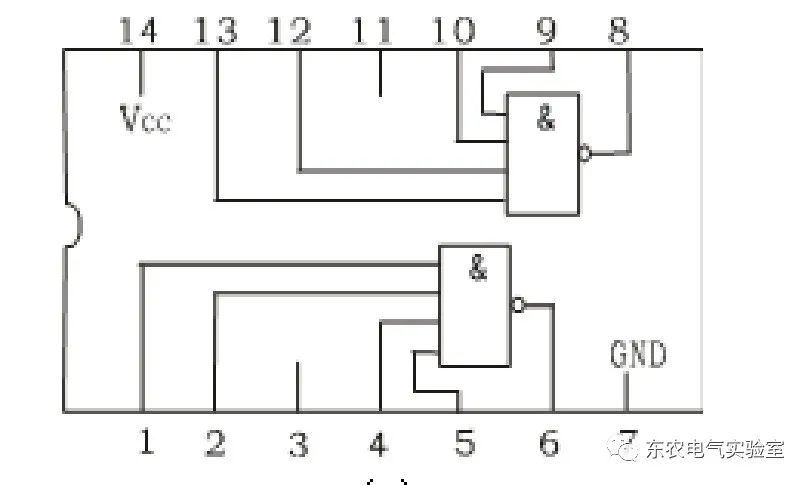

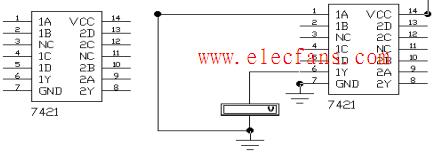

7、OC門(集電極開路與非門)

在電子計算機中廣泛使用“母線”結構,即與非門輸出

并聯使用,實踐證明普通與與非門是不允許的,為了滿足這一要求,制造廠生產出一種輸出晶體管的集電極開路的與非門電路,簡稱OC門電路,該電路使用時要外接負載電阻,其邏輯功能同一般的與非門,符號見右圖。

當所有OC門的輸入端均為1時,則Y=0,當某個OC門的輸入全為1時,而其他OC門輸入均有低電平時,由于其中一個OC門輸入均為1,則相應OC門輸出導通,而其它OC門的輸出截止。 所以輸出為低電平。 只有當各OC門輸入端均有低電平時,輸出端Y才為高電平。

三、邏輯門電路使用的幾個實際問題

1、組合邏輯門電路功能特點;

在組合邏輯門電路中,任何時刻的輸出狀態直接由當時的輸入狀態決定,輸入狀態小時,則相應的輸出狀態立即隨之小時,電路沒有記憶能力。

2、數字集成電路按照內部組成器件的種類可分為兩大類:

一類是普通三極管型數字集成電路,簡稱TTL電路; 另一類是場效應管型數字集成電路,簡稱CMOS電路。

3、數字集成電路的使用規則;

①TTL數字集成電路使用規則:

電源供電+VCC:只允許在+5V±10%范圍內,超過范圍會使邏輯功能混亂或損壞器件。

電源濾波:TTL為高速器件,在狀態切換時會在公共走線上產生壓降引起噪聲干擾,可在電源端并聯一個100UF的電容作為高頻濾波。

輸出端的連接:不允許輸出端直接接地或接+5V,除OC門和三態門,其他門電路不允許并聯使用,否則會英氣邏輯混亂或損壞器件。

輸入端的連接:輸入端可以串接1只1~10K電阻與電源或直接與電源相連獲得高電平輸入。 直接接地為低電平輸入。 TTL門電路多余輸入端不能懸空,對于或門、或非門只能接地,對于與門、與非門只能接高電平或與其他輸入端并聯使用,增加電路可靠性。

②CMOS數字集成電路使用規則

電源電壓+VDD:CMOS集成電路的電源電壓+VD范圍較寬,一般在+5V~+15V范圍內均可正常工作,并允許波動±10%,同時要求+VDD接電源正極,VSS接電源負極(接地)。

輸入端的連接:輸入端信號VI應為VSS≤VI≤VDD,超出范圍會損壞器件,多余的輸入端不允許懸空,應按照邏輯要求接+VDD或VSS,工作速度不高時允許輸入端并聯使用。

其他:測試CMOS電路時,應先加+VDD,后加輸入信號,關機時應先切斷輸入信號后斷開電源+VDD,所有儀器外殼應良好接地。

電子發燒友App

電子發燒友App

評論