LDO,英文全名是Low Dropout Regulaor,顧名思義就是低壓差線性穩(wěn)壓器,屬于線性電源。為線性的穩(wěn)壓器,僅能使用在降壓應(yīng)用中,也就是輸出電壓必需小于輸入電壓。

LDO=low dropout regulator,低壓差+線性+穩(wěn)壓器。

“低壓差”:輸出壓降比較低,例如輸入3.3V,輸出可以達(dá)到3.2V。

“線性”:LDO內(nèi)部的MOS管工作于線性電阻。

“穩(wěn)壓器”:說明了LDO的用途是用來給電源穩(wěn)壓。

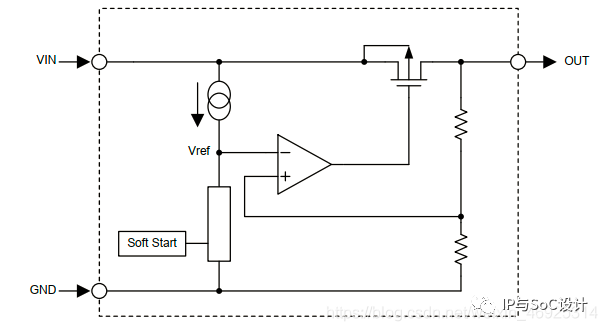

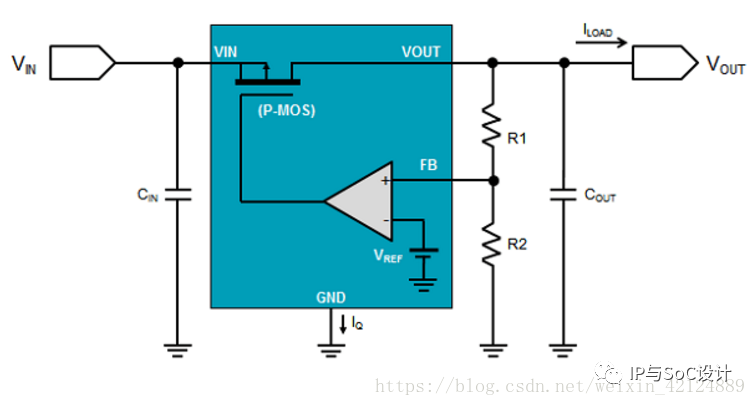

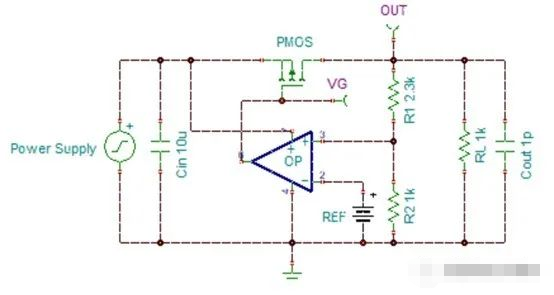

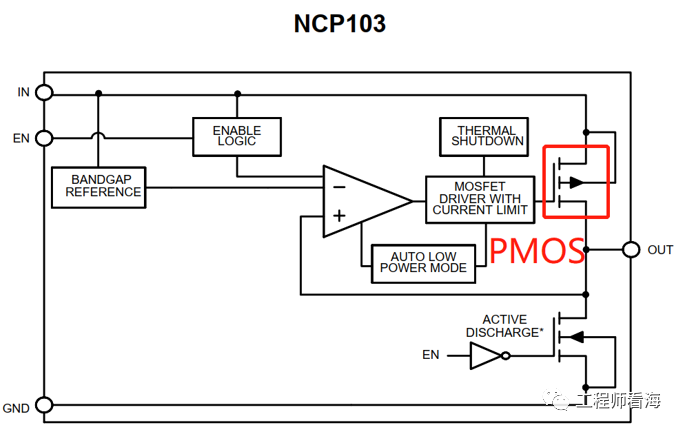

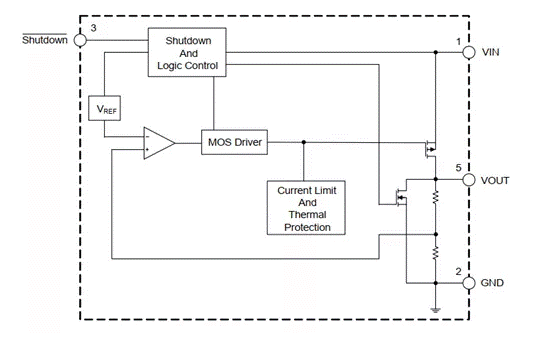

我們從上面的拓?fù)鋱D可以看出,LDO內(nèi)部主要是基準(zhǔn)參考電壓、誤差放大器、分壓取樣電路和MOS管調(diào)整電路。

LDO內(nèi)部基本都是由4大部件構(gòu)成,分別是分壓取樣電路、基準(zhǔn)電壓、誤差放大電路和晶體管調(diào)整電路。

分壓取樣電路---通過電阻R1和R2對(duì)輸出電壓進(jìn)行采集,誤差放大電路---將采集的電壓輸入到比較器反向輸入端,與正向輸入端的基準(zhǔn)電壓(也就是期望輸出的電壓)進(jìn)行比較,再將比較結(jié)果進(jìn)行放大,晶體管調(diào)整電路---把這個(gè)放大后的信號(hào)輸出到晶體管的控制極(也就是PMOS管的柵極或者PNP型三極管的基極),從而這個(gè)放大后的信號(hào)(電流)就可以控制晶體管的導(dǎo)通電壓了,這就是一個(gè)負(fù)反饋調(diào)節(jié)回路。晶體管輸出電壓就是輸入電壓減去導(dǎo)通電壓,因此控制了導(dǎo)通電壓就相當(dāng)于控制了LDO的輸出電壓了。當(dāng)輸出電壓與基準(zhǔn)電壓相差較大的時(shí)候,比較器輸出信號(hào)變強(qiáng),從而晶體管壓降變小,輸出電壓變小,從而基準(zhǔn)電壓與輸出電壓變得更加接近。

LDO的基本原理

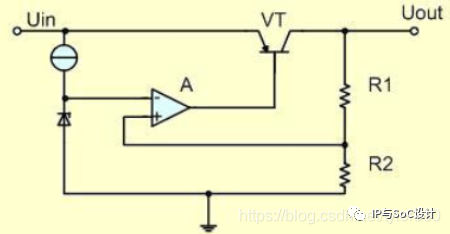

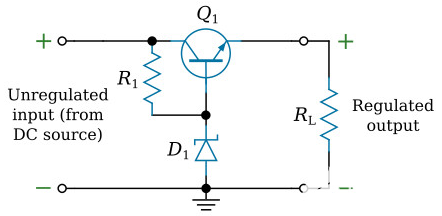

低壓差線性穩(wěn)壓器(LDO)的基本電路如下圖所示,該電路由串聯(lián)調(diào)整管VT(PNP晶體管,注:實(shí)際應(yīng)用中,此處常用的是P溝道場(chǎng)效應(yīng)管)、取樣電阻R1和R2、比較放大器A組成。

低壓差線性穩(wěn)壓器基本電路

取樣電壓Uin加在比較器A的同相輸入端,與加在反相輸入端的基準(zhǔn)電壓Uref(Uout*R2/(R1+R2))相比較,兩者的差值經(jīng)放大器A放大后. Uout=(U+ - U-)*A 注A為比較放大器的倍數(shù),)控制串聯(lián)調(diào)整管的壓降,從而穩(wěn)定輸出電壓。當(dāng)輸出電壓Uout降低時(shí),基準(zhǔn)電壓Uref與取樣電壓Uin的差值增加,比較放大器輸出的驅(qū)動(dòng)電流增加,串聯(lián)調(diào)整管壓降減小,從而使輸出電壓升高。相反,若輸出電壓Uout超過所需要的設(shè)定值,比較放大器輸出的前驅(qū)動(dòng)電流減小,從而使輸出電壓降低。供電過中,輸出電壓校正連續(xù)進(jìn)行,調(diào)整時(shí)間只受比較放大器和輸出晶體管回路反應(yīng)速度的限制。

應(yīng)當(dāng)說明,實(shí)際的線性穩(wěn)壓器還應(yīng)當(dāng)具有許多其它的功能,比如負(fù)載短路保護(hù)、過壓關(guān)斷、過熱關(guān)斷、反接保護(hù)等,而且串聯(lián)調(diào)整管也可以采用MOSFET。

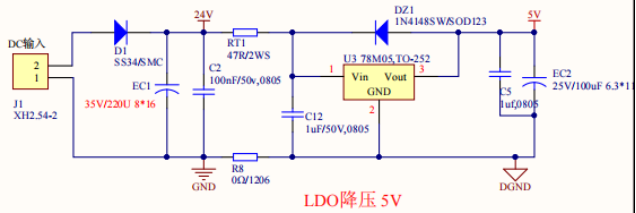

LDO的典型應(yīng)用

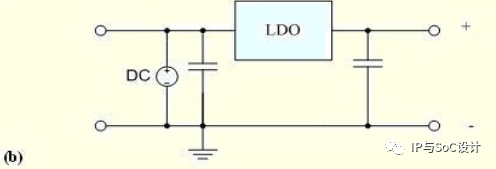

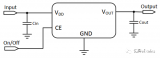

低壓差線性穩(wěn)壓器的典型應(yīng)用如下圖所示。下圖所示電路是一種最常見的AC/DC電源,交流電源電壓經(jīng)變壓器后,變換成所需要的電壓,該電壓經(jīng)整流后變?yōu)橹绷麟妷骸T谠撾娐分校蛪翰罹€性穩(wěn)壓器的作用是:在交流電源電壓或負(fù)載變化時(shí)穩(wěn)定輸出電壓,抑制紋波電壓,消除電源產(chǎn)生的交流噪聲。

各種蓄電池的工作電壓都在一定范圍內(nèi)變化。為了保證蓄電池組輸出恒定電壓,通常都應(yīng)當(dāng)在電池組輸出端接入低壓差線性穩(wěn)壓器,如下圖所示。低壓差線性穩(wěn)壓器的功率較低,因此可以延長蓄電池的使用壽命。同時(shí),由于低壓差線性穩(wěn)壓器的輸出電壓與輸入電壓接近,因此在蓄電池接近放電完畢時(shí),仍可保證輸出電壓穩(wěn)定。

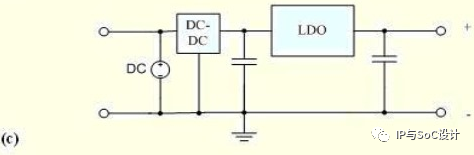

眾所周知,開關(guān)性穩(wěn)壓電源的效率很高,但輸出紋波電壓較高,噪聲較大,電壓調(diào)整率等性能也較差,特別是對(duì)模擬電路供電時(shí),將產(chǎn)生較大的影響。在開關(guān)性穩(wěn)壓器輸出端接入低壓差線性穩(wěn)壓器,如下圖所示,就可以實(shí)現(xiàn)有源濾波,而且也可大大提高輸出電壓的穩(wěn)壓精度,同時(shí)電源系統(tǒng)的效率也不會(huì)明顯降低。

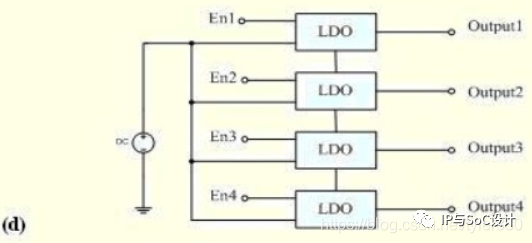

在某些應(yīng)用中,比如無線電通信設(shè)備通常只有一足電池供電,但各部分電路常常采用互相隔離的不同電壓,因此必須由多只穩(wěn)壓器供電。為了節(jié)省共電池的電量,通常設(shè)備不工作時(shí),都希望低壓差線性穩(wěn)壓器工作于睡眠狀態(tài)。為此,要求線性穩(wěn)壓器具有使能控制端。有單組蓄電池供電的多路輸出且具有通斷控制功能的供電系統(tǒng)如下圖所示。

輸出電壓計(jì)算方式在上面是有的,但是注意是換成了下面的電阻R2除以上面的電阻R1,正好和上面的DCDC典型電路相反,請(qǐng)注意兩者的區(qū)別。

注:LDO和DCDC的反饋電阻取值不同,請(qǐng)注意DCDC反饋電阻取值一般是 KΩ 級(jí)別,但是LDO的反饋電阻一般是 百Ω 級(jí)別,因?yàn)長DO對(duì)于反饋引腳電流有要求。

LDO工作原理

首先分壓取樣電路兩個(gè)電阻分壓對(duì)輸出電壓進(jìn)行采集,誤差放大電路將采集的電壓輸入到比較器反向輸入端,與正向輸入端的基準(zhǔn)電壓(也就是期望輸出的電壓)進(jìn)行比較,再將比較結(jié)果進(jìn)行放大。

MOS管調(diào)整電路把這個(gè)放大后的信號(hào)輸出到MOS管的柵極,從而這個(gè)放大后的信號(hào)(電流)就可以控制MOS管的導(dǎo)通電壓了,這就是一個(gè)負(fù)反饋調(diào)節(jié)回路。

MOS管輸出電壓就是輸入電壓減去導(dǎo)通電壓,因此控制了導(dǎo)通電壓就相當(dāng)于控制了LDO的輸出電壓了。

當(dāng)輸出電壓與基準(zhǔn)電壓相差較大的時(shí)候,比較器輸出信號(hào)變強(qiáng),從而MOS管壓降變小,輸出電壓變小,從而基準(zhǔn)電壓與輸出電壓變得更加接近。

從LDO工作原理我們可以得知,LDO只能降壓。

舉例

通過對(duì)于LDO的進(jìn)一步了解,我們知道LDO一般應(yīng)用于輸入輸出壓差小,輸出電流小的應(yīng)用場(chǎng)景,這樣才能發(fā)揮LDO的優(yōu)勢(shì),同時(shí)使用時(shí)還要重點(diǎn)注意壓降、耗散功率等參數(shù),保證電路可以按預(yù)期正常工作。

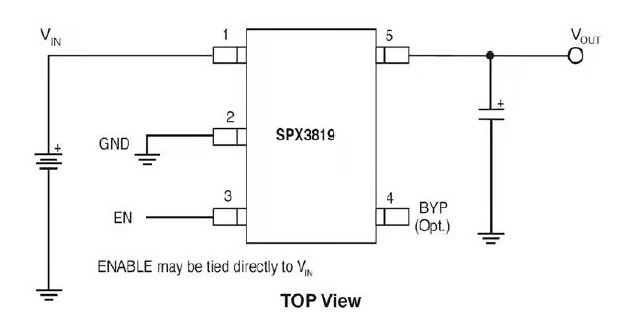

上圖中的LDO芯片,內(nèi)部為一個(gè)P-MOS+一個(gè)運(yùn)放+2個(gè)電阻

因此上圖LDO核心架構(gòu):P-MOS+運(yùn)放,通過芯片內(nèi)部已經(jīng)設(shè)置好的電阻來達(dá)到調(diào)節(jié)P-MOS的輸出,而得到該芯片的輸出電壓。

上圖中的LDO工作原理就一句話:通過運(yùn)放調(diào)節(jié)P-MOS的輸出。

LDO的特點(diǎn)

1.外圍電路簡(jiǎn)單,價(jià)格便宜

LDO在使用的時(shí)候,非常方便,除了輸入、輸出端加上濾波電容,不需要其他外圍器件,而一般的DCDC模塊在使用時(shí)要電感、電容、二極管等外圍器件組合,且布局也需要特別講究,否則使用效果不盡人意。

LDO芯片一般都比較便宜,且不需要很多外圍器件,非常適合低成本方案。

2.效率較低

使用LDO時(shí),需注意輸入電壓與輸出電壓差不能太大,否則效率會(huì)非常低。LDO效率η=(Vin-Vout)/Vin,比如輸入電壓Vin為24V,輸出電壓Vout3.3V,計(jì)算得出效率η=13.75%,效率很低。所以使用LDO時(shí),盡量控制輸入輸出電壓差。

3.噪聲低、紋波小

因?yàn)槠湓頌榫€性調(diào)節(jié)方式,所以不會(huì)產(chǎn)生開關(guān)噪聲,同時(shí)電路紋波也很小。

LDO的主要參數(shù)

1.輸出電壓(Output Voltage)

輸出電壓是低壓差線性穩(wěn)壓器最重要的參數(shù),也是電子設(shè)備設(shè)計(jì)者選用穩(wěn)壓器時(shí)首先應(yīng)考慮的參數(shù)。低壓差線性穩(wěn)壓器有固定輸出電壓和可調(diào)輸出電壓兩種類型。固定輸出電壓穩(wěn)壓器使用比較方便,而且由于輸出電壓是經(jīng)過廠家精密調(diào)整的,所以穩(wěn)壓器精度很高。但是其設(shè)定的輸出電壓數(shù)值均為常用電壓值,不可能滿足所有的應(yīng)用要求,但是外接元件數(shù)值的變化將影響穩(wěn)定精度。

2.最大輸出電流(Maximum Output Current)

用電設(shè)備的功率不同,要求穩(wěn)壓器輸出的最大電流也不相同。通常,輸出電流越大的穩(wěn)壓器成本越高。為了降低成本,在多只穩(wěn)壓器組成的供電系統(tǒng)中,應(yīng)根據(jù)各部分所需的電流值選擇適當(dāng)?shù)姆€(wěn)壓器。

3.輸入輸出電壓差(Dropout Voltage)

輸入輸出電壓差是低壓差線性穩(wěn)壓器最重要的參數(shù)。在保證輸出電壓穩(wěn)定的條件下,該電壓壓差越低,線性穩(wěn)壓器的性能就越好。比如,5.0V的低壓差線性穩(wěn)壓器,只要輸入5.5V電壓,就能使輸出電壓穩(wěn)定在5.0V。

4.接地電流(Ground Pin Current)

接地電路IGND是指串聯(lián)調(diào)整管輸出電流為零時(shí),輸入電源提供的穩(wěn)壓器工作電流。該電流有時(shí)也稱為靜態(tài)電流,但是采用PNP晶體管作串聯(lián)調(diào)整管元件時(shí),這種習(xí)慣叫法是不正確的。通常較理想的低壓差穩(wěn)壓器的接地電流很小。

5.負(fù)載調(diào)整率(Load Regulation)

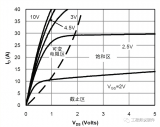

負(fù)載調(diào)整率可以通過圖2-1和式2-1來定義,LDO的負(fù)載調(diào)整率越小,說明LDO抑制負(fù)載干擾的能力越強(qiáng)。

6.線性調(diào)整率(Line Regulation)

線性調(diào)整率可以通過圖2-2和式2-2來定義,LDO的線性調(diào)整率越小,輸入電壓變化對(duì)輸出電壓影響越小,LDO的性能越好。

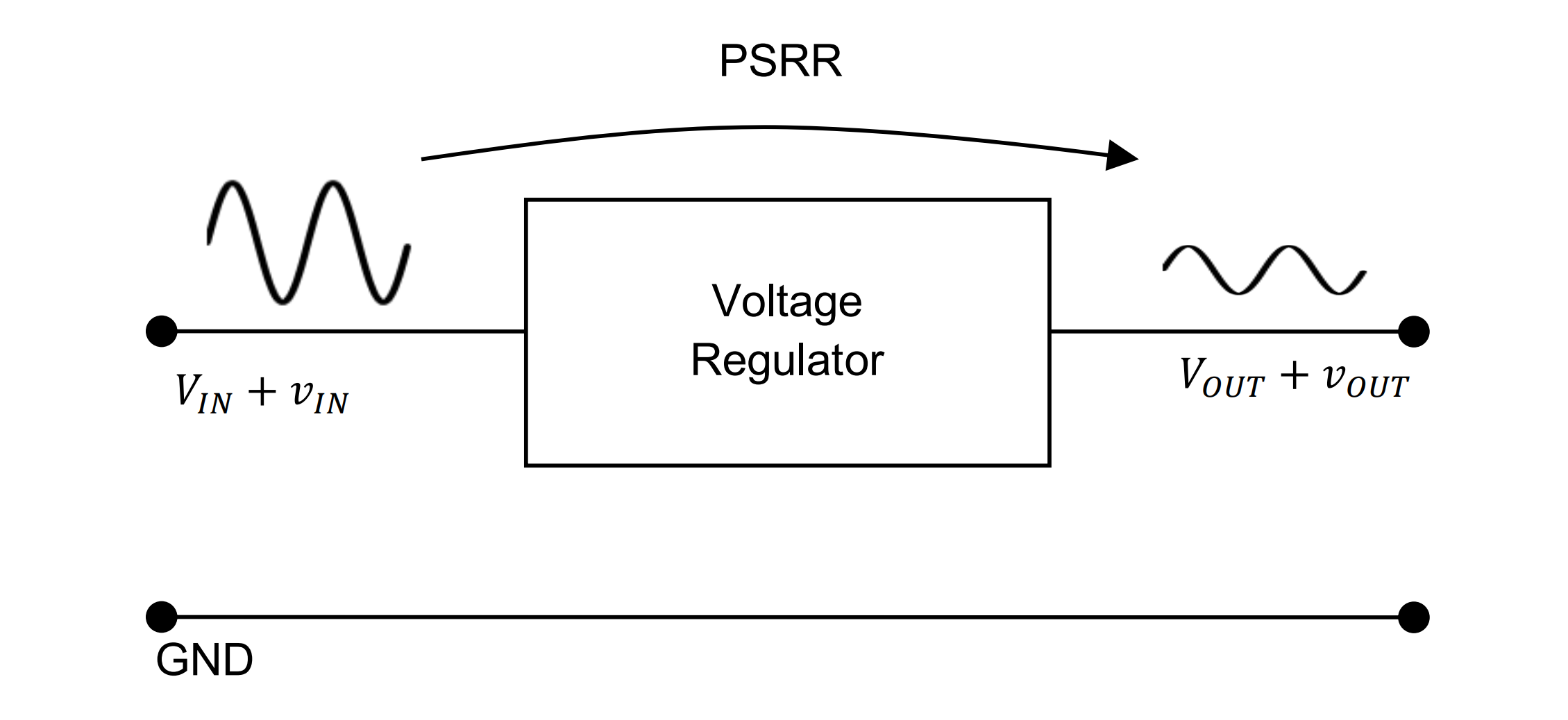

7.電源抑制比(PSSR)

LDO的輸入源往往許多干擾信號(hào)存在。PSRR反映了LDO對(duì)于這些干擾信號(hào)的抑制能力。

LDO選型需考慮的因素

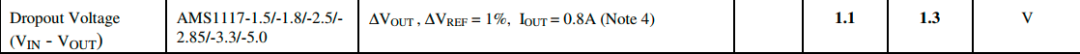

1.壓降(Dropout Voltage)

我們?cè)谶x型LDO時(shí),除了考慮輸入輸出電壓的范圍,還要考慮LDO本身存在壓降,這個(gè)是由LDO本身結(jié)構(gòu)(MOS管存在導(dǎo)通電阻)導(dǎo)致,這個(gè)參數(shù)我們很多設(shè)計(jì)人員都會(huì)忽略,最后就會(huì)導(dǎo)致電路工作不正常。比如我們常用的AMS1117-3.3,這個(gè)LDO最高可以輸入15V,輸出3.3V,假設(shè)我們的輸入電壓為4.2V,乍一看輸入電壓在手冊(cè)規(guī)定范圍內(nèi),同時(shí)也高于輸出,應(yīng)該是可以使用的。但是實(shí)際使用時(shí),卻發(fā)現(xiàn)輸出電壓沒有3.3V,大概在2.7V-2.9V左右,這就是設(shè)計(jì)時(shí)忽略的LDO本身存在的壓降。

從上圖我們看可以知道AMS1117的壓降一般1.1V,最大1.3V,因?yàn)閴航颠€和電流、溫度有關(guān)系,所以推薦輸 入電壓-輸出電壓≥1.5V,才可以保證電路穩(wěn)定。

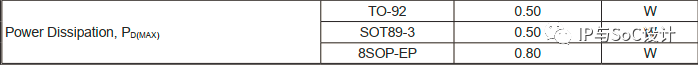

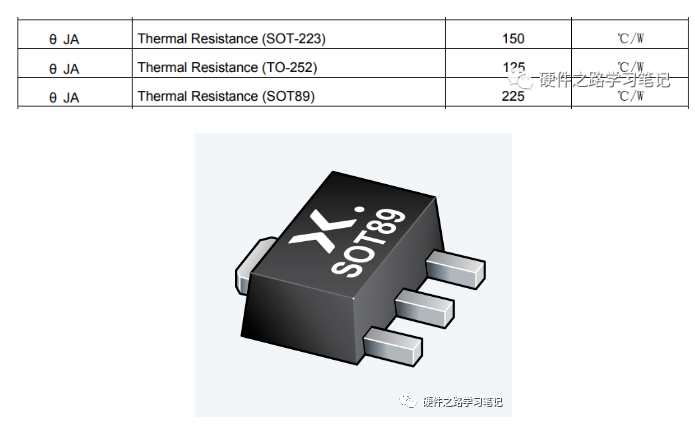

2.最大耗散功率(Power Dissipation)

LDO的耗散功率P=(Vin-Vout)*Iout,假設(shè)輸入電壓Vin24V,輸出電壓Vout3.3V,輸出電流Iout30mA,那LDO的耗散功率P=0.651W,這個(gè)功耗全部是通過熱量損耗了,所以不推薦LDO用于輸入輸出壓差過大,大輸出電流的場(chǎng)景。

如果實(shí)在需要使用的話,我們就要考慮LDO芯片能承受多大的功耗了,我們以HT7333-3為例,下圖為其不同封裝的最大耗散功率,這個(gè)最大耗散功率就是這個(gè)芯片能承受最大的熱功耗,超過就會(huì)燒壞。

我們以上面舉例的場(chǎng)景下使用HT7333-3的話,那我們就只能選用最下面的8SOP-EP封裝了,同時(shí)注意電路散熱,這樣才不至于燒壞LDO芯片。

3.輸入電壓范圍:穩(wěn)壓器輸入端可以輸入的電壓范圍。

4.輸出電壓:穩(wěn)壓器輸出端的輸出電壓值。

5.最大輸出電流:穩(wěn)壓器輸出端的最大輸出電流值。

6.線性調(diào)整率:穩(wěn)壓器輸入變化對(duì)輸出的影響,即在負(fù)載一定的情況下,輸出電壓變化量和輸入電壓變化量之比。線性調(diào)整率越小越好。

7.負(fù)載調(diào)整率:是指在給定負(fù)載變化下的輸出電壓的變化,這里的負(fù)載變化通常是從無負(fù)載到滿負(fù)載。負(fù)載調(diào)整率越小越好。

8.電源紋波抑制比(PSRR):表示穩(wěn)壓器抑制由輸入電壓造成的輸出電壓波動(dòng)的能力。線性調(diào)整率只有在直流電時(shí)才需要考慮,但是電源抑制比必須在寬頻率范圍上考慮。PSRR是一個(gè)用來描述輸出信號(hào)受電源影響的參量,PSRR越大,輸出信號(hào)受到電源的影響越小。

9.瞬態(tài)響應(yīng):表示負(fù)載電流突變時(shí)引起的輸出電壓的最大變化,它是輸出電容及其等效串聯(lián)電阻和旁路電容的函數(shù)。其中輸出電容的作用是提高負(fù)載瞬態(tài)響應(yīng)的能力,也起到了高頻旁路的作用。

10.靜態(tài)電流:又叫接地電流,是通路元件的偏流和驅(qū)動(dòng)電流的組合,通常保持盡可能低的水平。靜態(tài)電流越大,穩(wěn)壓器的效率越低。

DC/DC和LDO的區(qū)別是什么?

DC/DC簡(jiǎn)介

DC/DC 轉(zhuǎn)換器一般由控制芯片,電桿線圈,二極管,三極管,電容構(gòu)成。DC/DC轉(zhuǎn)換器為轉(zhuǎn)變輸入電壓后有效輸出固定電壓的電壓轉(zhuǎn)換器。DC/DC轉(zhuǎn)換器分為三類:升壓型DC/DC轉(zhuǎn)換器、降壓型DC/DC轉(zhuǎn)換器以及升降壓型DC/DC轉(zhuǎn)換器。根據(jù)需求可采用三類控制。PWM控制型效率高并具有良好的輸出電壓紋波和噪聲。PFM控制型即使長時(shí)間使用,尤其小負(fù)載時(shí)具有耗電小的優(yōu)點(diǎn)。PWM/PFM轉(zhuǎn)換型小負(fù)載時(shí)實(shí)行PFM控制,且在重負(fù)載時(shí)自動(dòng)轉(zhuǎn)換到PWM控制。目前DC/DC轉(zhuǎn)換器廣泛應(yīng)用于手機(jī)、MP3、數(shù)碼相機(jī)、便攜式媒體播放器等產(chǎn)品中。?

由于一般的LDO封裝都比DC/DC小的多,并且成本也低得多,因此在很多產(chǎn)所中,我們會(huì)使用到LDO來轉(zhuǎn)換我們所需要的電壓,當(dāng)然在選擇使用LDO的前提下,是需要滿足對(duì)噪聲的反應(yīng)和耗電等基本要求的。

兩者如何選用

1、輸入電壓和輸出電壓范圍。如果輸入輸出電壓差值很大,此時(shí)就應(yīng)該選擇DCDC,效率高損耗低;如果選擇LDO器件,隨著輸入輸出壓差的增加,器件的效率一直下降,由此帶來的問題就是高發(fā)熱量;

2、看預(yù)算。相同輸入輸出電壓的LDO可選擇時(shí),確認(rèn)研發(fā)以及生產(chǎn)的成本,成本如果可行的話,用便宜的,顯然LDO是不錯(cuò)的選擇;首先單芯片的價(jià)格,DCDC貴,外加濾波電容、儲(chǔ)能電感、續(xù)流二極管,這些東西可是不便宜的;

3、空間。PCB是項(xiàng)目最終需要拿出來的實(shí)物,所有的直插式、表貼式元件都是安裝在PCB板上的,如果空間足夠,看其他要求,有空間問題,LDO占用空間小于DCDC;

4、看負(fù)載規(guī)格。像CPU、GPU、內(nèi)核電壓這種,需要很大的工作電流,此時(shí)LDO已經(jīng)不滿足條件了,因?yàn)榍懊嬲f了,負(fù)載越大,損耗越多,這是兩者的工作原理決定的;

5、看負(fù)載要求。對(duì)于LDO來說,紋波小,穩(wěn)定;對(duì)于DCDC來講,紋波大;所以想WiFi、藍(lán)牙、GPS等工作需要很小的紋波時(shí),DCDC就派不上用處了,因?yàn)殡娫床▌?dòng)太大,超過IO口電壓容忍值,會(huì)導(dǎo)致后級(jí)負(fù)載對(duì)高低電平的判斷失誤;

6、看輸出電壓規(guī)格。如果在一個(gè)應(yīng)用中,需要輸出多路電源,電源值高于VCC和低于VCC,此時(shí)就需要DCDC了,應(yīng)為DCDC可以利用電感升壓,利用電感降壓,可以同時(shí)滿足需求;

7、看應(yīng)用環(huán)境。電子電路工作的環(huán)境不一致,會(huì)導(dǎo)致芯片的表現(xiàn)差異巨大,壽命也會(huì)大大縮短,比如濕度、溫度等,而產(chǎn)品種類不一致,器件廠商不一致,則產(chǎn)品的使用環(huán)境是不一致的,這個(gè)需要看需求看電源手冊(cè)決定。

LDO分類:PMOS與NMOS

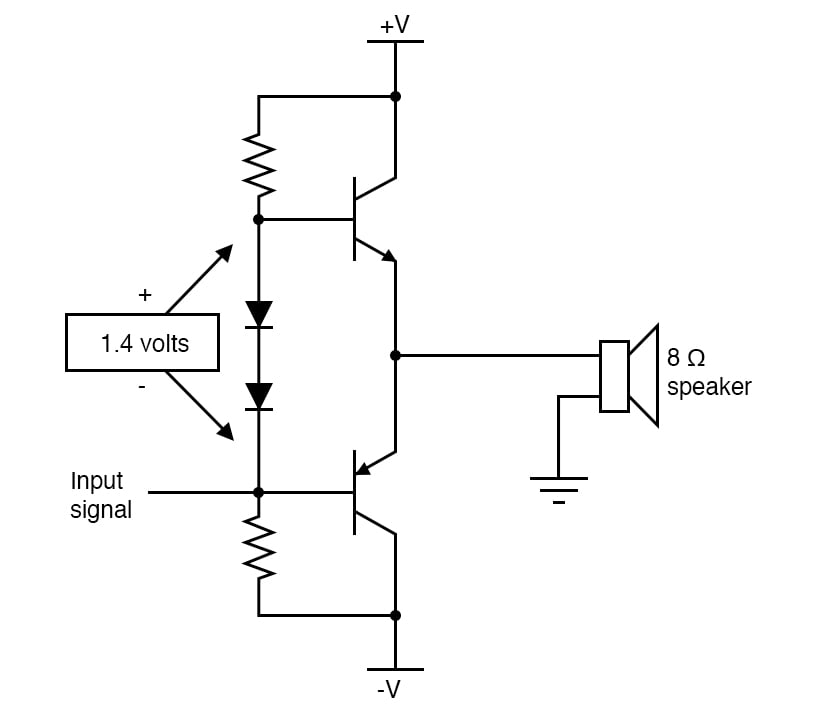

常見的LDO是由P管構(gòu)成的,由于LDO效率比較低,因此一般不會(huì)走大電流。針對(duì)某些大電流低壓差需求的場(chǎng)合,NMOS LDO應(yīng)運(yùn)而生。下圖是PMOS和NMOS LDO的系統(tǒng)框圖對(duì)比。

此圖為PMOS

此圖為NMOS

下面是一個(gè)PMOS LDO最基本結(jié)構(gòu)框圖。我們可以看到LDO主要由PMOS、運(yùn)放、反饋電阻和基準(zhǔn)參考電壓構(gòu)成。LDO主要工作流程是將輸出電壓通過分壓電阻分壓,Va和基準(zhǔn)參考電壓做比較,通過運(yùn)放輸出Vg來調(diào)節(jié)輸出,反饋回路已用紅色軌跡標(biāo)識(shí)出。

下圖是一個(gè)NMOS LDO的基本框圖,NMOS LDO一般也工作在飽和區(qū)(特殊時(shí)會(huì)在可變電阻區(qū)),所以Vg要大于Vs,因此NMOS LDO除了有Vin引腳,一般還會(huì)有個(gè)Vbias引腳來給MOS G極提供高壓驅(qū)動(dòng)源;或者只有一個(gè)Vin,而內(nèi)部集成了CHARGE BUMP來為G極提供高壓驅(qū)動(dòng)源。大體工作流程同PMOS LDO:當(dāng)Vout下降時(shí),反饋回路中的Vfb也會(huì)下降,誤差放大器輸出端Vg就會(huì)增加,隨著Vg增加,Ids電流也增加,最終使得Vout又恢復(fù)到指定電平,狀態(tài)如下:

Vout↓——>Vfb↓——>Vg↑——Iout↑——>Vout↑

Vidatronic、Archband等公司提供優(yōu)質(zhì)的DC/DC IP產(chǎn)品。

部分產(chǎn)品展示

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論