T線圈在集成電路設計中有著非常重要的地位,尤其是高速電路設計的I/O單元、寬帶匹配等電路中有廣泛應用。本文翻譯拉扎維發表在《A Circuit for All Seasons》雜志上關于T線圈的文章,非常具有參考價值。

The Bridged T-Coil

橋T線圈

By Behzad Razavi(拉扎維)

橋T線圈(The bridged T-coil),通常稱為T線圈(T-coil),是一種電路拓撲結構,其帶寬擴展性能要大于電感峰化(inductive peaking)。如今的許多高速放大器(high-speed amplifier)、線路驅動器(line driver)以及輸入/輸出接口(input/output interfaces, I/O)在應對寄生電容時都會在芯片上整合T線圈。在這篇文章中,我們將介紹和分析其基本結構,并研究其應用。

簡短歷史

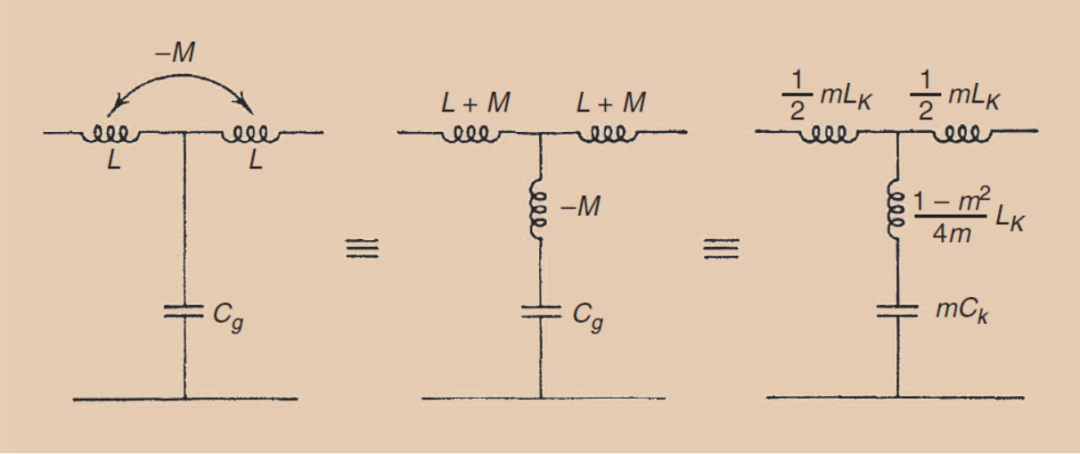

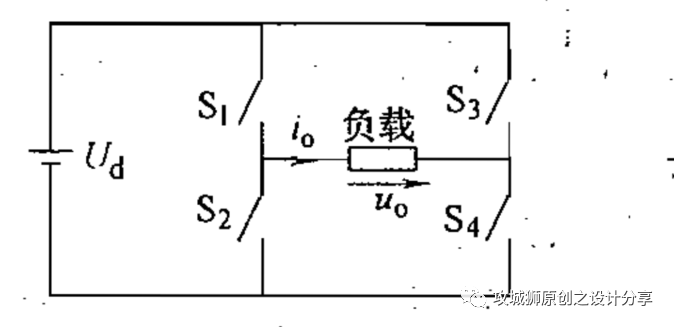

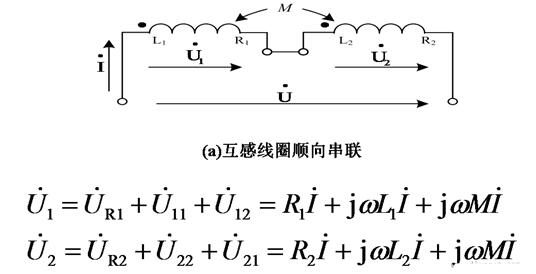

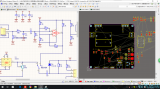

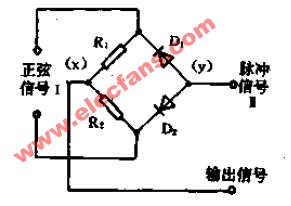

線圈電路可以追溯到1948年Ginzton等人對分布式放大器的經典論文。作者們將這個結構稱為"橋T連接",并將其與等效電路一起呈現,如圖1所示。

圖1:1948年由Ginzton等人描述的橋T線圈電路。

T線圈在帶寬增強方面的應用始于1960年代末的Tektronix工程師。他們需要為示波器(oscilloscope)的前端(front end)設計快速的"垂直"放大器,這促使他們創新了許多寬帶電路技術,并且Tektronix的設計師們看到了T線圈的顯著優勢。儀器制造商對T線圈電路的設計細節保密了很多年。直到1990年,前Tektronix工程師Dennis Feucht在他的書中公開了T線圈的設計方程。

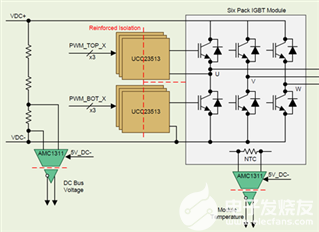

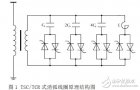

早期的T線圈實現主要基于分立的、非片上的電感或變壓器,但會受到電路板寄生效應、鍵合線電感,以及與其他信號之間的不期望的耦合的影響。1980年代末和1990年代初出現了一些GaAs工藝集成電路的實現。隨著1990年代射頻電路的革命和對集成電感的巨大工作,T線圈必然也會找到其在CMOS芯片上的位置。當然,芯片結構的有限Q值和寄生電容會帶來新的問題。此外,還需要在兩個螺旋電感之間創建一個明確的耦合因子。2003年,有兩篇論文描述了集成T線圈的設計以及它們在寬帶驅動器(broadband driver)和靜電放電保護電路(ESD protection)中的應用。

基本思想

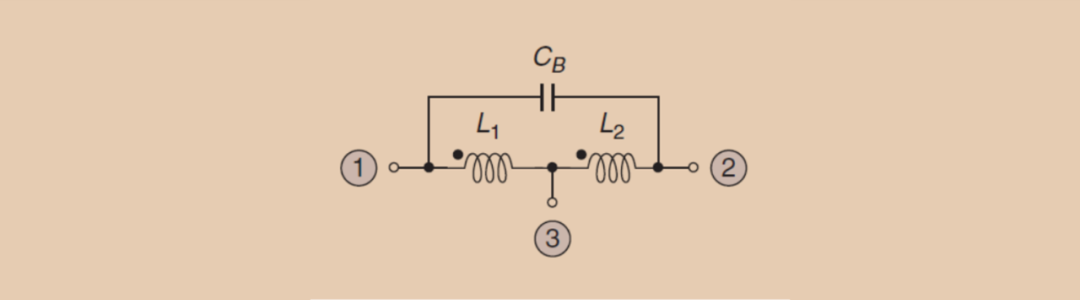

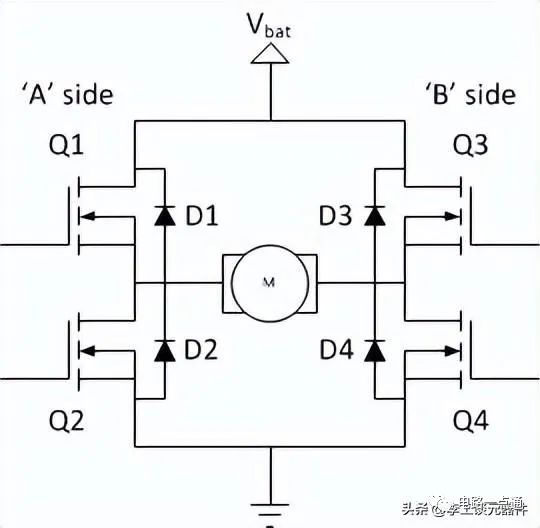

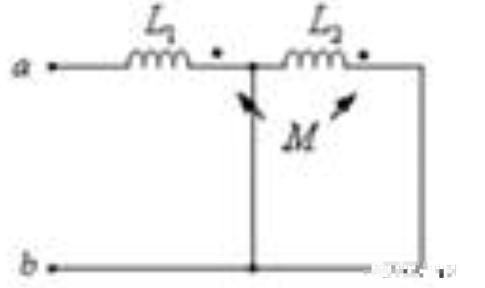

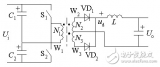

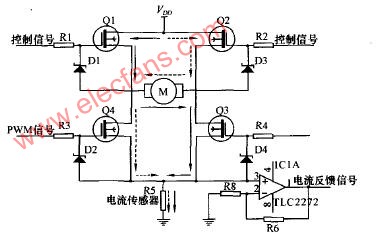

橋T線圈是雙端橋T網絡的一種特例。它由兩個相互耦合的電感和一個橋接電容組成(如圖2)。耦合極性很重要,而這兩個電感值通常選擇是相等的。當某些負載連接到這個電路時,節點1或2處看到的阻抗以及從這些節點到節點3的傳輸函數會呈現出一些有趣的特性。

圖2:基本的橋T線圈結構

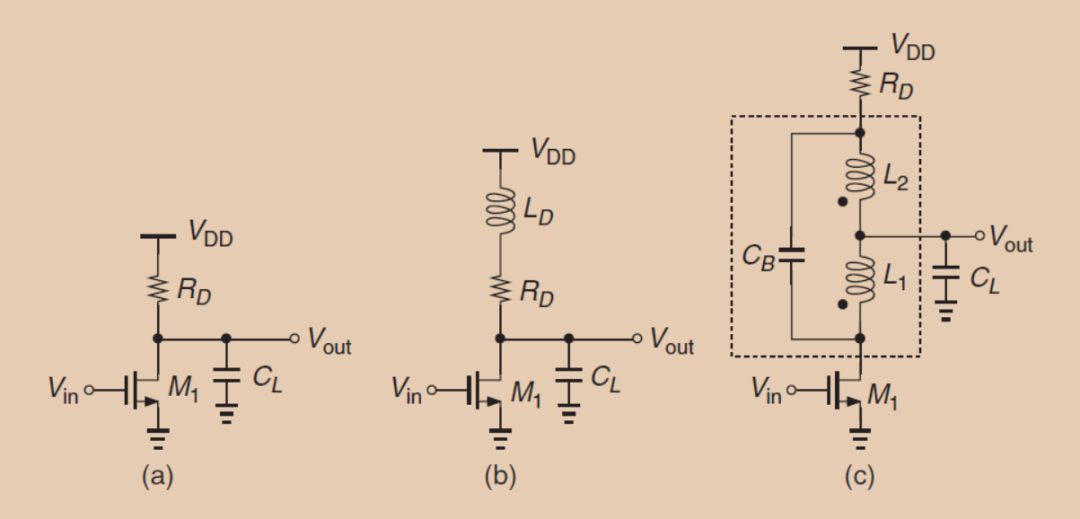

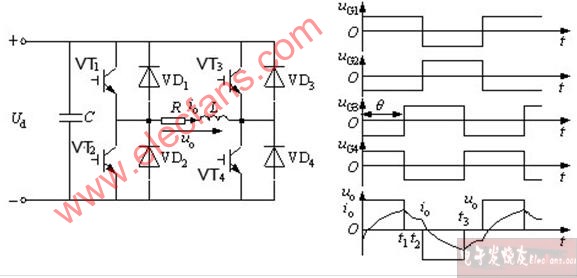

例如,考慮圖3(a)中顯示的簡單共源級,其具有負載電容的電路。在高頻時,的小信號漏電流會被分流,導致下降。我們可以將一個電感并聯在上[圖3(b)],使和的串聯阻抗隨頻率增加,從而強迫更多的電流通過,從而減少總增益的下降。或者,我們可以在信號路徑中插入一個T線圈電路,如圖3(c)所示。我們關心的是傳輸函數及其作為組件值函數的行為。

圖3:共源級與(a)簡單的電阻負載,(b)電感峰化(inductive peaking)和(c)T線圈峰化(T-coil peaking)

傳輸函數可以使用額外元定理(Extra Element Theorem,EET)或變換得出,具體如下:

其中,

這里,表示圖3(c)中顯示的和之間的互感。這個傳輸函數沒有提供太多的直觀感受,但是其中的一個特例在數學和實際應用上都更易處理。我們假設,并選擇這樣的值,使得公式(1)中的零點被兩個極點抵消。如文獻中所示,如果滿足以下兩個條件,這就可以實現,

其中是耦合系數,等于,并且

得到的二階傳輸函數形式如下

其中

對于設計目的,我們選擇阻尼因子的值,并希望確定其他電路參數。解上述方程,由文獻得出,

這些結果與文獻中的結果一致。值得注意的是,隨增加,即更緊密的耦合對應更有阻尼的響應。

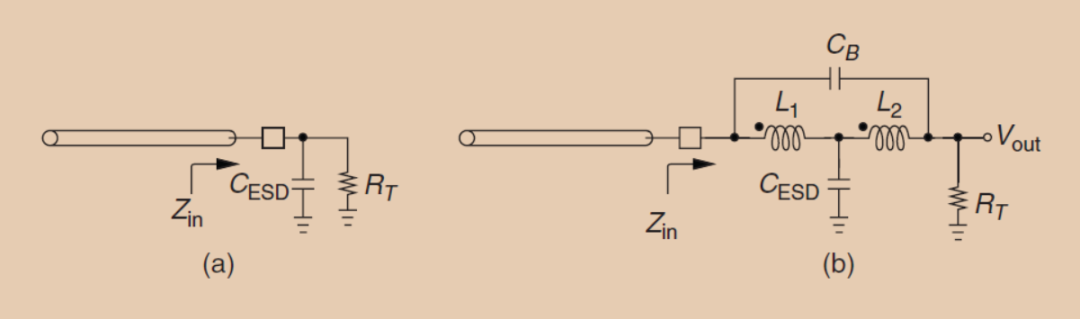

FICURE 4: (a) An input network with an ESD device and (b) an input network using a T-coil for broadband matching.圖4:(a)帶有ESD器件的輸入網絡和(b)使用T線圈進行寬帶匹配的輸入網絡。

帶寬優勢

如上所述,橋T線圈比電感峰化更大程度地提高了速度。我們通過考慮兩種情況下的3dB帶寬來闡述這種優勢。從(10)中,T線圈的帶寬表達為:

我們用公式(14)替換,用公式(13)替換,得到:

例如,如果,那么。值得注意的是,T線圈將原始帶寬乘以了2.83的因子。相比之下,圖3(b)的電感峰化階段對于的帶寬大約是。(更準確的比較應該同時考慮到時域過沖。)

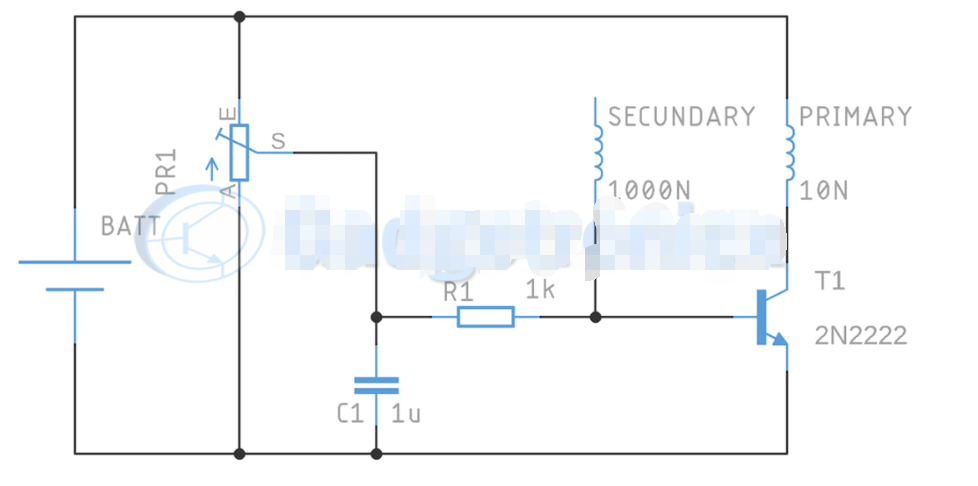

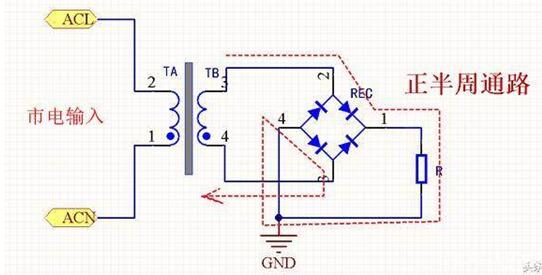

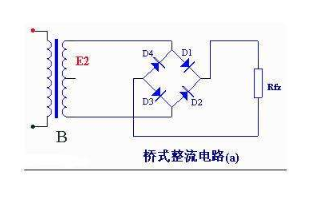

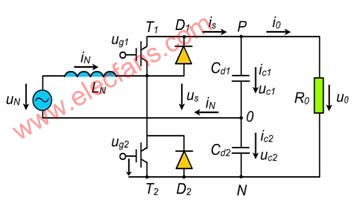

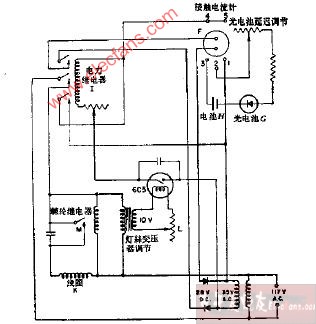

ESD保護

除了擴大帶寬,T線圈在存在重負載電容的情況下也可以創建一個固定、阻性的輸入阻抗,這是在ESD保護電路中常見的情況。例如,在圖4(a)所示的輸入網絡中,其中是終端電阻,ESD器件電容會惡化輸入匹配特性,從而導致反射。另一方面,如果按如圖4(b)所示插入一個橋T線圈,可以在所有頻率下都等于?。我們可以在兩個極端直觀地感受到這個特性:在非常低的頻率下,和將短接到輸入端,在高頻時,做同樣的事情。可以證明,如果,并且滿足公式(10)的極-零抵消的條件也成立,則在所有頻率下。換句話說,公式(13)-(15)所規定的條件在這里也同樣適用。

直觀的說明也可以解釋為什么在這種情況下T線圈不能有零點。如果電路確實包含一個零點,那么在零點頻率處,必須仍然需要等于終端阻抗。現在假設我們用的形式驅動圖3(c)的電路,得到。因此,可以去掉。換句話說,對于,漏端電荷減少到了并聯和的組合。這種組合在時不能有零阻抗,因此。

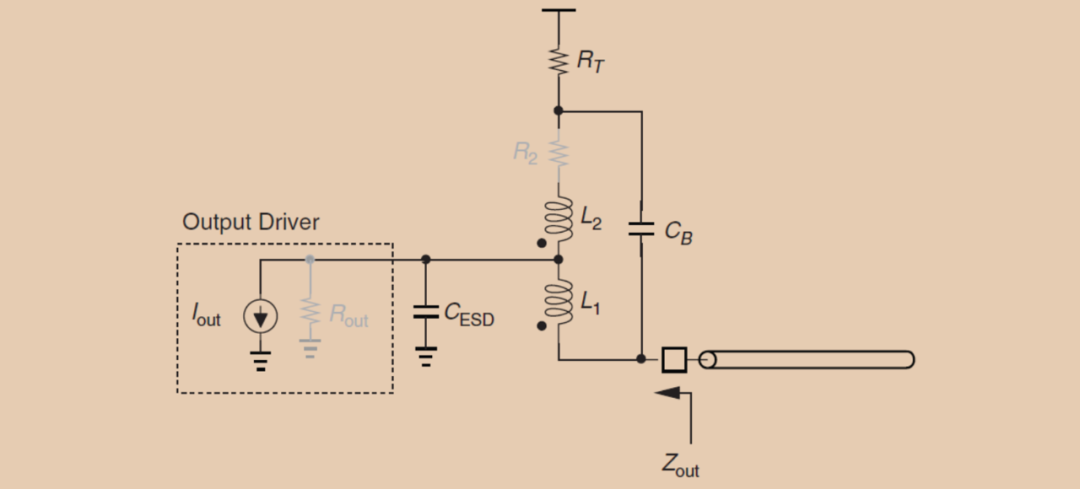

使用ESD保護的輸出驅動器也可以類似地從T線圈中受益。如圖5所示,這種設計假設驅動級的輸出阻抗為無窮大,并向外界呈現等于的阻抗。如果輸出阻抗,不夠高,可以將一個小阻抗串聯在上來補償其效果。這個阻抗由給出。

T線圈的實現

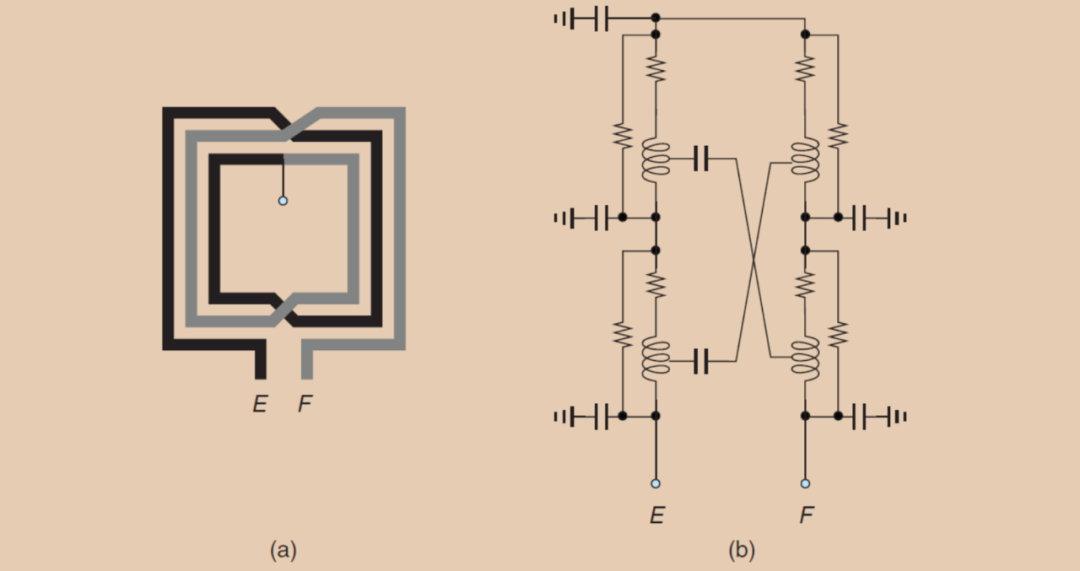

在這種特殊情況下,電感可以采用對稱螺旋的形式簡單地實現[圖6(a)]?。在這里,線間距被選擇來調整所需的互感,外部尺寸和圈數提供所需的電感。為了在仿真中包含螺旋線的寄生電阻和電容,可以構造一個分布的模型,如圖6(b)所示。注意,也考慮到了線圈間電容。作為一階近似,這個電容出現在和之間,并可以從橋電容中減去。

圖5:使用T線圈的輸出驅動

圖6:(a)T線圈的實現和(b)用于電路仿真的分布模型

與其他技術的結合

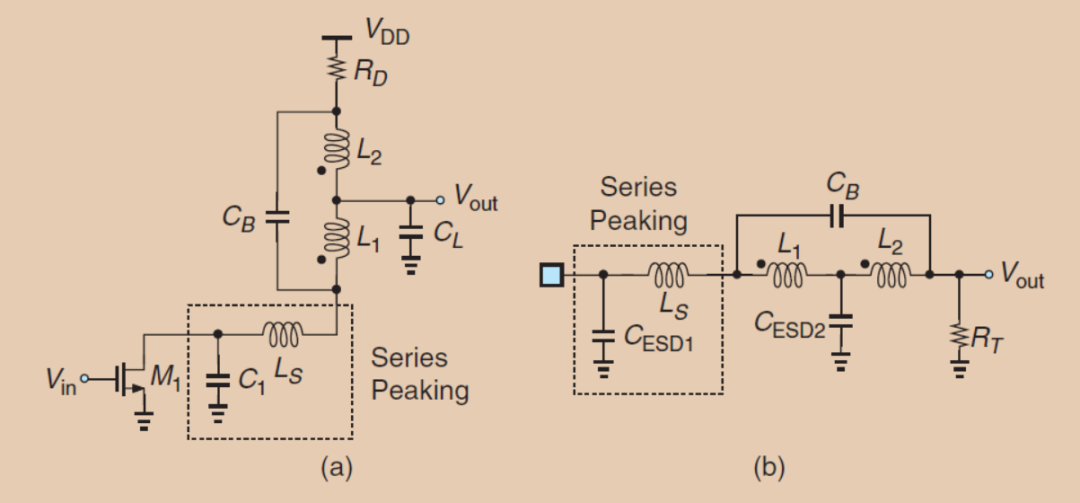

橋T線圈網絡可以與其他高速拓撲結合,以實現更大的帶寬。例如,由于二階T線圈電路的輸入阻抗是恒定的,人們可以在輸入信號路徑中直接添加串聯峰化。如圖7所示,這種組合在兩種情況下都很有用:1)如果一級包含一個大的晶體管[圖7(a)],會遭受高輸出電容;2)如果一個輸入網絡必須容納一個大的ESD電容[圖7(b)],在這種情況下,兩個電容器都可以代表ESD器件。串聯峰化也可以應用到如圖5所示的輸出網絡。

圖7:在(a)具有高輸出電容的增益級和(b)具有高ESD電容的輸入網絡中,串聯峰化和T線圈的使用。

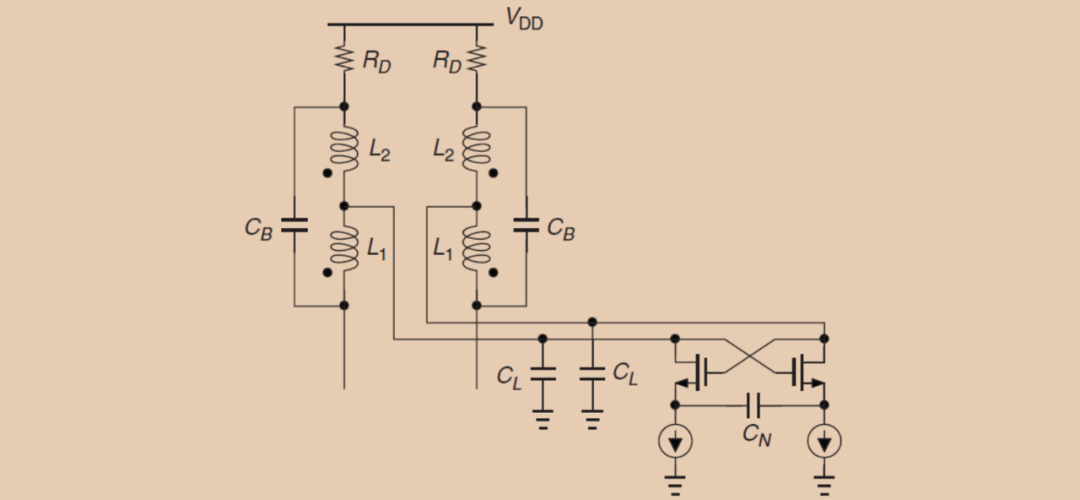

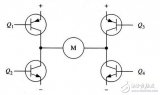

差分電路可以將T線圈與其他差分技術結合。例如,如圖8所示,可以添加一個使用交叉耦合對的負電容發生器并聯于負載電容,從而提高整體速度。為了避免在時間響應中產生大的過沖,我們選擇。

圖8:在T線圈中增加負電容發生器。

給讀者的問題

使用功率損耗論證來確定圖4(b)中電路的傳輸函數。

在圖7(a)中,如果串聯峰化網絡的阻尼因子必須保持在附近,那么應該如何選擇?

電子發燒友App

電子發燒友App

評論