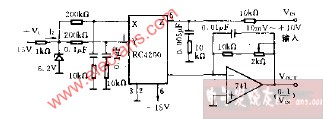

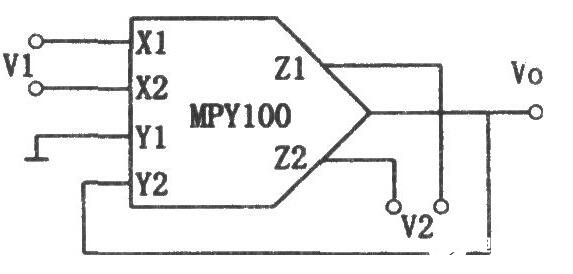

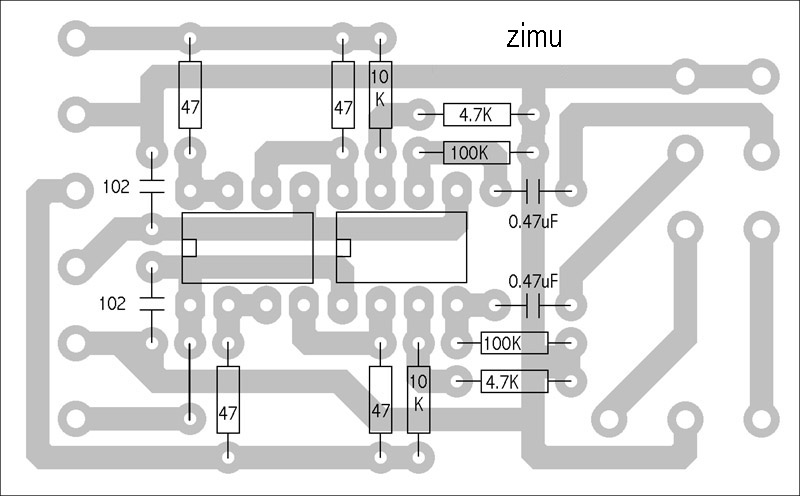

除法運算電路圖

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)>電子技術(shù)應(yīng)用>電路原理圖>放大電路圖>運算放大器電路>除法運算電路圖

相關(guān)推薦

924

924

5168

5168 15859

15859

5141

5141 3961

3961 46006

46006

0

0 5

5 5

5 10528

10528

1416

1416

2366

2366

1172

1172

11412

11412 14405

14405 1240

1240

評論