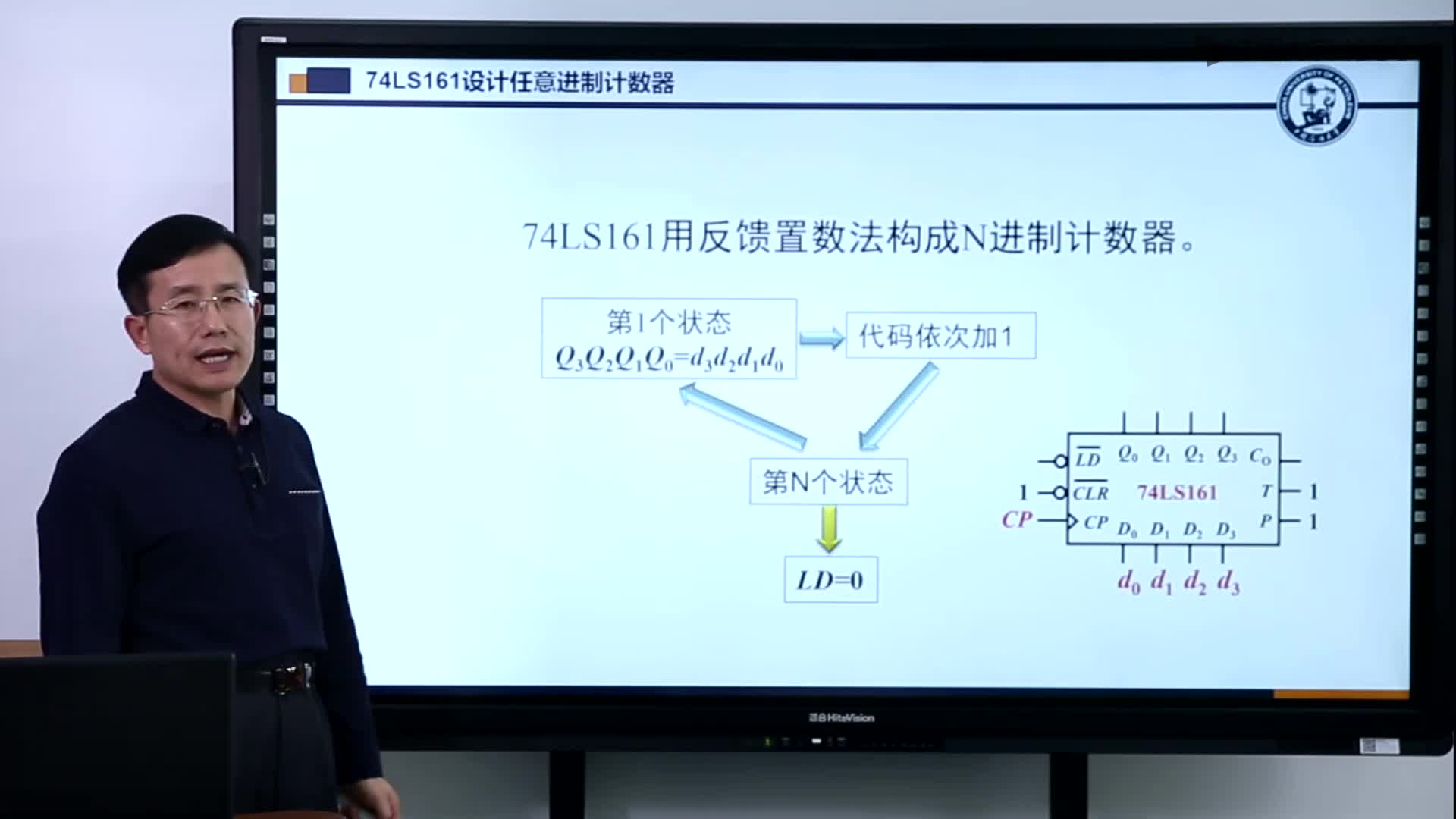

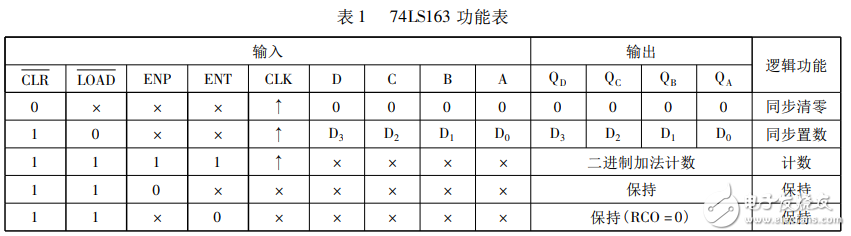

74LS161功能介紹

74LS161是4位二進制同步計數器,該計數器能同步并行預置數據,具有清零置數,計數和保持功能,具有進位輸出端,可以串接計數器使用。

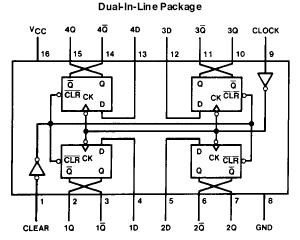

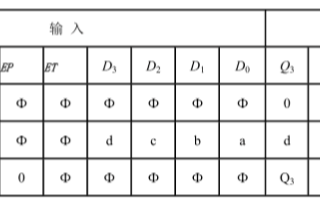

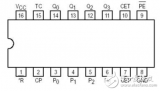

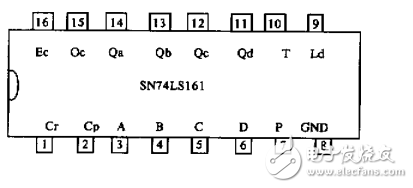

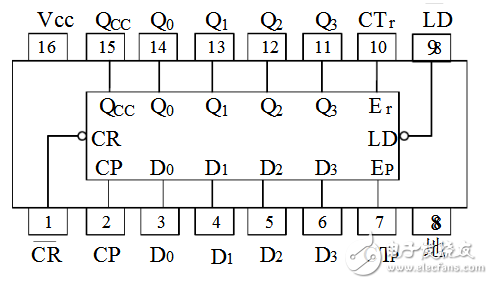

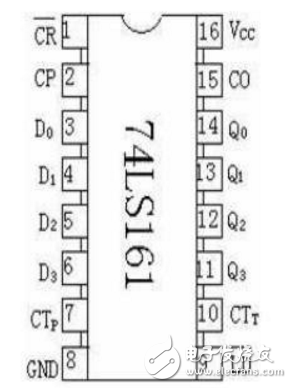

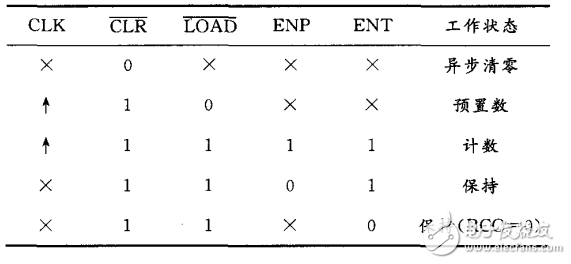

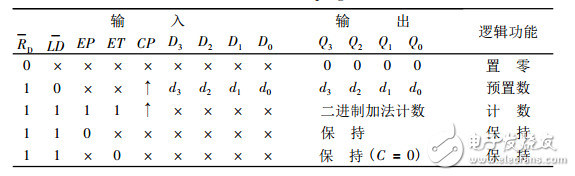

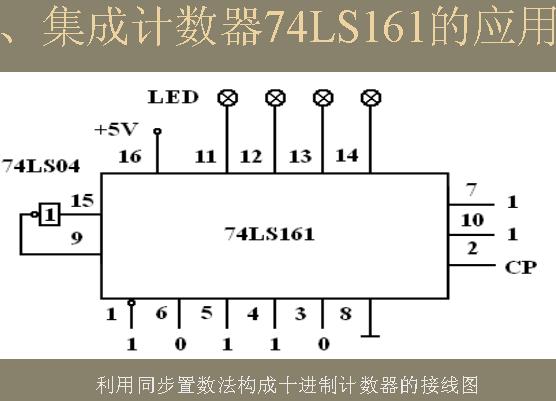

74LS161的引腳排列和邏輯功能如圖1所示。各引出端的邏輯功能如下。1腳為清零端/RD,低電平有效。2腳為時鐘脈沖輸入端CP,上升沿有效(CP↑)。3~6腳為數據輸入端A0~A3,可預置任意四位二進制數。7腳和10腳分別為計數控制端EP和ET,當其中有一腳為低電平時計數器保持狀態不變,當均為高電平時為計數狀態。9腳為同步并行置數控制端/LD,低電平有效。11~14腳為數據輸出端QQ30~。15腳為進位輸出端RCO,高電平有效。74LS161可編程度數器的真值表如下。

表 ?74LS161可編程度數器的真值表

一、74LS161集成計數器電路(十進制計數器)

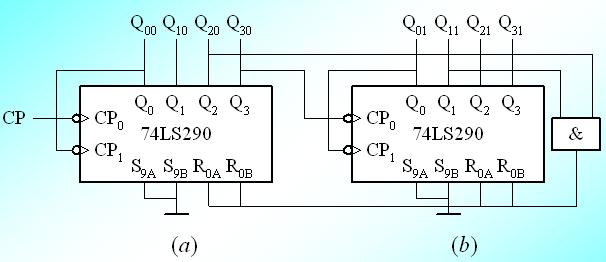

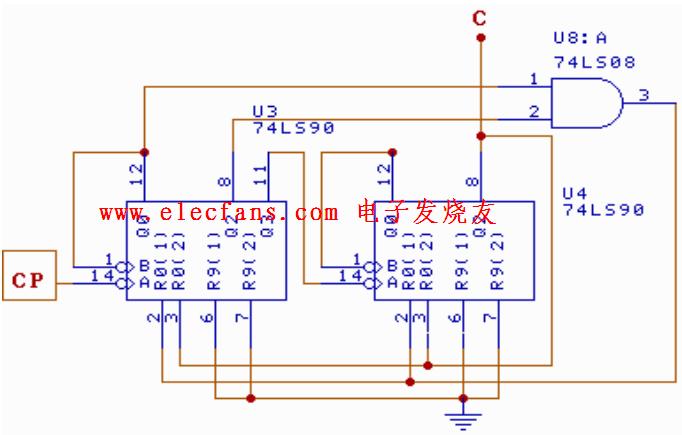

單片161可以實現16以內任意進制的加法計數功能。實現途徑有清零法和置數法兩種。以實現十進制加法計數器為例:

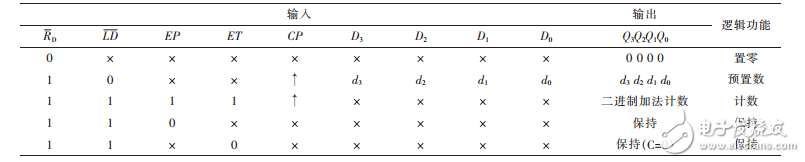

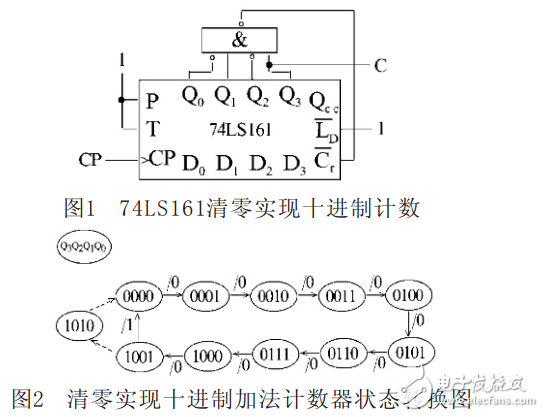

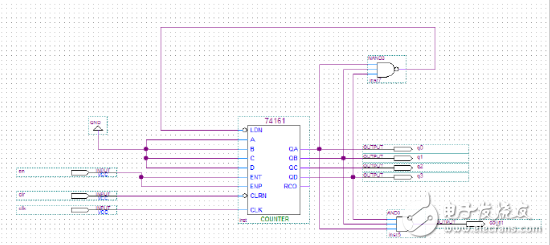

1)161的是異步清零端。當Q3Q2Q1Q0=1010(即10)狀態時,通過譯碼電路給出低電平信號,將計數器清零回到0000狀態。電路圖和狀態轉換圖如圖1,圖2所示。

由于置零信號隨著計數器被置零而立即消失,所以置零信號持續時間極短,可能觸發器還未來得及復位,置零信號已經消失,導致電路的誤動作。因此,這種電路的可靠性不高。為了克服這個缺點,時常在譯碼電路和之間加一個SR鎖存器,延長置零信號的寬度,從而增加電路的可靠性。

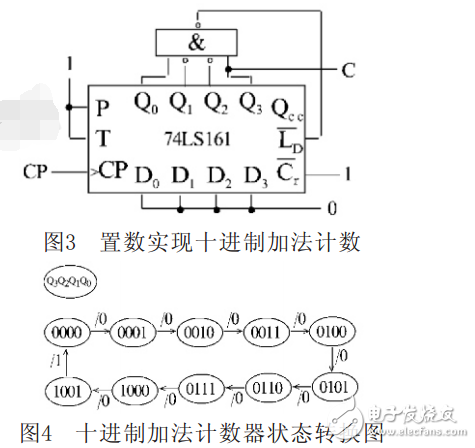

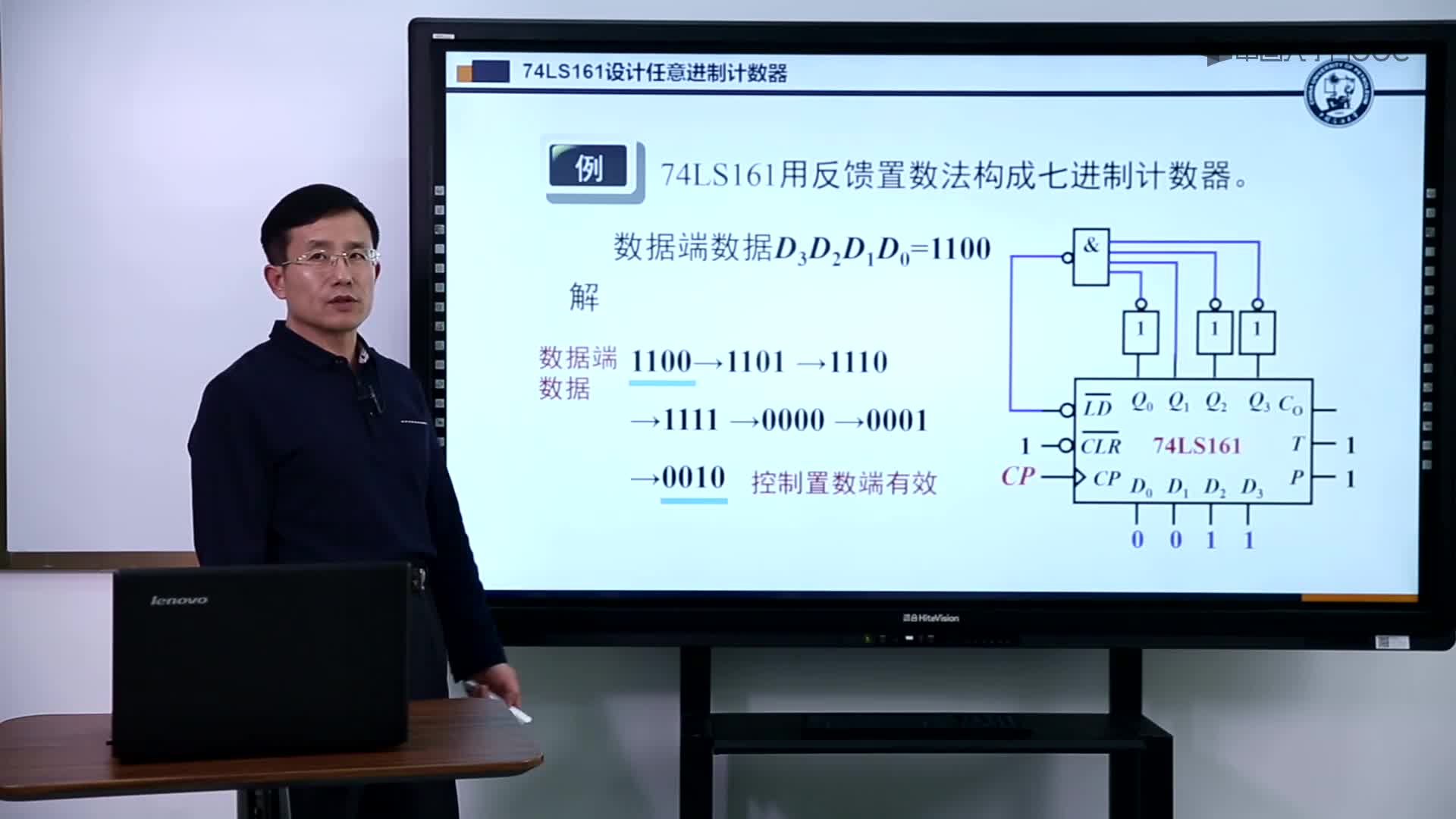

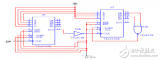

2)161的是同步置數置數端,可以用置數法實現十進制加法計數功能。161共有16個狀態,采用置數法實現十進制加法計數功能時只要跳過其中任意6個狀態就可以,方法有很多,這里僅舉一種。當Q3Q2Q1Q0=1001(即9)狀態時,通過譯碼電路給出低電平信號,將計數器置0回到0000狀態。電路圖和狀態轉換圖如圖3,圖4所示。

由于161的置數是同步式的,所以不存在異步置零法中因置零信號持續時間過短而可靠性不高的問題。

電子發燒友App

電子發燒友App

評論