基于DS12C887電子萬年歷設計方案

1、設計方案

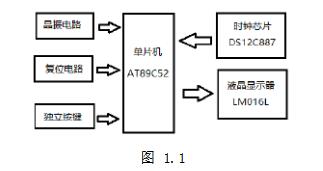

以單片機AT89C52為主控芯片,外圍采用時鐘芯片DS12C887,單片機P0口接DS12C887,P1.0口至P1.3口接按鍵,P1.4口至P1.7口分別接DS12C887的CS口、AS口、RW口、DS口。P2口接液晶顯示器LM016L的D0至D7口,P3.3口接DS12C887的IRQ口,P3.4口、P3.5口分別接LM016L的E口和RS口。

2、系統總體框圖

3、整體功能說明

本設計方案基于時鐘芯片DS12C887做萬年歷設計。當程序執行后,LCD顯示即時時間、年月日、星期、溫度。設置4個按鍵,S1:設置鍵S2:上調鍵;S3:下調鍵;S4:復位鍵。操作按鍵可以重新設置時間、星期、日期。

基于DS12C887電子萬年歷的制作

所需的元器件介紹

一、單片機AT89C52介紹

AT89C52是美國ATMEL公司生產的低電壓,高性能CMOS 8位單片機,片內含8k的可反復擦寫的只讀程序存儲器(PEROM)和256 bytes的隨機存取數據存儲器(RAM),器件采用ATMEL公司的高密度、非易失性存儲技術生產,與標準MCS-51指令系統及8052產品引腳兼容,片內置通用8位中央處理器(CPU)和Flash存儲單元,功能強大AT89C52單片機適合于許多較為復雜控制應用場合。引腳功能如圖2.1所示

AT89C52單片機功能特性概述

AT89C52提供以下標準功能:8K字節Flash閃速存儲器,256字節內部RAM, 32個I/O口線,3個16位定時/計數器,一個6向量兩級中斷結構,一個全雙工 串行通信口,片內振蕩器及時鐘電路。同時,AT89C52了降至0Hz的靜態邏輯操作,并支持兩種軟件可選的節電工作模式。空閑方式停止CPU的工作,但允許RAM,定時/計數器,串行通信口及中斷系統繼續工作。掉電方式保存RAM中的內容。但振蕩器停止工作并禁止其他所有部件工作直到下一個硬件復位。

AT89C52單片機主要引腳功能介紹

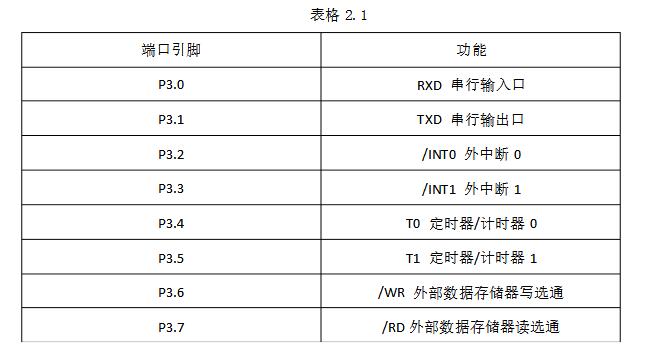

AT89S52單片機共有4個雙向的8位并行I/O端口(Port),分別記作P0-P3,共有32根口線,各口的每一位均由鎖存器、輸出驅動器和輸入緩沖器所組成。這四個口除了按字節尋址以外,還可以按位尋址。由于它們在結構上有一些差異,故各口的性質和功能有一些差異。

P0口:P0口是一組8位漏極開路型雙向I/O口,也即為地址/數據總線復用口。作為輸出口用時,每位能吸收電流的方式驅動8個TTL邏輯門電路,對端口P0寫“1”時,可作為高阻抗輸入端用。在訪問外部數據存儲器或程序存儲器時,這組口線分時轉換地址(低8位)和數據總線復用,在訪問期間激活內部上拉電阻。

P1口:P1是一個帶內部上拉電阻的8位雙向I/O口,P1的輸出緩沖級可驅動(吸收或輸出電流)4個TTL邏輯門電路。對端口寫“1”,通過內部的上拉電阻把端口拉到高電平,此時可作輸入口。作輸入口使用時,因為內部存在上拉電阻,某個引腳被外部信號拉低時會輸出一個電流。P1.0和P1.1還可分別作為定時/計數器2的外部計數輸入(P1.0/T2)和輸入(P1.1/T2EX)。

P2口:P2是一個帶有內部上拉電阻的位雙向I/O口,P2的輸出緩沖級可驅動(吸收或輸出電流)4個TTL邏輯門電路。對端口寫“1”,通過內部的上拉電阻把端口拉到高電平,此時可作輸入口。作輸入口使用時,因為內部存在上拉電阻,某個引腳被外部信號拉低時會輸出一個電流。

P3口:P3是一個帶有內部上拉電阻的位雙向I/O口,P3的輸出緩沖級可驅動(吸收或輸出電流)4個TTL邏輯門電路。對P3口寫入“1”時,它們被內部上拉電阻拉高并可作為輸入端口。此時,被外部拉低的P3口將用上拉電阻輸出電流。其最重要的用途是它的第二功能。其主要第二功能如表格2.1所示。

/EA/VPP:外部訪問允許。欲使CPU僅訪問外部程序存儲器,/EA端必須保持低電平(接地)。

XTAL1:振蕩器反相放大器及內部時鐘發生器的輸入端。 XTAL2:振蕩器反相放大器的輸出端。

二、時鐘日歷芯片DS12887

能夠自動產生年、月、日、時、分、秒等時間信息,芯片內部帶有鋰電池,外部掉電時,其內部時間信息能夠保持10年之久;有12小時制和24小時制兩種工作模式;時間的表示方法有兩種:二進制數表示和BCD碼表示。用戶可對DS12887進行編程以實現多種方波輸出,用戶可對其內部的三路中斷通過軟件進行屏蔽。 2.2.1 引腳說明

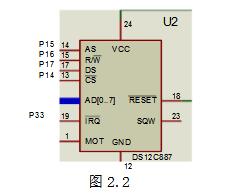

DS12C887引腳圖如圖2.2

1、Vcc:直流電源+5V輸入

當Vcc輸入為+5V時,用戶可以訪問DS12887內RAM中的數據,并可對其進行讀、寫操作;當Vcc的輸入小于+4.25V時,禁止用戶對內部RAM進行讀、寫操作,此時用戶不能正確獲取芯片內的時間信息;當Vcc的輸入小于+3V時,DS12887會自動將電源切換到內部自帶的鋰電池上,以保證內部的電路能夠正常工作

2、GND:地

3、MOT:總線模式選擇。當MOT接Vcc時選用Motorola總線模式,當MOT接GND時選用Intel總線模式。

4、SQW:方波輸出。當供電電壓Vcc大于4.25V時,SQW腳可進行方波輸出,此時用戶可以通過對控制寄存器編程來得到13種方波信號的輸出。

5、AD0~AD7:雙向地址/數據總線。

6、AS:地址有效輸入。

7、DS/RD:數據選通/讀允許。當MOT接Vcc時作為數據選通;當MOT接GND時,作為讀允許輸入。

8、R/W:讀/寫允許輸入。若MOT接Vcc,該引腳為高電平時讀操作,為低電平時寫操作;若MOT接GND,該引腳作為寫允許輸入。

9、CS:片選輸入。低電平有效。 10、IRQ:中斷請求輸出。低電平有效。

11、RESET:復位端。低電平有效,復位操作不影響時鐘日歷工作。

12、NC:空引腳。 2.2.2 存儲器分配與設置

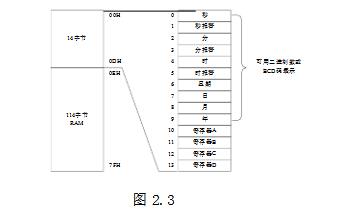

DS12887片內RAM與寄存器地址分配見圖2.3。

DS12887帶有128字節片內RAM:

1、10字節的時標寄存器:用來存儲時間信息,地址00H~09H。CPU可以通過讀取時標寄存器獲得時間與日歷值,也可以編程設置其初值,時標寄存器的值可以用二進制或BCD碼表示。4字節的控制寄存器:用來存儲控制信息,地址0AH~0DH。用戶可通過對控制寄存器編程實現從SQW引腳輸出多種不同頻率的方波,并可對其內部的三路中斷通過軟件進行屏蔽。114字節作為通用RAM供用戶使用,地址為0EH~7FH

2、UIP:更新周期標志。

當UIP=1時,表示芯片正處于或即將開始更新周期,在此期間不允許讀寫時標寄存器;當UIP=0時,表示沒有更新周期,此時可讀時標寄存器。

3、DV2~DV0:芯片內部振蕩器RTC控制位。當芯片復位后500ms開始第一個更新周期。將這3位設置成010,可使芯片以內置的32.768kHz的振蕩頻率工作。

4、RS3~RS0:周期中斷可編程方波輸出速率選擇位。

5、SET:允許更新周期位。可讀/寫,不受信號的影響。當SET=0時,芯片處于正常更新狀態;當SET=1時,芯片正常更新被禁止。

6、PIE、AIE、UIE:分別為周期中斷、鬧鐘中斷、更新周期結束中斷允許位。各位分別為“1”時允許發出相應的中斷,由端輸出。其中,UIE位在復位或設置SET為1時清零。

7、SQWE:方波輸出允許位。當SQWE=1,按寄存器A輸出速率選擇位所確定的頻率輸出方波;當SQWE=0,SQW腳保持低電平。

8、DM:時標寄存器格式選擇位。DM=0,為BCD碼;DM=1,為二進制碼。

9、24/12:24小時或12小時模式設置位。24/12=1,選擇24小時工作模式;24/12=0,選擇12小時工作模式。

10、DSE:夏令時允許標志位。當DSE=1時,夏時制設置有效。在四月的第一個星期日的1:59:59 AM,調到3:00:00 AM;在十月的最后一個星期日的1:59:59 AM,調到1:00:00 AM;當DSE=0無效。寄存器C 為中斷標志位寄存器。

11、IRQF:中斷申請標志位。

該位邏輯表達式為:IRQF = PF · PIE+AF · AIE+UF · UIE。當IRQF=1時,IRQ引腳將輸出低電平。PF、AF、UF:這三位分別為周期中斷、鬧鐘中斷、更新周期結束中斷標志位。只要滿足各中斷的條件,相應的中斷標志位將置“1”。 10、 VRT:芯片內部RAM與寄存器內容有效標志位。該位為“1”時,表示芯片內部RAM和寄存器內容有效。讀該寄存器后,該位將自動置“1”。

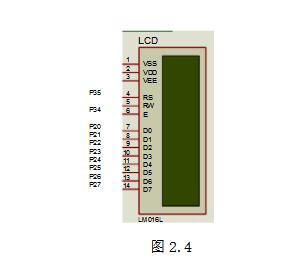

三、液晶顯示器LM016L

LM016L引腳 第1腳:VSS為地電源。

第2腳:VDD接5V正電源。

第3腳:VL為液晶顯示器對比度調整端,接正電源時對比度最弱,接地時對比度最高,對比度過高時會產生“鬼影”,使用時可以通過一個10K的電位器調整對比度。

第4腳:RS為寄存器選擇,高電平時選擇數據寄存器、低電平時選擇指令寄存器。

第5腳:R/W為讀寫信號線,高電平時進行讀操作,低電平時進行寫操作。當RS和R/W共同為低電平時可以寫入指令或者顯示地址,當RS為低電平R/W為高電平時可以讀忙信號,當RS為高電平R/W為低電平時可以寫入數據。

第6腳:E端為使能端,當E端由高電平跳變成低電平時,液晶模塊執行命令。

第7~14腳:D0~D7為8位雙向數據線。

第15腳:背光源正極。

第16腳:背光源負極

引腳圖如圖2.4

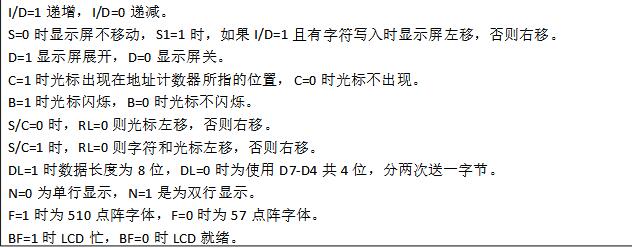

控制命令如表格2.2

電子發燒友App

電子發燒友App

評論