ad630應用電路:鎖相放大電路

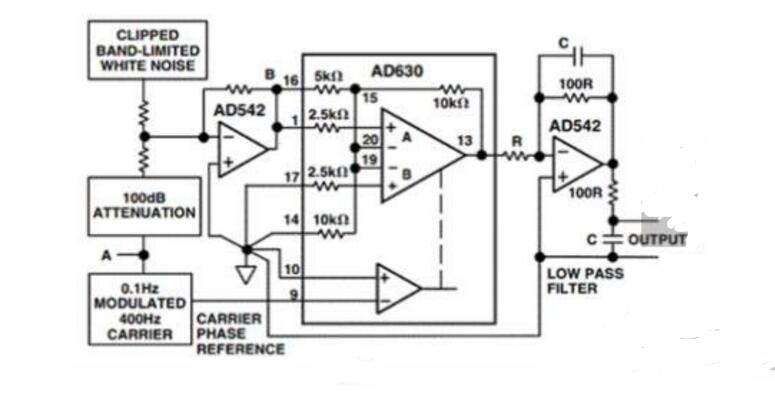

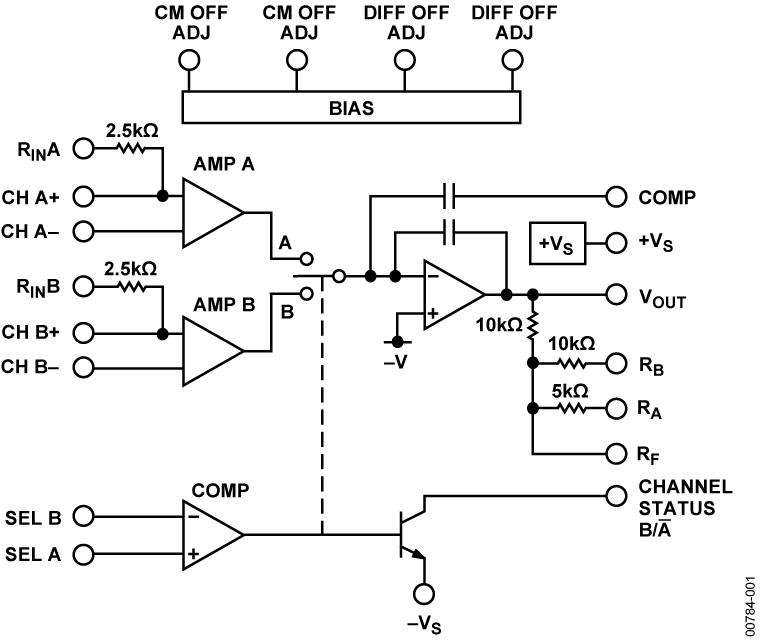

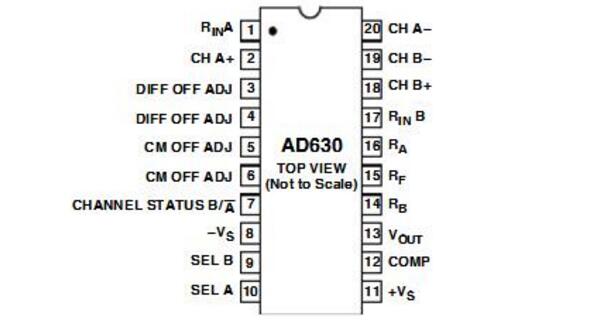

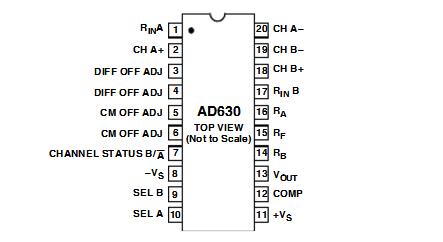

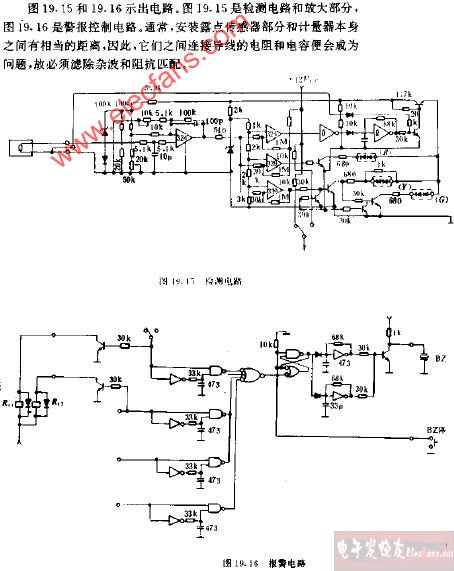

AD630的鎖相放大電路示意圖如下圖所示。

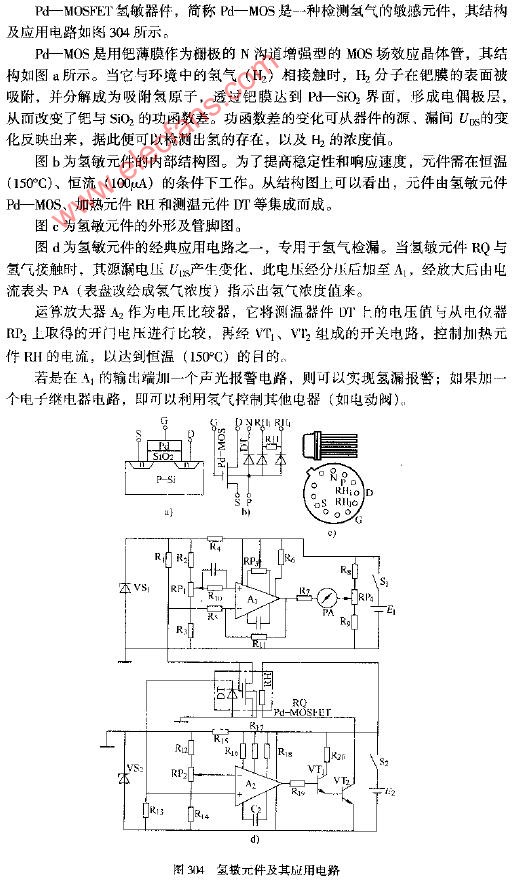

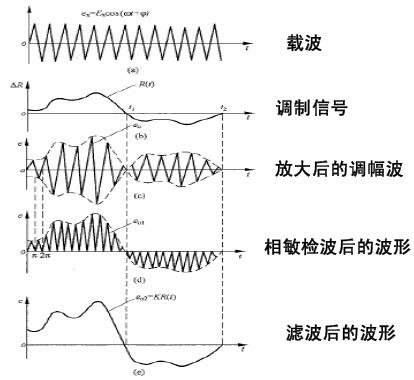

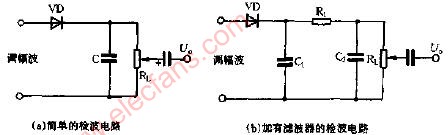

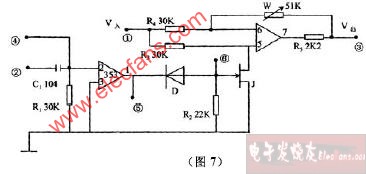

A點的波形為被檢測信號與載波調制后的雙邊已調制波形,B點為雙邊已調制波形和噪聲疊加后的波形,AD630的第9腳接載波信號,方波、正弦波都可行,相當與一個參考相位。AD630的輸出接一個積分電路及一個低通濾波器,以達到的信號的完美恢復。

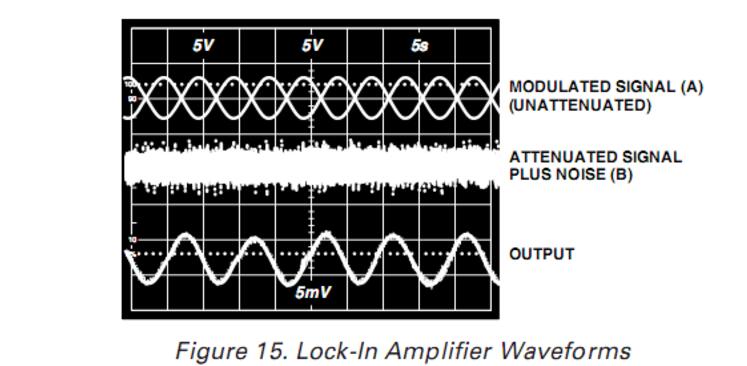

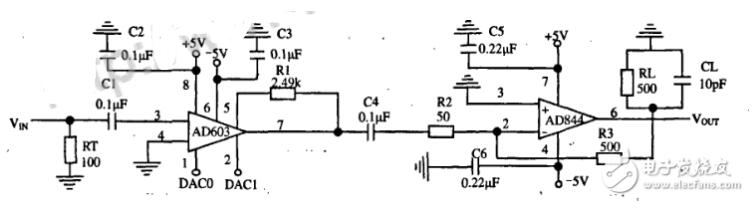

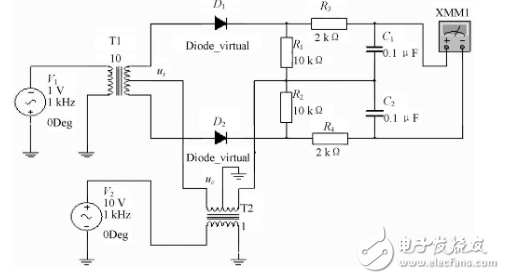

測試信號400Hz的載波調制0.1Hz的正弦波產生,正弦調制波形用于清楚的說明,信號通過類似于圖9b的電路產生,顯示在如圖15上部的軌跡。他被衰減10萬次,規范化求和放大器的輸出B。噪音信號通過求和放大器加入到調制信號中,這個信號是簡單的帶限裁剪的白噪聲。圖15的中間軌跡顯示了衰減的信號和噪音的疊加。混合信號使用相位信息同步解調(相位信息來自于調制器),結果為使用2極點的簡單濾波器進行低通濾波,濾波器對輸出端提供100增益,恢復后的信號在圖15的下部。

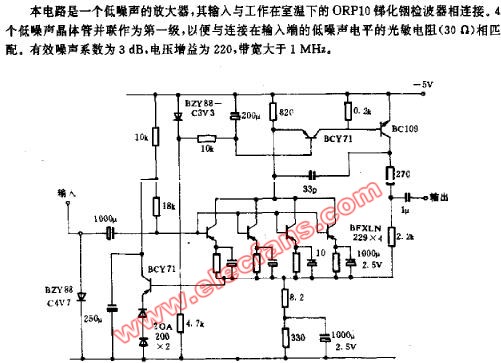

上述這個混合的信號和干擾噪音類似于要求進行檢測的鎖定放大的信號。AD630精確的輸入性能提供了大于100dB的信號范圍,并且其動態響應允許其用于載波頻率比實例中的大于兩個或以上的數量級。一個更復雜的低通輸出濾波器,將有助于抵抗更寬的帶寬干擾。

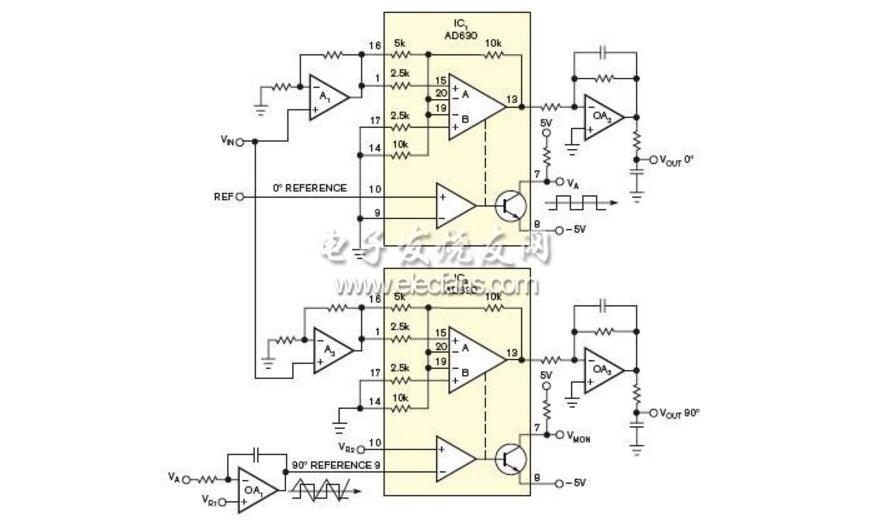

ad630應用電路:相敏檢波電路

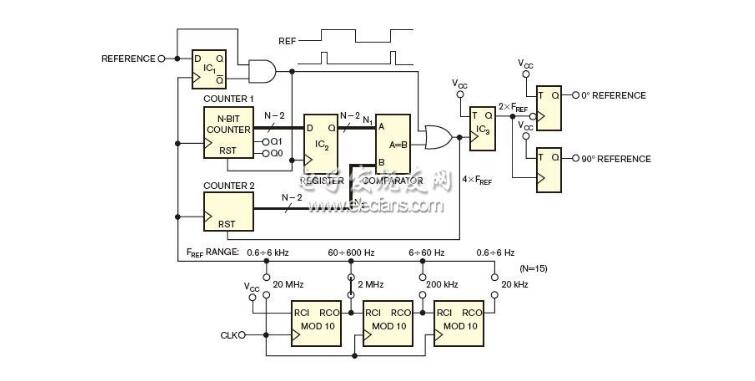

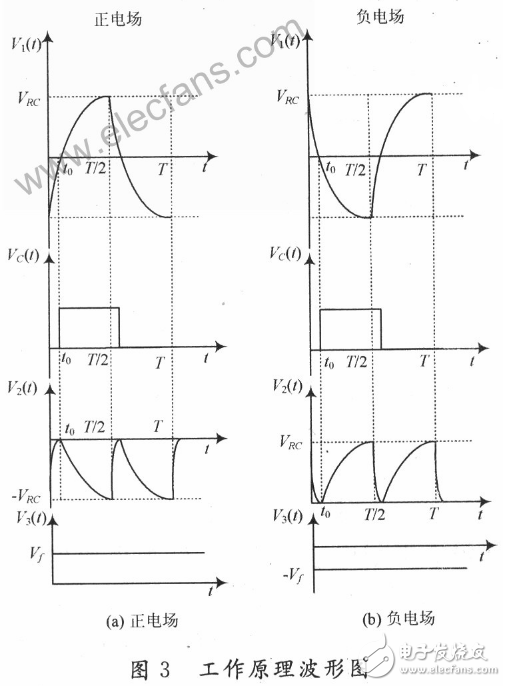

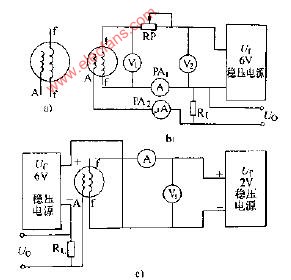

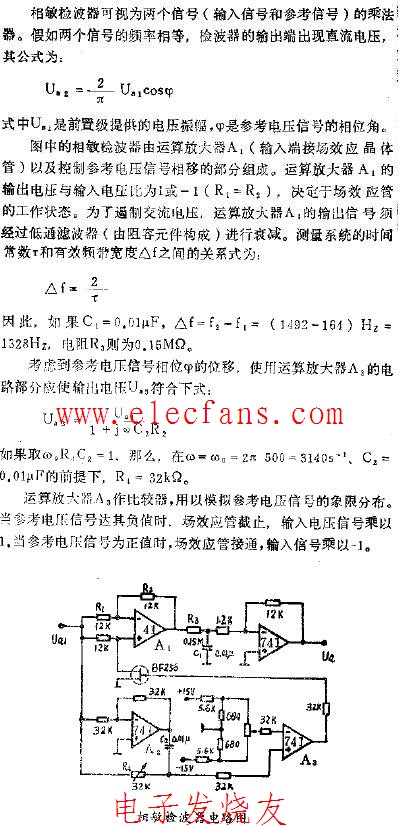

圖2描繪了一條全數字電路,你可在小型CPLD中實施該電路,來產生圖1中的0和90?基準信號。1號計數器以數字時鐘脈沖的數量N的形式來測量基準信號時間,其中的基準時間可能不同于50%。在基準信號的每個正前沿,該計數器在N1=1處收到一條預設命令。D型雙穩態多諧振蕩器IC1產生這類脈沖。

圖1,OA1把雙極VA信號積分,并創建三角波。VR1和VR2獲得關于VA的90。相移基準電壓。

圖2,你可在小型CPLD中實現這條全數字電路。

當基準時間超過N/4整數值的大約四倍時,就會缺少最后的EQ信號。為了克服這個問題,RST脈沖和EQ脈沖的“或”組合會在每個基準時間周期內產生四條幾乎等距的命令。N/4整數除法是邏輯右移N1的兩位,在最后的脈沖位置上產生最大誤差3。T型雙穩態多諧振蕩器IC3產生一個信號,頻率為基準信號的兩倍。這樣,準確度等于3/N1。

為使準確度至少能與AD630相比,1號計數器的N1輸出將為最高值。但是,如果你希望N1達到較高值,那么對于給定的數字時鐘頻率,位數的增加會使最大基準頻率下降。

電子發燒友App

電子發燒友App

評論