74ls160應用電路圖(一)

數字鐘是計數電路的一種典型應用,其構成原理框圖如下圖所示。它主要由三部分組成:

(1)秒脈沖發生電路

它由32768Hz的石英晶體振蕩器和若干級分頻電路構成,振蕩器產生32768Hz的方波,由于使用了晶體,振蕩頻率準確且穩定,經過216=65536分頻后,再經過2倍頻,得到秒脈沖信號,該秒脈沖信號經過控制門進入秒計數器進行計數。

(2)時間校準電路

時間調整由3個開關AN1、AN2、AN3以及3個R-S觸發器構成。當3個開關都撥到右邊時,R-S觸發器的輸出Q1、Q2、Q3都為1,因此控制門的3個右邊門開啟,秒、分、時脈沖可以正常進入相應計數器進行計數。當某開關撥到左邊時,R-S觸發器翻轉,例如當“秒調整”開關撥到左邊,Q1-0、,控制門的右門關、左門開,秒脈沖不能通過,而0.5s的脈沖信號卻可以進入秒計數器實現“秒調整”。分、時的調校原理與此相同,使用R—S觸發器的目的是為了消除開關抖動產生的影響。

(3)時、分、秒計數電路

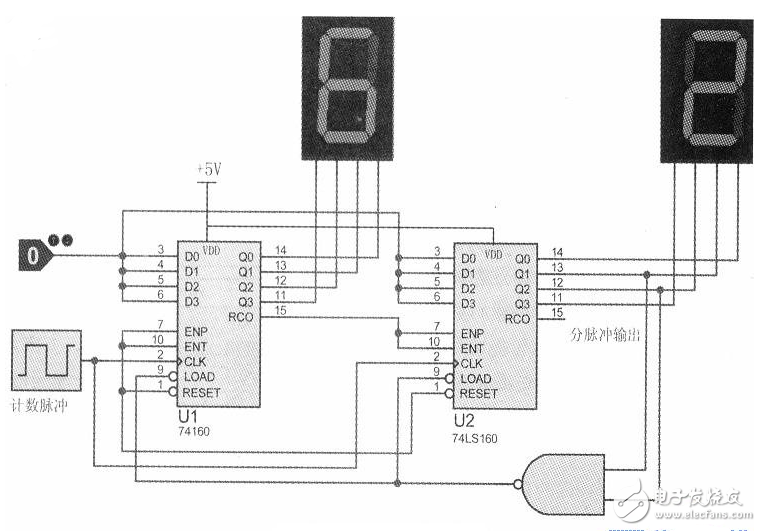

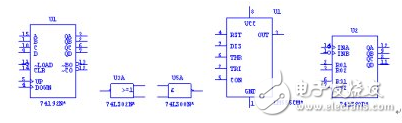

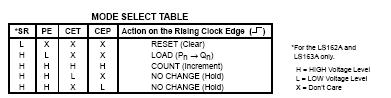

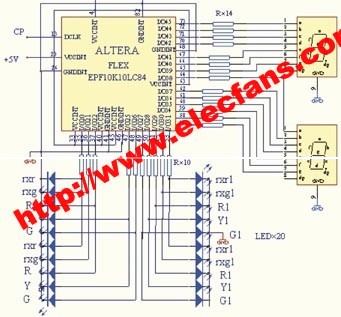

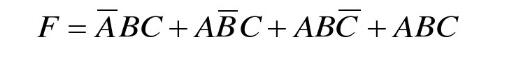

采用兩片74LS160按下圖所示連接,可以構成作60分頻計數,用于數字鐘中的秒計數器。

標準秒脈沖經過控制門進入秒計數器,并顯示其計數值,當計數滿60時得到一個進位“分”脈沖,同時秒計數器自動清零。“分”脈沖經控制門送入“分計數器”又作60分頻計數,當計數滿后得到進位“時”脈沖。“時”脈沖再經控制門送入“時計數器”計數。“分計數器”與“時計數器”的計數、復零和顯示原理與“秒計數器”相同,可以自行設計。

74ls160應用電路圖(二)

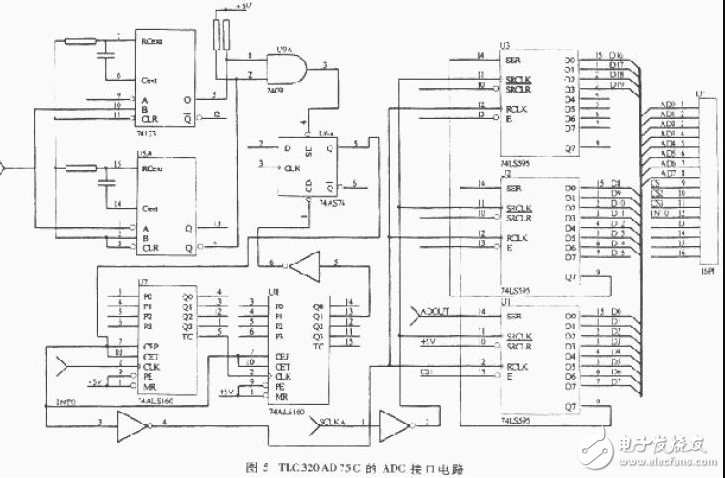

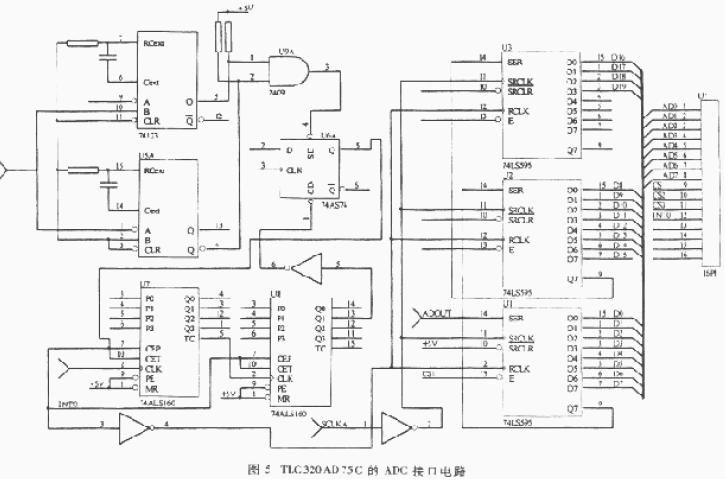

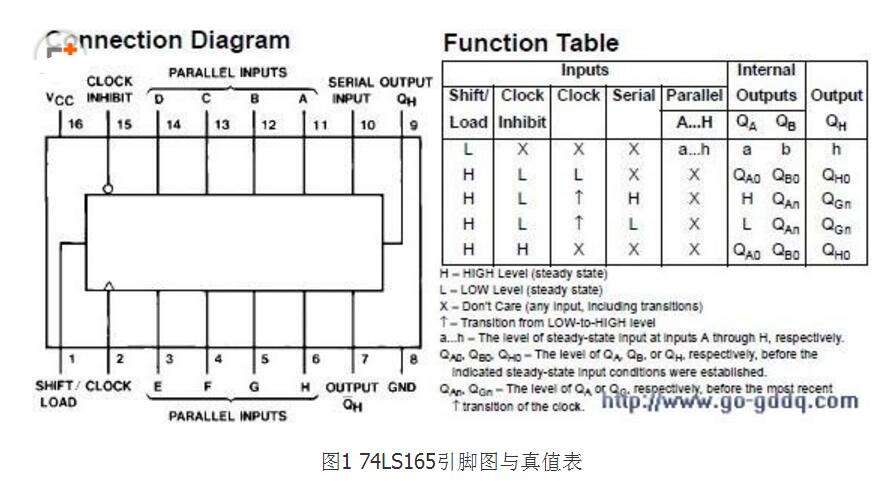

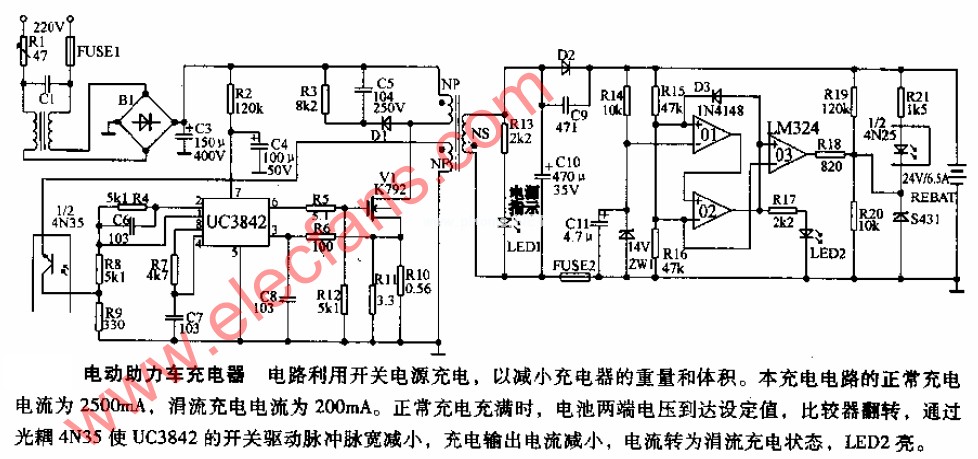

下圖是TLC320AD75C 的ADC 與MCS51 接口電路,DAC 接口電路是上述電路的逆過程,只要將8位輸出鎖存移位寄存器(三態、串入并出)74LS595 改成8位輸入鎖存移位寄存器74LS597(三態、并入串出)即可,此處不再詳述。圖5與圖3的畫法一樣,鑒于篇幅的限制,省略掉了一些電路細節,讀者應用本文中的電路時應補上。下面簡單講述一下圖5所示電路的工作過程。根據圖4串行接口時序,要求利用LRCKA 和SCLKA 生成圖4(d)所示的脈沖。在該脈沖的高電平期間20 位串行數據送到由三片74LS595 級聯而成的串入并出接口電路中;在脈沖的下降沿將74LS595 中移位寄存器中的數據傳輸到鎖存器;在脈沖的低電平期間發中斷到MCS51 的INTO,MCS51 依次發出三個片選信號,讀走該20 位數據,從而完成一個聲道的采集工作。因此如何產生圖4(d)所示的脈沖是本電路的核心問題。在圖5所示電路中,74LS123 捕捉到的LRCKA 上升沿和下降沿通過線與的方式生成圖4(e)形式的極窄脈沖。在該脈沖的低電平期間置位74LS74;兩片74LS160 接成20 進制的計數器,在74LS74 輸出高電平到來時對SCLKA 進行計數,當計滿20 個脈沖時輸出一高電平脈沖,該脈沖經一非門倒相去74LS74 的復位端。74LS74 在上述的置位與復位作用下即產生圖4(f)所示的脈沖,同時在該脈沖的低電平期間還要去清除計數器,停止計數器工作,直至該脈沖的下一個高電平到來。要指出的是圖4(f)所示脈沖比圖4(d)所示的脈沖有一延遲,但只要該延遲時間小于TSCLKA/2,即圖4(f)所示脈沖的上升沿比轉換開始后SCLKA 的第一個上升沿早,同步計數器就可正確計數,不會漏掉1位串行數據。

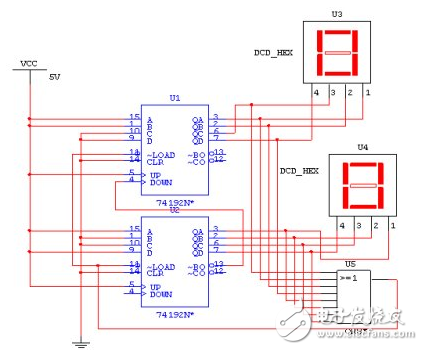

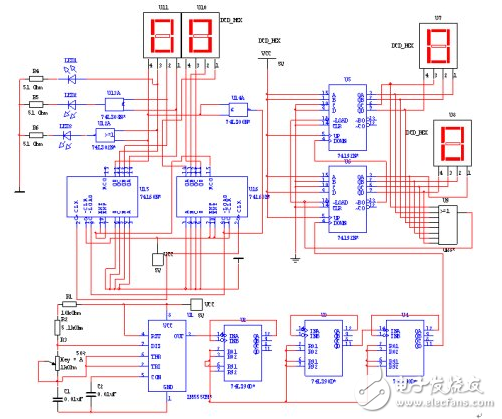

74ls160應用電路圖(三)

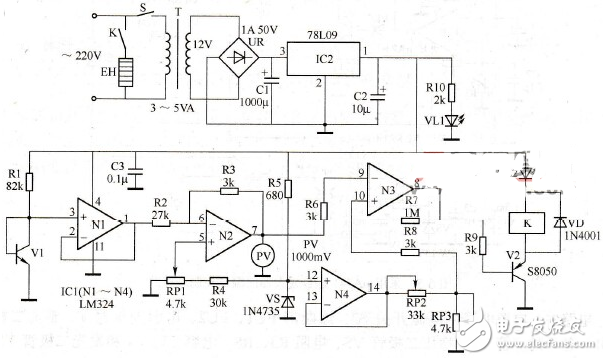

設計原理和工作電路

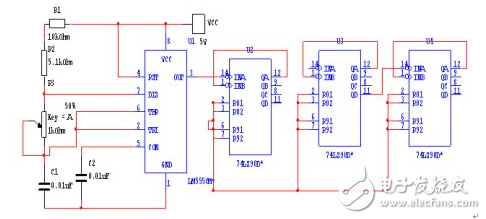

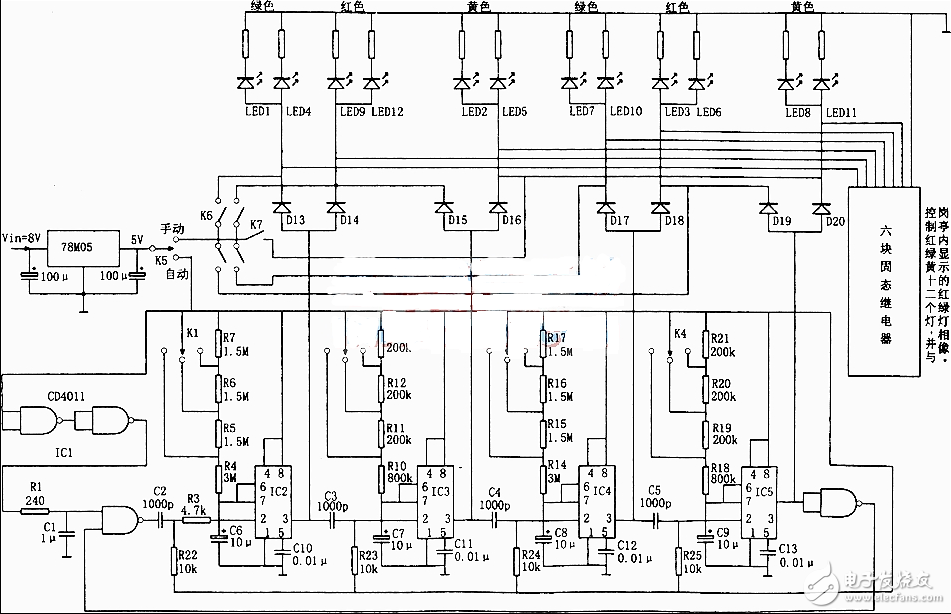

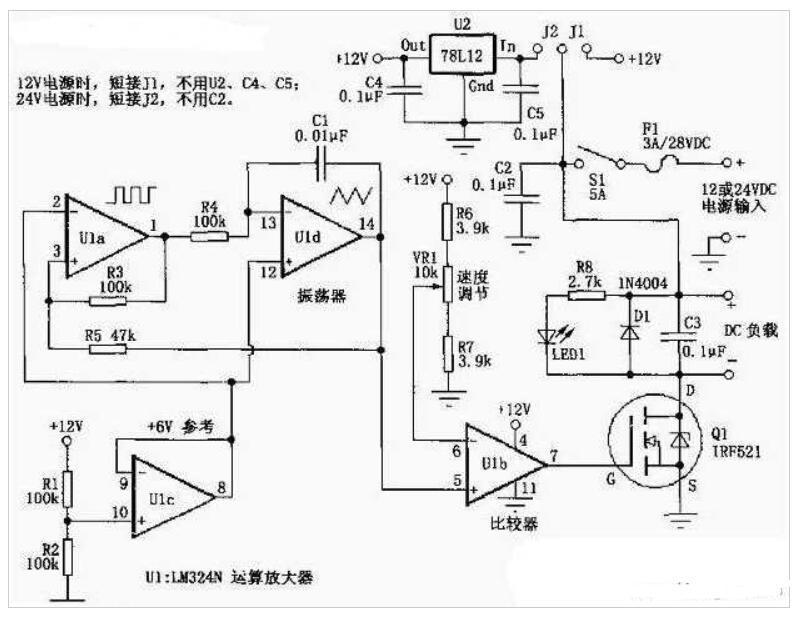

交通燈的控制電路主要由555定時器、分頻電路產生出1HZ的脈沖,兩個74LS160、與門、與非門、或非門組成的紅綠燈轉換電路,以及由74LS192設計出的倒計時顯示器等組成。

秒脈沖的產生

電路圖如下:

本電路由555定時器產生1KHZ的脈沖,再由分頻電路產生出1HZ脈沖。

紅綠燈的轉換

電路圖如下:

本電路是由兩個74LS160組成的80進制計數器,每到第40個脈沖時轉換紅綠燈,在每次紅綠燈轉換的最后10秒,黃燈也一起亮,達到提示的作用。

倒計時顯示

電路圖如下:

它是一個由74LS192可逆計數器組成的40倒計時到0的減法計數器,實現紅綠燈轉換時的顯示。由于時間緊迫,在實驗時未能調到正常工作狀態。

交通燈控制電路總圖:

實驗器材

(1)74LS90N(2)74LS00N(3)74LS47(4)5.1KR(5)10KR(6)36KR(7)51歐R(8)LM555CM(9)DCDHEX(10)LED(紅黃綠)

元器件功能

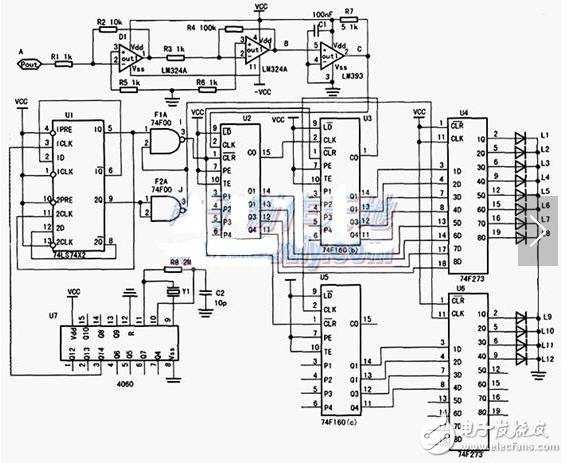

74ls160應用電路圖(四)

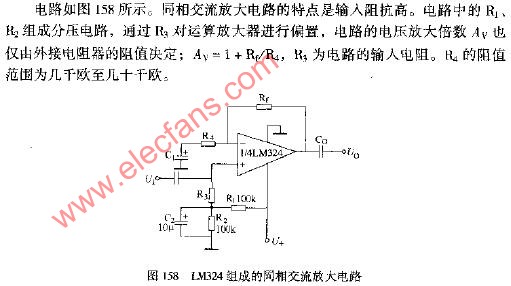

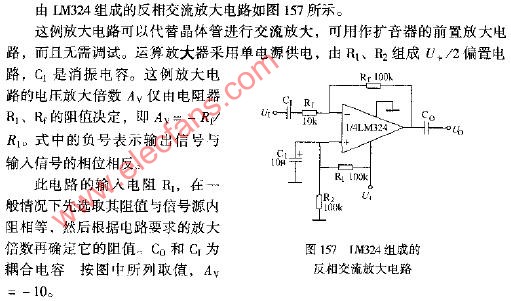

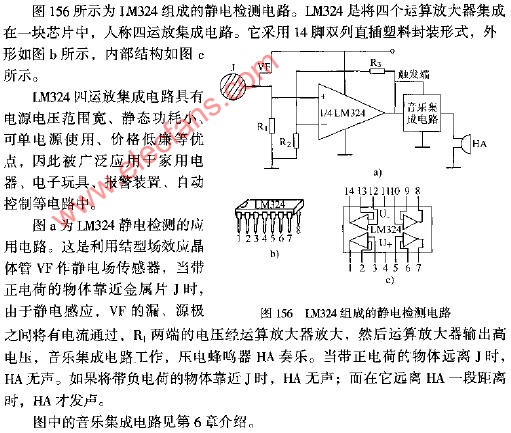

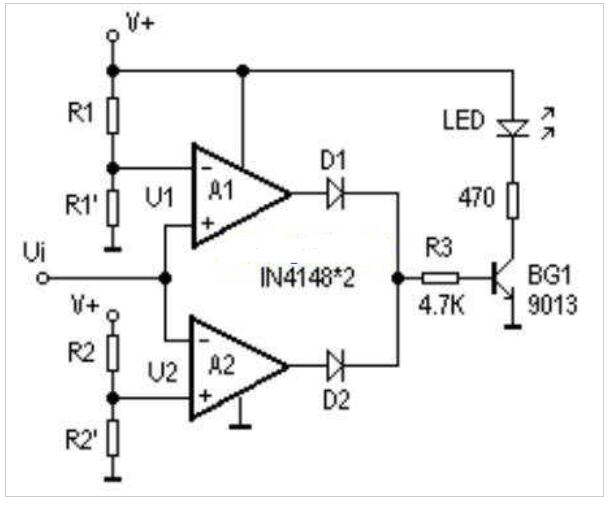

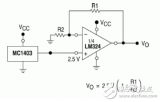

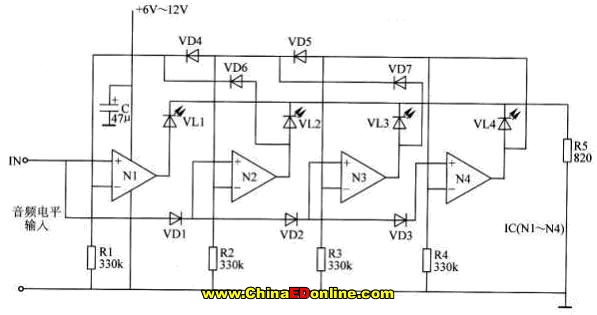

系統電路如下圖所示。

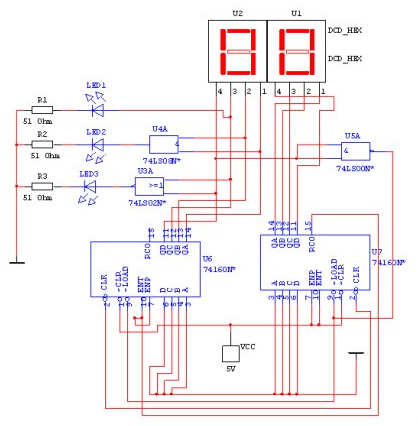

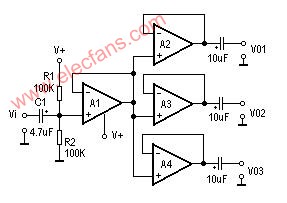

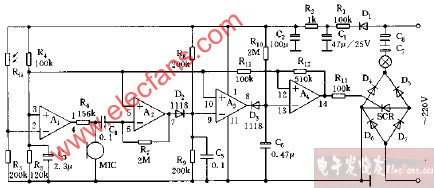

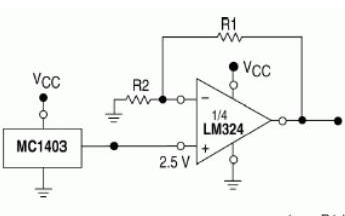

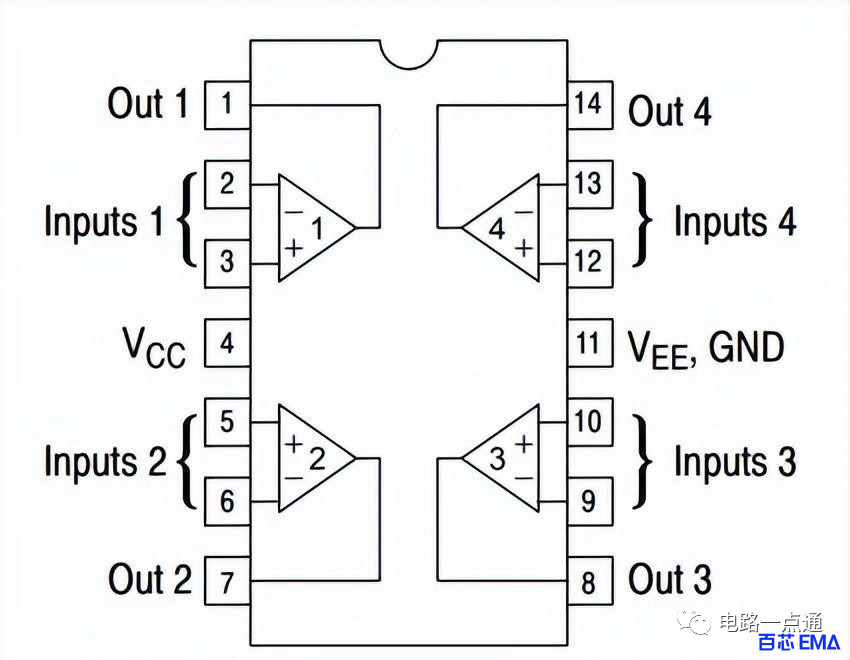

(1) 放大電路:放大電路部分主要由一塊LM324集成運放及外圍元件組成。本放大電路采用兩級放大,第一級信號的增益為20dB,第二級的信號增益為 40dB,兩級的放大倍數為1000倍,其頻率的帶寬為0~5kHz。采用多級放大可以提高的放大電路的通頻帶,如果被測的信號頻率較高。可以采用多級放 大來提高通頻帶,根據實際情況而定,由于本電路的測頻范圍低,對通頻帶不做太多的要求。圖2中,A端為被測信號的輸入端。B端為放大電路的輸出端,接整形 電路的輸入。

(2)整形電路:整形電路的主要作用是將第一部分放大的交變信號整形為數字信號(即幅度為5V的方波信號),其電路主要由比較器組成,該電路中我們選用LM393比較器,B端為整形電路輸入端,C為整形電路的輸出端接E端。

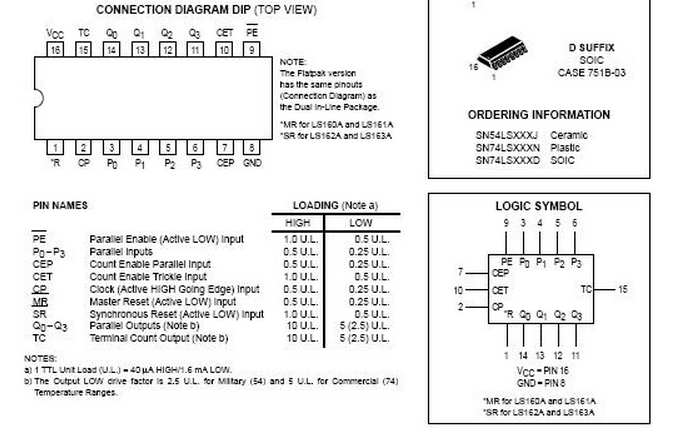

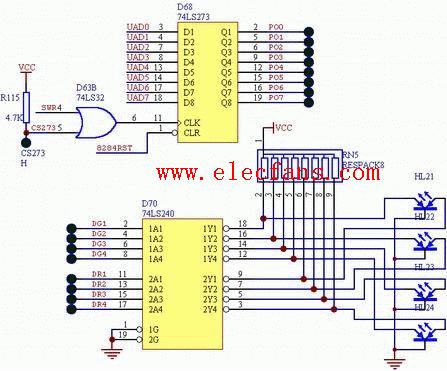

(3)計數電路:計數電路部分我們選用3片十進制加法計數器74LS160的級聯來實現0-999Hz的頻率顯示,74LS160為可預置的十進制同步計數器,利用其級聯,可以構成任意進制的計數器。

74LS160(a) 的2腳為脈沖信號的輸入端,1腳清零端。74LS160(a)的CO進位端接74LSl60(b)的CLK脈;中輸入端,74LS160(b)的進位端接 74LS160(c)的CLK脈沖輸入端,三塊計數器的PE、TE及LD端接電源.使計數器工作在計數的狀態,CLR端接時基電路,由時基電路來控制計數 與清零。

(4)顯示電路:顯示電路部分主要由二塊74LS273鎖存器和12個紅色發光二極管組成,74LS273是8位數據/地址鎖存器。他是 一種帶清除功能的8D觸發器,主要實現對計數電路的輸出信號進行鎖存,由于計數器的頻率較快。采用的是動態顯示,我們為了顯示的穩定,便于觀察,所以在計 數器的輸出端進行鎖存。該鎖存器的鎖存信號由時基電路來提供,且當1腳為高電平時,11(CLK)腳是鎖存控制端,并且是上升沿觸發鎖存,當11腳有一個 上升沿,立即鎖存輸入腳3、4、7、8、13、14、17、18的數據,并且立即呈現在輸出腳2(Q0)、5(Q1)、6(Q2)、9(Q3)、 12(Q4)、15(Q5)、16(Q6)、19(Q7)上。74LS273的CLR端接高電平,使其工作在不清零狀態。

(5)時基信號產生電 路:該電路的主要作用是產生O.5Hz的時基信號(即周期為2秒,脈寬為1秒的閘門信號)為鎖存器提供鎖存信號和為計數電路提供計數閘門信號,實現頻率計 數與顯示。時基信號產生電路由一個頻率為3.2768MHz的晶振和一塊CD4060分頻器以及外圍元件夠成。CD4060(IC)是一種帶有振蕩器的 14級分頻器電路。用作振蕩器時需外接R、C元件或石英晶體和電容器。內部包含兩個非門和14級2分頻電路,它所產生的信號頻率為32768Hz,經14 級兩二分頻后,得到一個2Hz的脈沖信號。下圖H端為2Hz信號的輸出端。

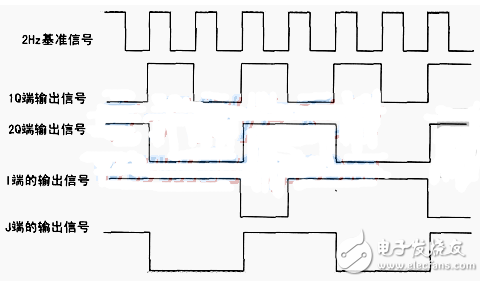

(6)計數器與鎖存器控制電路該部分電路主要是控制計數電路的清零、計數與鎖存電路的鎖存顯示。該電路的核心器件是一塊 D觸發器74L.S74與一塊與非門74LS00組成。H為2Hz方波信號(即周期為0.5s,時基電路產生)的輸入端I、J為控制信號的輸出端,分別接 計數器的清零端與鎖存電路的CLK時鐘端,H、I、J端的信號時序如下圖所示。

基準信號經過D觸發器分頻后便獲得1Q和2Q的方波信號,經由兩個與非即可得到l端和J端的方波信號。當l端的信號在高電平時計數器工作在計數狀態,低電平時對計數器清零。當l端的信號處于下降沿的時候,此時J端的信號處于上升沿。

該上升沿信號使鎖存器開始工作,直到下一個上升沿的到來.這樣便實現輸入信號的計數與鎖存。

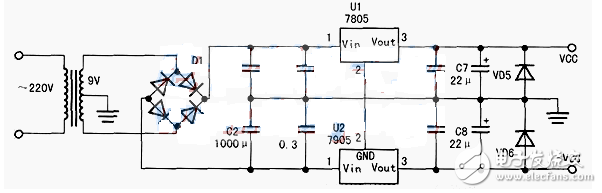

(7)電源電路:該電路的整體供電需要雙5V,因此我們可以設計一個簡單的雙電源供電電路。電路原理圖如下圖所示。

電子發燒友App

電子發燒友App

評論